Н.А. ТИТОВИЧ<sup>1</sup>, В.Н. ТЕСЛЮК<sup>1</sup>

## ИССЛЕДОВАНИЕ ВЛИЯНИЯ ЭЛЕКТРОМАГНИТНЫХ ПОМЕХ НА РАБОТОСПОСОБНОСТЬ МНОГОВЫХОДОВЫХ МИКРОСХЕМ

<sup>1</sup>Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники», г. Минск, Республика Беларусь

Одним из наиболее эффективных методов повышения помехоустойчивости РЭА является учет при проектировании информации о восприимчивости к воздействию ЭМП её элементной базы, в особенности полупроводниковых элементов и интегральных микросхем (ИМС). Путем выбора более устойчивых элементов, рациональной защиты их наиболее уязвимых цепей можно значительно снизить затраты на обеспечение ЭМС, уменьшить габариты и вес аппаратуры. В связи с этим при проведении исследований необходимо расширить номенклатуру ИМС и доработать приборы и методики оценки восприимчивости.

Проведены исследования влияние гармонических ВЧ помех с частотой 100 - 300 МГц на работоспособность многовыходовых схем, в частности двоичного счетчика ИЕ5. При проведении исследований использовалось устройство, описанное в [1]. Осуществлялся одновременный контроль сигналов на всех четырех выходах эталонной и исследуемой микросхем серии.

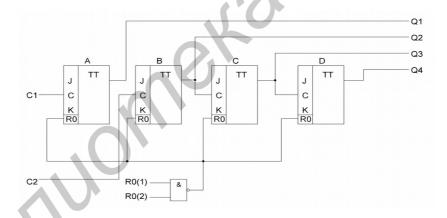

Логическая структура микросхемы ИЕ5 приведена на рис.1. Помеховые сигналы подавались последовательно на вход С1, выход Q4, шину питания. Контролировались изменения выходных сигналов на выходах Q1 — Q4 исследуемой (ИИС) по отношению к аналогичным сигналам эталонной (ЭИС) микросхемы под действием ЭМП, воздействующей на различные выводы.

Рисунок 1 – Логическая структура микросхемы ИЕ5

При воздействии помехового сигнала на вход С1 происходит нарушение в работе первого ЈК-триггера (А), который начинает работать как инвертор входного сигнала, происходят нарушения в работе последующих триггеров, коэффициент счета четырехразрядного двоичного счетчика уменьшается на два. При воздействии ЭМП на выход нарушения работоспособности происходят по причине сбоя в работе четвертого ЈК-триггера (D), на выходе Q4 устанавливается постоянный уровень логического нуля.

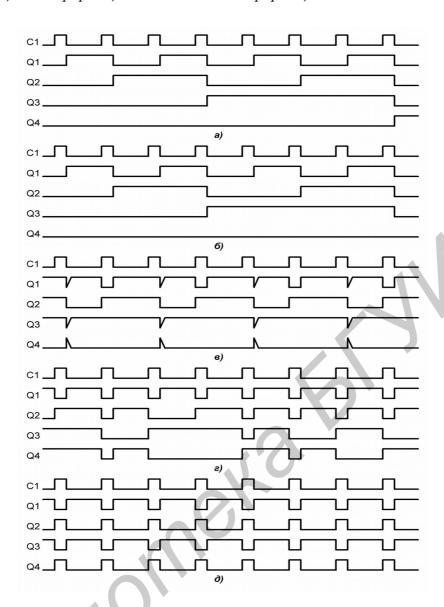

При подаче помехового сигнала на шину питания сначала отказывает триггер D (рис.2,б). Состояния выходов Q1, Q2, Q3 при этом не нарушаются. При увеличении помехового сигнала происходят сбои по всем остальным выходам по отношению к состоянию аналогичных выводов ЭИС. Однако, как видно из рис.2,в, отказы происходят только в работе триггеров A и C. Алгоритм работы триггера В не нарушается. И только при дальнейшем возрастании уровня ЭМП триггер В сбивается (рис.2,г). В конечном итоге все четыре триггера работают как инверторы (рис.2,д). Таким образом, наиболее восприимчивым к действию ВЧ помех оказался триггер D, а самым устойчивым - триггер В.

Рисунок 2 — Изменение выходных сигналов двоичного счетчика K155ИЕ5 под действием помехи, поступающей на шину питания

Таким образом, с целью повышения достоверности результатов оценки восприимчивости многовыходовых микросхем целесообразно осуществлять одновременный контроль состояния всех выходов. Это позволит выявить наиболее уязвимые элементы и цепи ИМС и учитывать это при разработке мер защиты и при построении цифровых схем с более высокой алгоритмической устойчивостью. Так, например, при определенных условиях для деления на 2 целесообразнее использовать более устойчивый триггер В микросхемы ИЕ5 вместо триггера А. Под действием ЭМП изменяются динамические параметры ИМС, а именно время задержки распространения сигнала. Наиболее уязвимыми являются те элементы ИМС, которые непосредственно связаны с их выводами, например, входом С1 (вывод 14) или выходом Q4 (11). Изменение времени задержки элементов ведет к возникновению состязаний сигналов, что может привести к неалгоритмическим переходам и сбоям в их работе.

## ЛИТЕРАТУРА

1. Патент RU 2069865, кл. G 01 R 31/28, 25.02.1991. Устройство для контроля параметров цифровых интегральных схем при воздействии электромагнитных помех/ Н.А.Титович, Е.А.Буевич (ВҮ). –Опубл.27.11.1996, бюл.№33.