## Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

Кафедра электронных вычислительных машин

## И.П. Кобяк

## ПРОЦЕССОРЫ КОМПЬЮТЕРНЫХ СИСТЕМ. СИНТЕЗ ОПЕРАЦИОННЫХ АВТОМАТОВ

## Методическое пособие

по курсовому и дипломному проектированию по ТиП ЭВМ и СиФО ЭВМ для студентов специальности 40 02 01 «Вычислительные машины, системы и сети» дневной формы обучения

# Рецент: доцент кафедры ЭВМ БГУИР, канд. техн. наук Ю.А. Луцик

#### Кобяк И.П.

К 55 Процессоры компьютерных систем. Синтез операционных автоматов: Метод. пособие по курсовому и дипломному проектированию по ТиП ЭВМ и СиФО ЭВМ для студентов специальности 40 02 01 «Вычислительные машины, системы и сети» дневной формы обучения / И.П. Кобяк. – Мн.: БГУИР, 2003. – 83 с.: ил.

ISBN 985-444-470-8.

Методическое пособие предназначено для ознакомления студентов с принципами проектирования операционных автоматов, а также с системными вопросами организации процессоров и блоков обработки данных. В пособии рассматриваются МПК К1804 и принципы использования комплекта при построении БОД, вопросы синтеза операционных автоматов и примеры применения методик для построения конкретных устройств. Представленные материалы могут быть использованы студентами для самостоятельного выполнения курсовых и дипломных проектов, а также для подготовки к экзамену по профилирующей специальности.

УДК 681.3 (075.8) ББК 32.973-04 я 73

#### 1. ОСНОВНЫЕ ПОЛОЖЕНИЯ

#### 1.1. Принцип действия ЭВМ

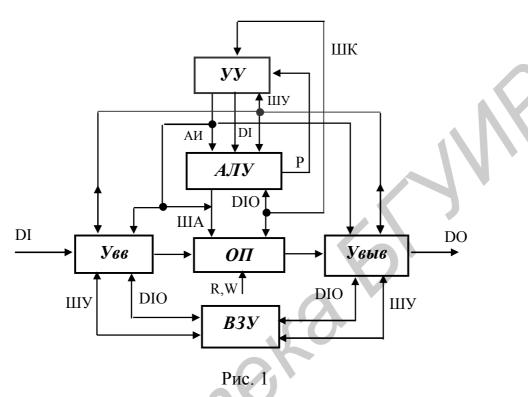

Классическая структура компьютера содержит в своем составе следующие блоки:

Структурные компоненты приведенной системы имеют следующее функциональное назначение.

Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций над числами, представленными в формате с ПЗ или ФЗ. Кроме данных в АЛУ могут обрабатываться адреса (адресная информация), команды (например, преобразование форматов), признаки результатов и другая двоичная информация.

Устройство управления (УУ) предназначено для автоматического управления вычислительным процессом путем посылки всем блока компьютера сигналов, предписывающих те или иные действия. В частности, УУ всегда указывает на:

- 1) источники информации для АЛУ;

- 2) функцию, выполняемую АЛУ;

3) приемник результатов, полученных при обработке данных.

ОП и ВЗУ – это память ЭВМ – предназначена для хранения информации, поступающей в компьютер извне, информации, выводимой на внешние носители (печать, монитор и т. д.). Эти блоки также предназначены для хранения программ, результатов промежуточных расчетов и другой машинной информации.

Оперативная память (ОП) состоит из определенного число ячеек, каждая из которых предназначена для хранения машинного слова. Основными характеристиками ОП считают время обращения и емкость памяти. При этом под временем обращения понимают время, необходимое для записи или считывания единицы информации из любой ячейки.

Устройство ввода (Увв) обеспечивает считывание информации с внешних носителей и представление ее в форме электрических сигналов.

Устройство вывода (Увыв) преобразует кодовую информацию, поступающую из памяти или других блоков машины, в форму, необходимую для обмена с внешней средой.

На рис.1 изображены следующие шины: DIO — двунаправленная шина данных, ШУ — шина управления, ША — шина адреса, DI — входные данные, DO — выходные данные, АИ — адресная информация, R, W — сигналы чтения\записи.

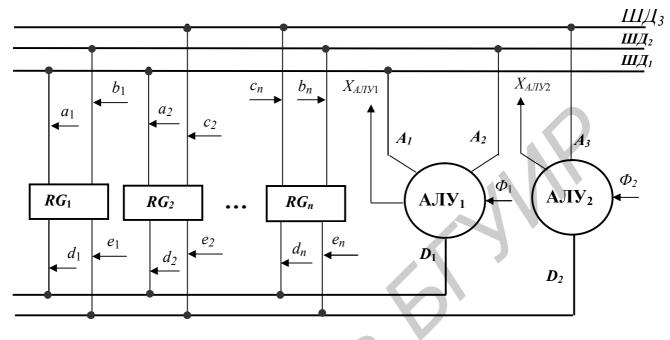

Другой вариант схемы предполагает представление компьютера в виде трехшинной модели (рис. 2).

Рис. 2

Время обращения к ОП (или ОЗУ – оперативное запоминающее устройство) в задачах системотехники называют циклом обращения к памяти.

Непосредственно в вычислительном процессе участвует только ОП. Внешнее ЗУ (ВЗУ) служит для хранения больших массивов информации и обмена данными с ОП на различных этапах вычислений.

В общем случае для решения задачи на компьютере пользователь должен задать алгоритм ее решения в виде программы. При этом под алгоритмом понимают последовательность действий, которые необходимо выполнить (над данными) для получения решения задачи. В результате программа машины может интерпретироваться как алгоритм, представленный в терминах системы команд компьютера.

## 1.2. Неймановские принципы программного управления

Принципы Джона фон Неймана, предложенные в 1945 г., используются в качестве основных для построения большинства современных цифровых компьютеров.

Главная неймановская идея заключается в реализации на некоторых аппаратных носителях принципа хранимой программы, представленной двоичными кодами, различающимися по способу использования в вычислительном устройстве.

Рассмотрим 5 основных принципов организации вычислений, предложенных Джоном фон Нейманом, на начальных этапах создания вычислительной техники.

Первый принцип — использование двоичной системы счисления в качестве базовой. В соответствии с данным принципом обрабатываемая и управляющая информация кодируется двоичной системой счисления и разделяется на блоки, называемые машинными словами.

Использование двоичной системы определяется следующими преимуществами:

- 1. Числовая информация в ЭВМ отождествляет состояние физических элементов, применяемых в устройствах или блоках машины для хранения и преобразования данных. Причем простота управления переключением этих схем очевидна.

- 2. Выполнение арифметических и логических операций в компьютере базируется на известных законах булевой алгебры. Наработка этих законов и простота реализации вычислений в двоичной системе общеизвестны и ведут отсчет еще с позапрошлого века.

- 3. Система счисления с основанием, равным двум, близка к оптимальной.

- 4. В литературе имеются исследования, доказывающие, что двоичная система имеет быстродействие примерно на 26% большее, чем любая другая. И вообще, из всех систем счисления двоичная система самая быстродействующая.

- 5. Аппаратура и информация, использующие двоичное кодирование, имеют наибольшую помехозащищенность.

В общем случае, если задачу выбора системы счисления обосновать с точки зрения организации живой материи, то можно сделать аналогичный вывод. Это следует из того, что процесс деления клетки — основного элемента организованной материи — имеет явно выраженную двоичную зависимость. Причем мощность этого процесса столь велика, что определяет воспроизводство всего живого на Земле.

2-й принцип. Информационные слова, циркулирующие в компьютере, различаются по способу использования, но не способом кодирования, т.е. согласно принципу хранимой программы, команды закодированы и хранятся в памяти в виде кодов наравне с данными. Это позволяет каждую команду использовать в программе многократно и, кроме того, над командами, как и над данными, выполнять различные преобразования, т.е. при необходимости модифицировать команды.

*3-й принцип*. Машинные слова размещаются в ячейках памяти в виде двоичных кодов и идентифицируются номерами, называемыми адресами памяти. Как правило, в качестве машинной памяти используются схемы ЗУ с произвольной выборкой. Создание более эффективных систем (например, ассоциативной памяти) позволяет реализовать безадресные обращения, что в общем случае свойственно памяти человека. Однако стоимость проектирования таких схем существенно велика, хотя при наличии отлаженных технологий процесс создания встроенных специальных ЗУ используется достаточно часто.

4-й принцип заключается в организации программного управления работой машины. Данный принцип предполагает, что алгоритм решения задачи состоит из отдельных команд, каждая из которых предписывает определенные действия. Команда включает в свой состав определенное число разрядов, кодирующих: 1) выполняемую операцию, 2) адреса источников операндов, 3) приемники результата и другую информацию. Например:

| КОП А1 | A2 | A3 |  |

|--------|----|----|--|

|--------|----|----|--|

5-й принцип — принцип последовательной отработки команд. В процессе выполнения программы порядок исполнения команд определяется алгоритмом решаемой задачи. Первой выполняется команда, заданная начальным адресом. Адрес очередной команды определяется в процессе выполнения текущей. Данный принцип нарушается, если компьютер имеет архитектуру, отличную от неймановской, т.е. имеется, например, возможность параллельного исполнения команд в процессоре с несколькими АЛУ и т.д. Таким образом, в процессе проектирования компьютеров, как правило, осуществляется синтез неймановских архитектур. Однако в спецсистемах, предназначенных для быстрых вычислений, при введении различных форм параллелизма возможно нарушение 3-го и 5-го принципов.

Нарушение других принципов, очевидно, приведет к созданию вычислительных устройств, функционирующих на других физических основах.

Основными характеристиками компьютеров считаются:

1. Производительность, т.е. скорость выполнения контрольных или измерительных смесей команд. В общем случае для определения производительности используют смеси двух типов, а именно синтетические (или полусинтетические) и профильные.

Синтетические смеси представляют собой отобранные специальным образом процедуры с наибольшим удельным весом команд, соответствующих данному классу задач.

Профильные смеси представляют собой набор фрагментов реальных программ, работающих в единой операционной среде. Они используются для определения производительности компьютеров на проблемно-ориентированных задачах.

2. Стоимость – это показатель, включающий в себя расходы на эксплуатацию и обслуживание компьютера.

На практике указанные две характеристики могут быть использованы для построения диаграмм вида стоимость/производительность. Эти диаграммы при покупке вычислительной техники позволяют выбрать оптимальный или квазиоптимальный для данного класса задач вариант системы. Следует, однако, помнить, что индекс стоимость/производительность не включают в свой состав расходы на покупку компьютера. Это обусловлено тем, что основное назначение данного показателя заключается в определении эффективности эксплуатации новой техники, а не ее покупки.

- 3. Число разрядов в машинном слове определяет точность представления данных и результатов (измеряется в битах).

- 4. Скорость выполнения основных видов команд, т.е. преобразований типа «регистр-регистр», «регистр-память» и т.д. (измеряется в оп/с).

- 5. Емкость оперативной памяти (измеряется в мегабайтах).

- 6. Скорость обмена между ядром ЭВМ и периферийным оборудованием, где под ядром понимают схемы процессора и памяти и их линии связей.

#### 2. ПРОЦЕССОРЫ

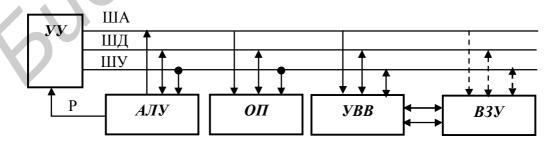

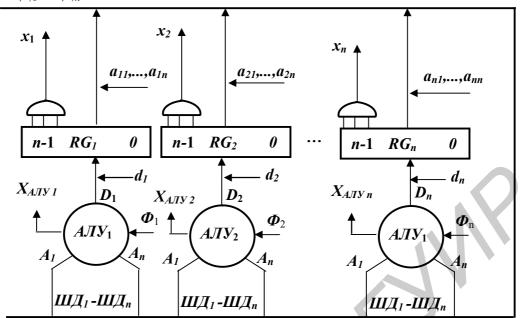

Процессор занимает центральное место в структуре компьютера. Он предназначен для реализации процессов, связанных с обработкой цифровой информации, а также для управления взаимодействием узлов и блоков, входящих в состав вычислительного устройства. Укрупненно структура процессора может быть представлена в виде композиции операционного и управляющего автоматов (рис. 3).

Рис. 3

При этом управляющий автомат может быть построен по схеме с жесткой логикой (автомат Мили или Мура) или спроектирован в виде микропрограммного УУ с хранимой логикой (схема Уилкса или ее модификации). Операционный автомат (ОА) используется для преобразования данных и включает в свой состав регистры, элементы управляющей логики, сумматоры, сдвигатели и другие функциональные узлы.

Вычислительный процесс инициируется кодом операции каждой выполняемой команды. Он преобразуется управляющим автоматом в последовательность сигналов, подаваемых на вход ОА, т.е. задает временную диаграмму пересылки и преобразования операндов.

По результатам выполненной команды ОА процессора формирует ряд признаков, используемых для ветвления исполняемого алгоритма.

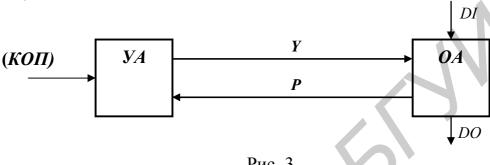

## 2.1. Микропроцессорная секция К1804ВС1

Четырехразрядная микропроцессорная секция К1804ВС1 предназначена для построения операционных блоков цифровых устройств с разрядностью,

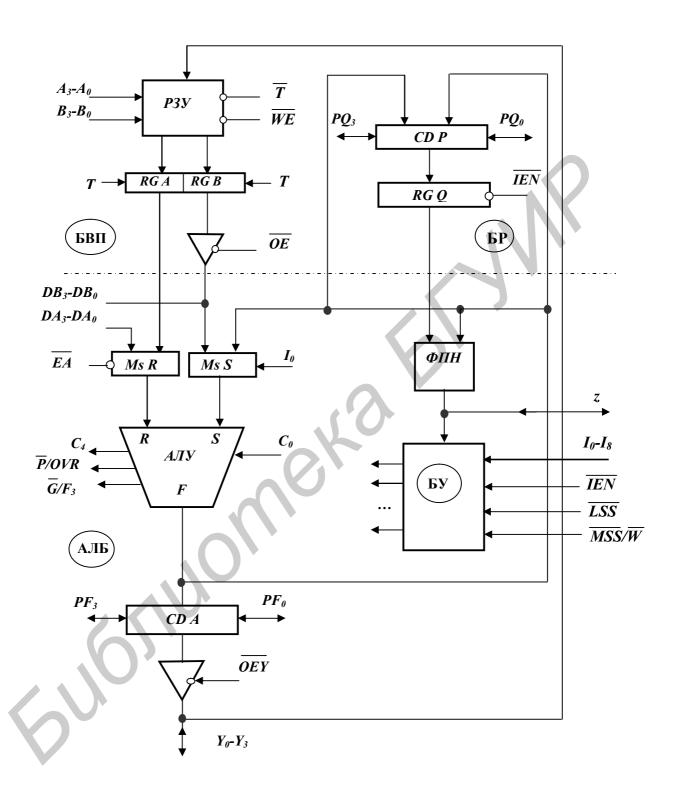

кратной 4. На структурной схеме  $M\Pi C$  условно выделяют четыре крупных блока (рис. 4): 1)  $BB\Pi$  — блок внутренней памяти; 2)  $A\Pi B$  — арифметико-логический блок; 3) блок регистра Q; 4) BY — блок управления.

Рис. 4

*Блок внутренней памяти* содержит в своем составе регистровое 3V с двумя независимыми каналами выбора информации — канал адреса A и канал адреса B. На входе P3V включен сдвигатель A (CD A), позволяющий записывать в 3V

информацию как без сдвига, так и со сдвигом вправо или влево на один разряд. Запись в P3V возможна только по адресу, указанному на линиях канала B.

Регистры  $RG\ A$  и  $RG\ B$ , установленные на выходах P3V, представляют собой 4-разрядные устройства с синхронной записью информации.

Выбор из  $BB\Pi$  любого POH в качестве источника информации осуществляется путем подачи на входы A и B адресной информации без программирования каких-либо других управляющих сигналов. Из P3V одновременно могут быть считаны два операнда. При этом, если на входах A и B установлены одинаковые адреса (выполняется обращение к одному и тому же POH), то на обоих выходах P3V появляются идентичные данные.

Запись данных в P3V выполняется только по каналу B, при этом адрес по каналу A игнорируется. Моментом начала записи в P3V является момент перехода тактового импульса из состояния «1» в состояние «0».

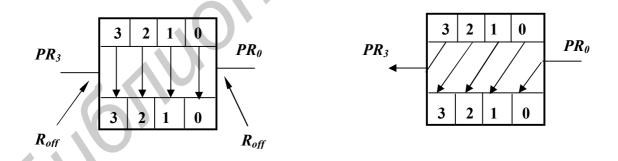

Информация перед записью может быть сдвинута влево или вправо на один разряд. Эту операцию выполняет сдвигатель данных  $CD\ A$ , управляемый сигналами с дешифратора приемника результата. Схема  $CD\ A$  имеет следующую структуру:

Рис. 5

Арифметико-логический блок включает в свой состав двухвходовое АЛУ, выполняющее 8 арифметических и логических операций и формирующее 4 признака результата:

$C_{_{4}}$  — перенос из старшего разряда результата;

OVR – переполнение; OVR = 1, если  $C_4 \oplus C_3 = 1$ ;

$F_3$  – знак числа или значения старшего разряда на выходе AJV;

z — признак нулевого результата.

С выхода AЛУ информация подается на первый вход селектора выходных данных (CBД). На второй вход селектора данные передаются прямо с выхода  $RG\ A$ , минуя AЛУ. С выхода CBД информация через управляемые усилители передается на выходную шину  $M\Pi C$  – трехстабильную шину Y.

Управление работой АЛБ осуществляется с помощью табл. 1,2,3.

Таблица 1

Таблица 2

|       | Mı    | икро  | код            | Источник операндов <i>АЛУ</i> |          |  |  |  |

|-------|-------|-------|----------------|-------------------------------|----------|--|--|--|

| $I_2$ | $I_1$ | $I_0$ | <i>8</i> -рич. | R                             | S        |  |  |  |

| 0     | 0     | 0     | 0              | A                             | Q        |  |  |  |

| 0     | 0     | 1     | 1              | A                             | $Q \\ B$ |  |  |  |

| 0     | 1     | 0     | 2              | 0                             | Q        |  |  |  |

| 0     | 1     | 1     | 3              | 0                             | B        |  |  |  |

| 1     | 0     | 0     | 4              | 0                             | A        |  |  |  |

| 1     | 0     | 1     | 4<br>5         | D                             | A        |  |  |  |

| 1     | 1     | 0     | 6              | D                             | Q        |  |  |  |

| 1     | 1     | 1     | 7              | D                             | $Q \\ 0$ |  |  |  |

| Мин                             | срокс                           | ЭД                              | Операция                                                                                                                                            |

|---------------------------------|---------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_5$ $I_4$                     | $I_3$                           | <i>8</i> -рич.                  | АЛУ                                                                                                                                                 |

| 0 0 0 0 0 1 0 1 1 0 1 1 1 1 1 1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | 0<br>1<br>2<br>3<br>4<br>5<br>6 | $R+S+C_0$ $S-R-I+C_0$ $R-S-I+C_0$ $R \lor S$ $\overline{R} \land S$ $\overline{R} \land S$ $\overline{R} \Leftrightarrow S$ $\overline{R} \oplus S$ |

Селектор источников данных выбирает операнды для R и S входов AЛУ. Причем выбор источников операндов осуществляется сигналами микрокоманды  $I_2 - I_0$  (см. табл. 1), приемника результата — сигналами  $I_8 - I_6$  (см. табл. 3), а функции AЛУ — сигналами  $I_5 - I_3$  (см. табл. 2).

Арифметические операции в AJIV выполняются с учетом значения сигнала входного переноса  $C_0$  и по правилам дополнительного кода при представлении отрицательных чисел. Это, в частности, означает, что если оба операнда нулевые и выполняется вычитание при  $C_0 = 0$ , на выходе устанавливается значение 1111, обозначающее в дополнительном коде число -1. При  $C_0 = 1$  на выходе

| ]     | Микр  | окод  | Į          | I      | P3 <i>Y</i>         | RG     | Q                   | Выход |

|-------|-------|-------|------------|--------|---------------------|--------|---------------------|-------|

| $I_8$ | $I_7$ | $I_6$ | 8-<br>рич. | Сдвиг  | Загрузка            | Сдвиг  | Загрузка            | Y     |

| 0     | 0     | 0     | 0          | _      | _                   | _      | $F \rightarrow Q$   | F     |

| 0     | 0     | 1     | 1          | _      | _                   | _      | _                   | F     |

| 0     | 1     | 1     | 2          | _      | $F \rightarrow B$   | _      | _                   | A     |

| 0     | 1     | 1     | 3          | _      | $F \rightarrow B$   | _      | _                   | F     |

| 0     | 1     | 0     | 4          | Вправо | $F/2 \rightarrow B$ | Вправо | $Q/2 \rightarrow Q$ | F     |

| 1     | 0     | 1     | 5          | Вправо | $F/2 \rightarrow B$ | _      | _                   | F     |

| 0     | 0     | 1     | 6          | Влево  | $2F \rightarrow B$  | Влево  | $2Q \rightarrow Q$  | F     |

| 1     | 1     | 1     | 7          | Влево  | $2F \rightarrow B$  | _      | -                   | F     |

AЛУ формируется значение 0000.

Выводы  $\overline{P}$ ,  $\overline{G}$   $A \Pi Y$  позволяют с помощью внешних схем организовать между секциями ускоренный перенос при комплексировании их в блок с разрядностью, кратной четырем.

Сигналы признаков, формируемые АЛУ, используются следующим образом.

Вывод  $F_3$  – старший разряд AЛУ – может быть использован, например, для определения знака арифметической операции. При этом отсутствует необходимость отпирания трехстабильной выходной шины данных, что упрощает выполнение команд перехода в мультипроцессорных системах. При соединении нескольких МПС знаком является вывод  $F_3$  старшей секции. Выводы  $F_3$  остальных секций не используются.

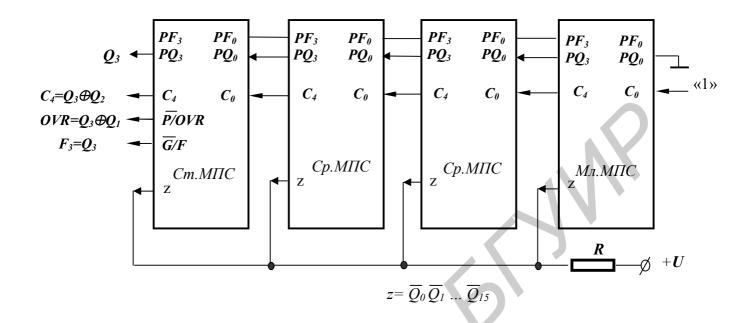

Выход z выполнен по схеме с открытым коллектором, и при объединении нескольких МПС все выводы z соединяются в общей точке, подключаемой через резистор к источнику питания. Потенциал этой точки имеет высокий уровень, если все выходы AЛУ одновременно нулевые.

*Блок регистра Q* состоит из дополнительного регистра  $RG\ Q$  и сдвигателя  $CD\ P$ . Сдвигатель данных позволяет перезаписывать информацию в  $RG\ Q$  как

без сдвига, так и со сдвигом влево или вправо на один разряд. Запись данных в  $RG\ Q$  выполняется по положительному фронту сигнала синхроимпульса.

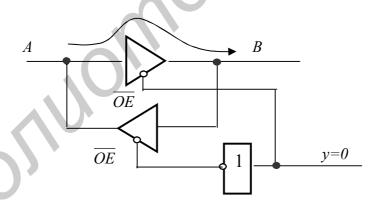

*Блок управления* формирует управляющие сигналы для остальных блоков  $M\Pi C$ . Входами данной подсхемы является шина микрокоманды  $I_8$ — $I_0$ , которую условно можно разделить на три части. Блок управления соответственно также может быть представлен в виде совокупности трех частей, причем первая — вырабатывает сигналы управления для  $CU\mathcal{I}$ , вторая — используется для управления функцией  $A\Pi V$ , а третья — для управления  $CB\mathcal{I}$ , RGQ, CDP, CDA.

Инверсный сигнал  $\overline{OE}$  предназначен для управления *Y*-выходами *МПС*. При  $\overline{OE}=0$  разрешается вывод информации через *Y*-выходы на  $\overline{III}$ Д, если  $\overline{OE}=1$ , выходная шина отключается (переводится в состояние  $R_{off}$ ).

## 2.2. Микропроцессорная секция К1804ВС2

По отношению к предыдущей разработке процессорная секция *К1804ВС2* имеет ряд усовершенствований (рис. 6):

во-первых,  $A \Pi Y$  микропроцессора выполняет арифметические, логические и специальные функции;

во-вторых, сдвигатель данных  $A \Pi Y CDA$  выполняет как логические, так и арифметические сдвиги;

в-третьих, в микропроцессоре заложена возможность внешнего расширения P3V путем подсоединения любого числа дополнительных рабочих регистров, обращение к которым возможно в различных режимах адресации.

В целом микропроцессорная секция состоит из 4 основных блоков: блока внутренней памяти (EBII), арифметико-логического блока (AJIE), блока рабочего регистра (EP) и блока управления (EV).

<u>Блок внутренней памяти</u> включает в свой состав шестнадцать 4-разрядных POH, объединенных в P3V, а также регистр A и регистр B с трехстабильным выходом. Информация, размещаемая в регистрах, адресуется по каналам адреса  $A_3 - A_0$  и  $B_3 - B_0$  P3V соответственно.

Рис. 6

Управление выходом регистра B осуществляется сигналом  $\overline{OE}$ , что позволяет передавать данные с выхода  $\overline{BBH}$  на вход мультиплексора  $\overline{MsS}$  AJY и на входы  $\overline{DB_3}$ - $\overline{DB_0}$   $\overline{MHC}$  при  $\overline{OE}=0$ , кроме того, при  $\overline{OE}=1$  имеется возможность вводить информацию со входов  $\overline{DB_3}$ - $\overline{DB_0}$ .

Каждый из POHов может быть выбран в качестве источника или приемника полученного результата. При этом информация с выходов P3V записывается в RG A или RG B при наличии уровня логической единицы на входе T, в частности, если T=0, то регистры находятся в режиме хранения.

Запись информации в P3V может производиться только по адресу B. При этом необходимо, чтобы на входах  $\overline{WE}$  и  $\overline{T}$  был установлен логический « $\theta$ ». Подача на входы  $\overline{WE}$  или  $\overline{T}$  единичного потенциала запрещает режим записи. Считывание информации из P3V может производиться одновременно по адресам A и B. Если на входах A и B установлены одинаковые адреса, то на выходы P3V считывается одинаковая информация.

$M\Pi C$  может функционировать в режиме двухадресной (B=A+B) и трехадресной (Q=A+B) обработки данных. В двухадресном режиме на входы  $A_3-A_0$  подается адрес операнда R, а на входы  $B_3-B_0$  — адрес операнда S и результата. В трехадресном режиме приемником результата служит дополнительный регистр Q, адресуемый в микрокоманде неявно.

<u>Арифметико-логический блок</u> состоит из двух мультиплексоров MsS и MsR, арифметико-логического устройства, сдвигателя данных CDA с трехстабильным выходом (рис. 7), формирователя признака нуля  $\Phi\Pi H$ , используемого при выполнении арифметических, логических и специальных функций, а также при формировании сигналов состояния  $M\Pi C$ .

Входные мультиплексоры осуществляют выбор источников операндов R и S под действием управляющих сигналов  $\overline{EA}$ ,  $\overline{OE}$ ,  $I_0$  в соответствии с табл. 4. Из таблицы следует, что, если  $I_0$ =1, то параллельно с выполнением операции в  $A\Pi V$  возможен вывод данных из P3V по шине  $DB_3$ – $DB_0$  во внешнюю память.

Таблииа 4

| $\overline{EA}$ | $I_0$ | $\overline{OE}_1$ | R  | S  |

|-----------------|-------|-------------------|----|----|

| 0               | 0     | 0                 | A  | В  |

| 0               | 0     | 1                 | A  | DB |

| 0               | 1     | 0                 | A  | Q  |

| 0               | 1     | 1                 | A  | Q  |

| 1               | 0     | 0                 | DA | В  |

| 1               | 0     | 1                 | DA | DB |

| 1               | 1     | 0                 | DA | Q  |

| 1               | 1     | 1                 | DA | Q  |

Арифметико-логическое устройство обеспечивает выполнение семи арифметических, девяти логических операций, а также девяти специальных функций. Выбор операции AJV осуществляется под действием поля регистра микрокоманды  $I_8-I_0$ , причем если разряды  $I_4-I_0$  имеют значение 00000, то AJY выполняет специальные функции.

Выводы  $\overline{P},\overline{G}$  *МПС* используются для организации ускоренного переноса в многоразрядных процессорах. Причем выходы  $\overline{P},\overline{G}$  *Ст.МПС* не используются, а выходы  $F_3$ , OVR — наоборот, используются только у Cm.MПC. Этот факт позволяет объединить выводы  $\overline{G}$  и  $F_3$ , а также  $\overline{P}$  и OVR и соответственно уменьшить общее число контактов интегральной микросхемы.

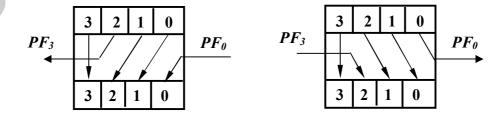

Данные с выхода AЛУ могут быть переданы на входы сдвигателя CD P регистра Q и на входы сдвигателя CD A, соединенного с выходами F AЛУ. Таким образом, выходная информация может записываться в P3V и выводиться на шину  $Y_3$  - $Y_0$  как без сдвига, так и со сдвигом влево или вправо на один разряд.

Отличительной особенностью CDA AЛУ является процесс выполнения арифметических сдвигов. Схема сдвигателя для старшей  $M\Pi C$  процессора при сдвиге влево или вправо на 1 разряд в этом случае имеет вид, показанный на рис. 7.

Рис. 7

Выполнение сдвиговых операций в процессоре K1804BC2 осуществляется под управлением сигналов микрокоманды  $I_8-I_5$ , при этом сигнал  $\overline{IEN}=0$ , сигналы микрокоманды  $I_0 \vee I_1 \vee I_2 \vee I_3 \vee I_4=1$  (табл. 5).

Таблица 5

|                   |                            | •  |         |                  |            |                |                          |

|-------------------|----------------------------|----|---------|------------------|------------|----------------|--------------------------|

| Код мик-          |                            |    |         | Выходн           | ые сигна   | лы             |                          |

| рокоман-<br>ды    |                            |    |         | $\overline{P/C}$ | VR         | $\overline{G}$ |                          |

| ДЫ                | Операция АЛУ               | _  | $C_4$   |                  | Мл. и      |                | Мл. и                    |

| $I_4I_3I_2I_1I_0$ |                            | Z  | C4      | Ст.<br>МПС       | Ср.<br>МПС | Ст.<br>МПС     | <i>Ср.</i><br><i>МПС</i> |

| 00000             |                            | Ci | пециалы | ные функ         | сции       |                |                          |

| 00001             | F <sub>AJIV</sub> :=«1111» | 0  | 0       | 0                | 0          |                |                          |

| 0001x             | $S-R-1+C_0$                |    |         |                  |            |                |                          |

| 0010x             | $R-S-1+C_0$                |    |         |                  |            |                |                          |

| 0011x             | $R+S+C_0$                  |    |         |                  |            |                |                          |

| 0100x             | $S+C_0$                    | Z  | $C_4$   | OVR              | $\bar{P}$  |                |                          |

| 0101x             | $\overline{S}+C_0$         |    |         |                  |            |                |                          |

| 0110x             | $\underline{R} + C_0$      |    |         |                  |            |                |                          |

| 0111x             | $\overline{R}+C_{\theta}$  |    |         | U'               |            | E              | $\overline{G}$           |

| 1000x             | $F_{AJIY}$ :=« $0000$ »    | 1  | 0       | 0                | 0          | $F_3$          | G                        |

| 1001x             | $\overline{R} \wedge S$    |    |         |                  |            |                |                          |

| 1010x             | $\overline{R} \oplus S$    |    |         |                  |            |                |                          |

| 1011x             | R⊕S                        |    |         |                  |            |                |                          |

| 1100x             | $\overline{R \wedge S}$    | Z  | 0       | 0                | 0          |                |                          |

| 1101x             | $\overline{R \vee S}$      |    |         |                  |            |                |                          |

| 1110x             | $R \wedge S$               |    |         |                  |            |                |                          |

| 1111x             | $R \vee S$                 |    |         |                  |            |                |                          |

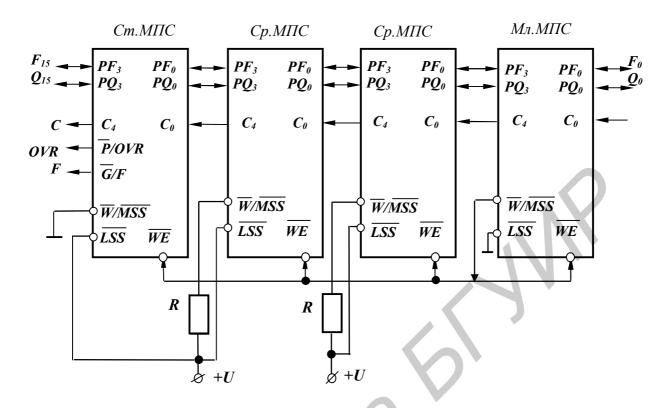

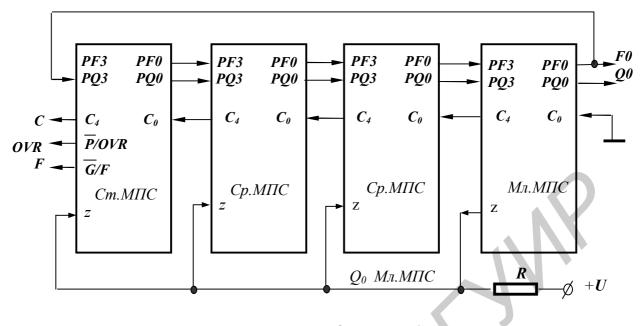

Функционирование  $M\Pi C$  при выполнении некоторых операций зависит от ее положения в системе, поэтому при соединении секций необходимо выполнить их настройку на заданное положение:  $Cm.M\Pi C$ ,  $Cp.M\Pi C$ ,  $Mn.M\Pi C$ . Такая настройка выполняется при помощи выводов  $\overline{LSS}$  и  $\overline{MSS}/\overline{W}$ . В младшей  $M\Pi C$  на входе  $\overline{LSS}$  устанавливается «0», при этом линия  $\overline{MSS}/\overline{W}$  становится выходом  $\overline{W}$ , причем необходимо, чтобы  $\overline{W}$  =0 для каждого такта записи в РЗУ, в противном случае —  $\overline{W}$  =1. Поэтому, как правило, входы  $\overline{WE}$  всех  $M\Pi C$  соединяют с выходом  $\overline{W}$   $Mn.M\Pi C$ , как показано на рис. 8.

Рис. 8

В средней и старшей  $M\Pi C$  на входе  $\overline{LSS}$  устанавливается логическая «1». При этом линия  $\overline{MSS}/\overline{W}$  становится входом секции  $\overline{MSS}$ . В старшей  $M\Pi C$  на этот вход подается уровень нуля, а в средних — уровень логической «1». Это позволяет вывести в старшей  $M\Pi C$  на выходы  $\overline{P}/OVR$  и  $\overline{G}/F_3$  сигналы OVR и  $F_3$ , а на выводы средних  $M\Pi C$  — выходы ускоренного переноса  $\overline{P}$ ,  $\overline{G}$ .

Расширение знака при вычислениях может быть выполнено на несколько разрядов за 1 такт, для чего используется предпоследняя микрокоманда (код  $I_8 - I_5 = E$ , табл. 6). Микрокоманда E передает знак с вывода  $PF_0$  MIIC на выводы  $PF_3$ ,  $Y_3 - Y_0$ . Принцип расширения знака используется не для модификации результата, а для формирования данных. Например, если 16-разрядный процессор должен интерпретировать 8-разрядные данные как двоичные числа со знаком, то знаковый разряд расширяется на один байт. Однако данный подход требует реорганизации межсекционных цепей сдвига процессора.

|                                |                                    |                                      | Y               | 73              | Y                       | 2               |                 |                 | P               | F <sub>3</sub>  |                  | W     | RC             | G Q    |

|--------------------------------|------------------------------------|--------------------------------------|-----------------|-----------------|-------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|-------|----------------|--------|

| I <sub>8</sub> -I <sub>5</sub> | Функц.<br>СДА                      | Функц.<br>СДР                        | Cr.<br>MIIC     | Ср.,Мл.<br>МПС  | C <sub>T.</sub><br>MIIC | Ср.,Мл<br>МПС   | $Y_1$           | $Y_0$           | CT.MITC         | Ср., Мл.<br>МПС | $\mathbf{PF}_0$  | TSS=0 | $PQ_3$         | $PQ_0$ |

| 0000                           | $F/_2 \rightarrow Y$ Ap.C          | $Q \rightarrow Q$                    | F <sub>3</sub>  | PF <sub>3</sub> | PF <sub>3</sub>         | F <sub>3</sub>  | F <sub>2</sub>  | $F_1$           | Bx.             | Bx.             | F <sub>0</sub>   | 0     | R              | off    |

| 0001                           | $F/_2 \rightarrow Y$ Лог.С         | $Q \rightarrow Q$                    | PF <sub>3</sub> | PF <sub>3</sub> | F <sub>3</sub>          | F <sub>3</sub>  | F <sub>2</sub>  | $F_1$           | Bx.             | Bx.             | F <sub>0</sub>   | 0     | R              | off    |

| 0010                           | $F/_2 \rightarrow Y$ Ap.C          | $\frac{Q}{2} \rightarrow Q$ Jor.C    | F <sub>3</sub>  | PF <sub>3</sub> | PF <sub>3</sub>         | F <sub>3</sub>  | F <sub>2</sub>  | $F_1$           | Bx.             | Bx.             | F <sub>0</sub>   | 0     | Bx.            | $Q_0$  |

| 0011                           | $F/_2 \rightarrow Y$ Лог.С         | $Q/2 \rightarrow Q$ Jor.C            | PF <sub>3</sub> | PF <sub>3</sub> | F <sub>3</sub>          | F <sub>3</sub>  | F <sub>2</sub>  | F <sub>1</sub>  | Bx.             | Bx.             | F <sub>0</sub>   | 0     | Bx.            | $Q_0$  |

| 0100                           | $F \rightarrow Y$                  | $Q \rightarrow Q$                    | F <sub>3</sub>  | F <sub>3</sub>  | F <sub>2</sub>          | F <sub>2</sub>  | F <sub>1</sub>  | F <sub>0</sub>  | Bx.             | Bx.             | Р                | 0     | R              | off    |

| 0101                           | $F \rightarrow Y$                  | $\frac{Q}{2} \rightarrow Q$<br>Лог.С | F <sub>3</sub>  | F <sub>3</sub>  | F <sub>2</sub>          | F <sub>2</sub>  | F <sub>1</sub>  | F <sub>0</sub>  | Bx.             | Bx.             | Р                | 1     | Bx.            | $Q_0$  |

| 0110                           | $F \rightarrow Y$                  | $F \rightarrow Q$                    | F <sub>3</sub>  | F <sub>3</sub>  | F <sub>2</sub>          | $F_2$           | F <sub>1</sub>  | $F_0$           | Bx.             | Bx.             | P                | 1     | R              | off    |

| 0111                           | $F \rightarrow Y$                  | $F \to Q$                            | F <sub>3</sub>  | F <sub>3</sub>  | F <sub>2</sub>          | F <sub>2</sub>  | $F_1$           | F <sub>0</sub>  | Bx.             | Bx.             | P                | 1     | R              | off    |

| 1000                           | $2F \to Y$ Ap.C                    | $Q \rightarrow Q$                    | F <sub>3</sub>  | F <sub>2</sub>  | $F_1$                   | F <sub>1</sub>  | $F_0$           | PF <sub>0</sub> | F <sub>2</sub>  | F <sub>3</sub>  | Bx.              | 0     | R              | off    |

| 1001                           | $2F \rightarrow Y$<br>Лог.С        | $Q \rightarrow Q$                    | F <sub>2</sub>  | F <sub>2</sub>  | $F_1$                   | $F_1$           | $F_0$           | PF <sub>0</sub> | F <sub>3</sub>  | F <sub>3</sub>  | Bx.              | 0     | R              | off    |

| 1010                           | $2F \rightarrow Y$ Ap.C            | 2 <i>Q</i> → <i>Q</i><br>Лог.С       | F <sub>3</sub>  | F <sub>2</sub>  | F <sub>1</sub>          | F <sub>1</sub>  | F <sub>0</sub>  | PF <sub>0</sub> | F <sub>2</sub>  | F <sub>3</sub>  | Bx.              | 0     | Q <sub>3</sub> | Bx.    |

| 1011                           | $2F \rightarrow Y$<br>Лог.С        | 2 <i>Q</i> → <i>Q</i><br>Лог.С       | F <sub>2</sub>  | F <sub>2</sub>  | F <sub>1</sub>          | $F_1$           | F <sub>0</sub>  | PF <sub>0</sub> | F <sub>3</sub>  | F <sub>3</sub>  | Bx.              | 0     | Q <sub>3</sub> | Bx.    |

| 1100                           | $F \rightarrow Y$                  | $Q \rightarrow Q$                    | F <sub>3</sub>  | F <sub>3</sub>  | F <sub>2</sub>          | F <sub>2</sub>  | $F_1$           | F <sub>0</sub>  | F <sub>3</sub>  | F <sub>3</sub>  | $R_{off}$        | 1     | R              | off    |

| 1101                           | $F \rightarrow Y$                  | <i>2Q→Q</i><br>Лог.С                 | F <sub>3</sub>  | F <sub>3</sub>  | F <sub>2</sub>          | F <sub>2</sub>  | $F_1$           | $F_0$           | F <sub>3</sub>  | F <sub>3</sub>  | $R_{\rm off}$    | 1     | Q <sub>3</sub> | Bx.    |

| 1110                           | $PF_0 \rightarrow Y_0 Y_1 Y_2 Y_3$ | $Q \rightarrow Q$                    | PF <sub>0</sub> | PF <sub>0</sub> | PF <sub>0</sub>         | PF <sub>0</sub> | PF <sub>0</sub> | PF <sub>0</sub> | PF <sub>0</sub> | PF <sub>0</sub> | Bx.              | 0     | R              | off    |

| 1111                           | $F \rightarrow Y$                  | $Q \rightarrow Q$                    | F <sub>3</sub>  | F <sub>3</sub>  | F <sub>2</sub>          | F <sub>2</sub>  | F <sub>1</sub>  | F <sub>0</sub>  | F <sub>3</sub>  | F <sub>3</sub>  | R <sub>off</sub> | 0     | R              | off    |

Четыре микрокоманды (коды  $I_8 - I_5 = 4$ , 5, 6, 7) используются для формирования паритета на шине  $PF_0$ . Паритет представляет собой результат операции M2 всех выходов AJV и сигнала, подаваемого на вход  $PF_3$ . Паритетная логика обладает способностью наращивания путем соединения вывода  $PF_3$  предыдущей MIIC с выводом  $PF_0$  последующей. При этом уравнение паритета будет иметь следующий вид:

$$PF_{0\ M\pi.MIIC} = F_{15} \oplus F_{14} \oplus ... \oplus F_1 \oplus F_0 \oplus PF_{3\ Cm.MIIC}.$$

Специальные функции, выполняемые  $M\Pi C$ , определяются сигналами  $I_8-I_5$  при наличии нулевой комбинации на входах  $I_4-I_0$ . Схема может выполнять девять специальных функций, которые перечислены в табл. 10. Семь кодовых комбинаций не используются и являются запрещенными при функционировании  $M\Pi C$ .

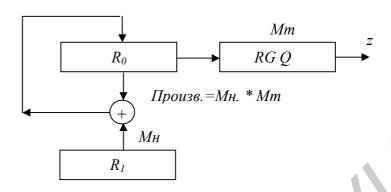

1. Умножение без знака. Реализация данной функции предполагает выполнение базовых операций сдвига и сложения. Для умножения чисел с разрядностью, кратной четырем ( $4n \times 4n$ ), требуется 4n тактов работы  $M\Pi C$ . При выполнении умножения предполагается, что регистр  $R_0$  O3V предварительно был очищен и далее будет использоваться для размещения старших бит частичных произведений результата. Множимое записывается в регистр  $R_1$ , а множитель — в регистр  $R_2$ . Регистры  $R_0$  и  $R_1$  могут быть расположены в P3V  $M\Pi C$  и адресованы по входам A и B соответственно, а также располагаться во внешней памяти процессорной секции. Во втором случае регистр  $R_1$  используется как источник операнда R и соединяется с шиной  $DA_0 - DA_3$ , а регистр  $R_0$  — как источник операнда S и как приемник результата и соединяется с шинами  $DB_0 - DB_3$  и  $Y_3 - Y_0$ . После начальной установки множитель из  $R_2$  пересылается в RG Q. После этого микрокоманда умножения без знака выполняется 4n раз.

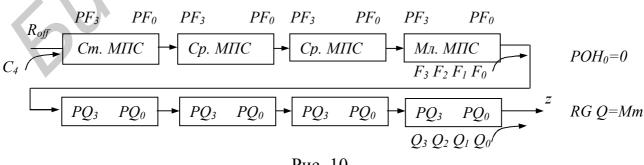

Соединение выводов МПС при выполнении данной специальной функции показано на рис. 9.

Рис. 9

Шина *z Мл.МПС* включена в режим выдачи информации. Сюда выдается младший разряд множителя из  $RG\ Q\ (Q_0\ Mл.M\Pi C\ )$ . Линии  $z\$ остальных  $M\Pi C\$ являются входами. AJJV реализует функцию  $F=S+C_0$  при z=0 или  $F=R+S+C_0$ при z=1. Таким образом, при  $z=Q_0=1$  выполняется сложение множимого из R1 с частичным произведением. При  $z=Q_0=0$  сложение не выполняется  $(C_0 = 0).$

По каждому положительному фронту синхросигнала содержимое выходов АЛУ сдвигается вправо, и полученное частичное произведение записывается в  $R_0$  (рис. 10, 11). При этом сигнал  $C_4$   $Cm.M\Pi C$  передается в старший разряд  $R_0$ , а

Рис. 10

младший разряд  $R_0$  через выводы  $PF_0$  Mл.MПС и  $PQ_3$  Cm.MПС передается в регистр Q, одновременно выполняется сдвиг RG Q вправо.

Рис. 11

При использовании типичного устройства управления для выполнения умножения без знака в  $M\Pi\Pi$  требуется хранить только две микрокоманды (табл.7), а общее время умножения составит 4n+1 тактов.

Таблица 7

| Антоо |               |                         | Комментарий                |                   |                                                                     |                        |              |       |                                                 |

|-------|---------------|-------------------------|----------------------------|-------------------|---------------------------------------------------------------------|------------------------|--------------|-------|-------------------------------------------------|

| Адрес | $I_0$         | $I_4I_3I_2I_1$          | $I_8I_7I_6I_5$             | $\overline{OE}_I$ | ŌEŸ                                                                 | $A_3-A_0$              | $B_3-B_0$    | $C_0$ |                                                 |

| $A_1$ | X             | $0110$ $R+S+C_{\theta}$ | 0110<br>F→Y<br>F→Q         | X                 | X                                                                   | 0010<br>R <sub>2</sub> | XXXX         | 0     | $RG_2 \rightarrow RG Q$ $(Mm \rightarrow RG Q)$ |

| $A_2$ | $0 \atop S=B$ | 0000                    | 0000<br>R+S+C <sub>0</sub> | 0<br>S=B          | $ \begin{array}{c} 0 \\ \frac{1}{2}F \\ \rightarrow Y \end{array} $ | 0001<br>R <sub>1</sub> | 0000<br>RG 0 | 0     | Умножение $R_0 := R_0 + R_1$                    |

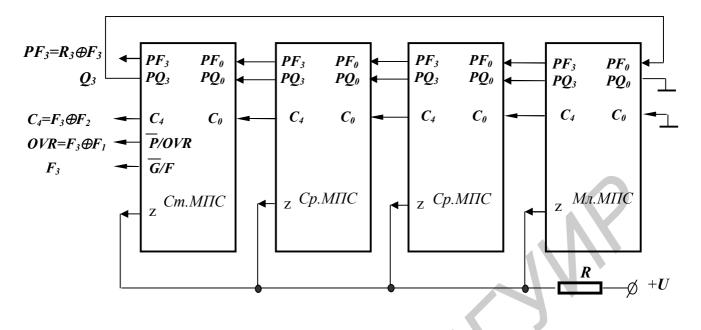

2. Умножение в дополнительном коде. Данный алгоритм выполняется аналогично предыдущему, за исключением последнего такта, на котором производится коррекция результата. Начальная установка и первые 4n–1 тактов умножения выполняются точно так же, как и при умножении без знака. Однако в данном случае в старший разряд сдвинутого частичного произведения в каждом такте записывается сумма  $F_3 \oplus OVR$ , а не  $C_4$ . Это обеспечивает передачу

требуемого бита в старший разряд частичного произведения при возникновении переноса.

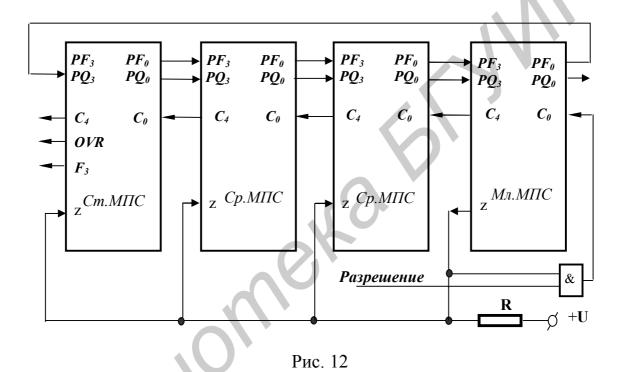

На 4n-м такте знаковый разряд множителя находится на шине z Mл.МПС. В это время необходимо подать микрокоманду последнего такта умножения в дополнительном коде или выполнить коррекцию результата.

Объединение МПС при выполнении умножения в дополнительном коде представлено на рис. 12.

При умножении на входе  $C_0$  процессора должен присутствовать уровень нуля до последнего такта. На последнем такте на данном входе должен присутствовать сигнал, соответствующий логическому уровню линии z. В связи с этим на входе  $C_0$  устанавливают элемент 2И с входными сигналами z и разрешение. Сигнал «Разрешение» устанавливается в единичное состояние только на последнем такте умножения. В остальных тактах линия z используется точно так же, как и в предыдущей команде.

На последнем такте умножения в дополнительном коде АЛУ реализует функцию  $F=S+C_0$  при z=0 и или  $F=S-R-1+C_0$  при z=1. Таким образом, если множитель положительный, то процесс умножения на этом такте заканчивает-

ся, а если множитель отрицательный, то множимое вычитается из полученного частичного произведения, после чего умножение заканчивается.

*Пример*. Пусть Mh=7, Mm=-5. Тогда в результате умножения получим произведение  $[-\Pi p]_{\partial}=1.1011101$ . В соответствии с рис. 11 процесс формирования дополнительного кода результата будет иметь вид:

$$00000000 RGSm$$

1 шаг:  $01110000 + MH$

$00111000 RGSm + MH, RGSm \cdot 2;$

2 шаг:  $01110000 + MH$

$01010100 RGSm + MH, RGSm \cdot 2;$

3 шаг:  $00000000 + 0$

$00101010 RGSm + MH, RGSm \cdot 2;$

4 шаг:  $01110000 + MH$

$01001101 RGSm + MH, RGSm \cdot 2;$

5 шаг:  $10010000 [-MH]_{\partial} - \kappa oppekuun$

$11011101 RGSm - MH = [-\Pi p]_{\partial}$ .

3. Нормализация чисел обычной и двойной длины. Операция нормализации чисел в дополнительном коде выполняется путем сдвига числа в сторону старших разрядов до тех пор, пока два старших бита не будут иметь различные значения. При этом знак нормализуемого операнда фиксируется в старшем разряде.

Пример

Нормализация выполняется для чисел как обычной, так и двойной длины. При нормализации чисел обычной длины используется только регистр Q, а при нормализации чисел двойной длины необходимо использовать еще

A J V и блок внутренней памяти. В первом случае операнд помещается в регистр Q и по положительному фронту тактового сигнала выполняется его сдвиг в сторону старших разрядов. Режим сдвига сохраняется до получения в двух старших битах регистра Q различных значений (0.1... или 1.0...), при этом через вывод  $PQ_0$  M IIC в младшие разряды регистра Q вдвигаются нулевые значения. Появление «1» на выходе  $C_4$  Cm.M IIC означает окончание операции нормализации; это обусловлено тем, что в Cm.M IIC значение переноса формируется по закону  $C_4 = Q_3 \oplus Q_2$ . Кроме того, по признаку OVR можно определить предпоследний такт нормализации, так как  $OVR = Q_2 \oplus Q_1$ , т.е. опережает  $C_4$  на один такт.

Чтобы не выполнять нормализацию нулевого операнда, необходимо идентифицировать соответствующую ситуацию установкой какого-либо признака. С этой целью используется схема ФПН, на выходе z которой устанавливается «1», если все выходы регистра Q — нулевые. При появлении единицы на выходе  $C_4$  операция нормализации прекращается, а на выходе  $F_3$  Cm.MПC устанавливается знак числа, хранящегося в RG Q  $(Q_3 \rightarrow F_3)$ .

При выполнении операции нормализации обычной длины можно подсчитать количество тактов, необходимое для выполнения этой операции. С этой целью на выходе  $C_0$  *МПС* устанавливается логическая единица, при этом регистр P3V, адресованный по каналу B, становится счетчиком тактов. В данном случае AJV выполняет функцию  $F=S+C_0$ .

Соединение выводов МПС при выполнении операции нормализации чисел обычной длины имеет вид, показанный на рис. 13.

При выполнении сдвигов счетчик тактов может быть организован во внешней памяти. В данном случае содержимое счетчика передается на S вход AJV через внешнюю шину  $DB_3 - DB_0$ , а результат выводится на шину  $Y_3 - Y_0$ . Если выполняется нормализация чисел двойной длины, то старшие разряды числа находятся в ячейке P3V, адресуемой по B, а младшие – в  $RG\ Q$ . Вывод  $PQ_3$  старшей  $M\Pi C$  должен быть соединен с выводом  $PF_0$  младшей  $M\Pi C$ . На выводе

$PQ_0$  младшей МПС (так же, как и при выполнении нормализации чисел обычной длины) устанавливается ноль.

Рис. 13

Для хранения старших разрядов нормализуемого числа можно также использовать и внешнюю память, при этом источником операнда служит шина  $DB_3$ – $DB_0$ , а сдвинутое значение передается на шину  $Y_3$  –  $Y_0$ . Так как при нормализации чисел двойной длины AЛУ участвует в выполнении операции и реализует функцию  $F=S+C_0$ , то на выходе  $C_0$  необходимо установить уровень нуля. Для подсчета числа сдвигов в этом случае можно применять внешнюю логику, а сигналы  $C_4$ , OVR и z используются так же, как и при нормализации чисел обычной длины, причем  $C_{4Cm.MIIC} = F_3 \oplus F_2$  этой же секции,  $OVR_{Cm.MIIC} = F_3 \oplus F_1$  тоже старшей MIIC, значение

$$z = \overline{F}_{n-1} \overline{F}_{n-2} ... \overline{F}_1 \overline{F}_0 \overline{Q}_{n-1} \overline{Q}_{n-2} ... \overline{Q}_1 \overline{Q}_0,$$

где n — разрядность нормализуемого числа.

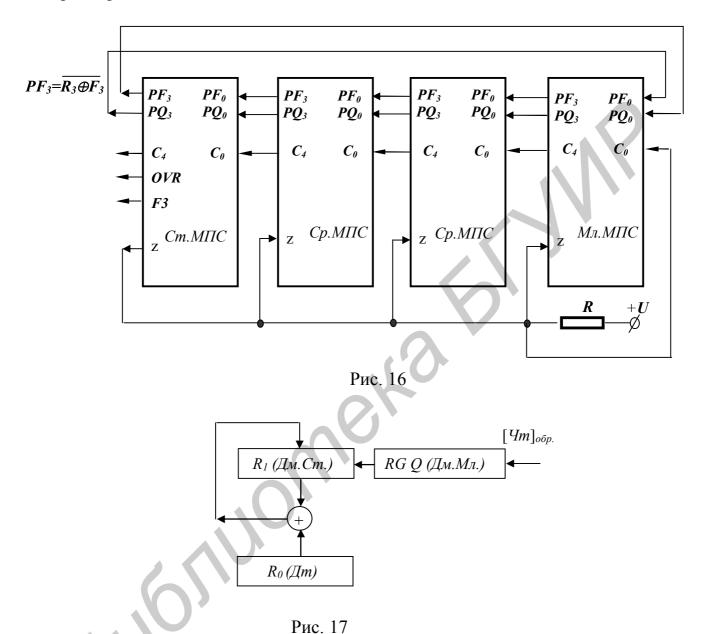

Соединение выводов  $M\Pi C$  при нормализации чисел двойной длины показано на рис. 14.

Рис. 14

Приведенное на рис. 14 обозначение  $R_3$  указывает на знаковый разряд операнда, подаваемого на R-exod АЛУ.

Код микрокоманды для данной специальной функции  $I_8-I_5$  =1010 (для операнда двойной длины) и  $I_8-I_5$  =0111 (для операнда одинарной длины).

4. Преобразование «число со знаком — дополнительный код» ( $I_8$ — $I_5 = 0101$ ). В процессе отработки данной специальной функции положительные числа не модифицируются, а отрицательные — преобразуются в дополнительный код от текущего кода операнда.

В ходе преобразования исходное число подается на вход SAJV (например, из регистра RGB EBII, из RGQ или с внешней шины  $DB_3 - DB_0$ ), а его знак – разряд  $S_3$  Cm.MIIC — на шину z и определяет, над каким числом (отрицательным или положительным) выполняются действия. Вход  $C_0$  Mn.MIIC соединяется с шиной z. АЛУ реализует следующий алгоритм вычислений:

$$F=S+C_0$$

при  $z=0$ ,

$F = \overline{S} + C_0$  при z=1 (образование дополнительного кода).

При преобразовании отрицательного числа на шине z Cm. $M\Pi C$  появляется потенциал логической единицы, что позволяет в процессе преобразования к

обратному коду прибавить единицу, так как z= $C_{\theta}$  .

Соединение выводов МПС для выполнения функции кодопреобразования имеет следующий вид:

- 5. Инкрементирование операнда на 1 или 2. Увеличение числа на единицу или двойку выполняется за один такт. Модифицируемый операнд подается на вход S  $A\Pi V$  (например, из регистра RGB  $BB\Pi$ , из RGQ или с внешней шины  $DB_3 DB_0$ ), после чего выполняется функция  $F = S + C_0 + 1$ , что при  $C_0 = 1$  предполагает увеличение операнда на 2, а при  $C_0 = 0$  на единицу. При выполнении данного преобразования используется стандартное включение  $M\Pi C$ .

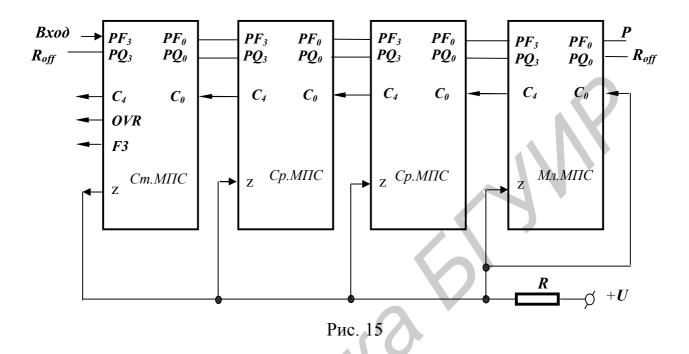

- 6. Деление в дополнительном коде. Данная специальная функция выполняется в соответствии с микрокомандой, представленной в табл. 8.

Таблица 8

| Алпас   |          | Микрокоманда   |                                                                             |                 |                  |                                |                                             |       |                        |  |  |  |  |

|---------|----------|----------------|-----------------------------------------------------------------------------|-----------------|------------------|--------------------------------|---------------------------------------------|-------|------------------------|--|--|--|--|

| Адрес   | $I_0$    | $I_4I_3I_2I_1$ | $I_8I_7I_6I_5$                                                              | $\overline{EA}$ | $\overline{OEY}$ | $A_3 - A_0$                    | $B_3-B_0$                                   | $C_0$ | рий                    |  |  |  |  |

| $A_{I}$ | 0<br>S=B | 0000           | $ \begin{array}{c} 1100 \\ S+R+C_0 \\ z=0 \\ S-R-1+C_0 \\ z=1 \end{array} $ | 0<br>R=A        | X                | 0000<br>R <sub>0</sub><br>(Дт) | 0001<br>R <sub>1</sub><br>(Дм.Ст.<br>часть) | Z     | Деление в<br>доп. коде |  |  |  |  |

Соединение выводов МПС при выполнении операции деления в дополнительном коде показано на рис. 16; рис. 17 поясняет расположение операндов в регистрах и размещение частного.

При выполнении данной специальной функции следует помнить, что используемый алгоритм деления формирует частное в обратном коде. Таким образом, при отрицательном частном необходимо выполнить коррекцию результата с помощью специальной микрокоманды (табл. 9). Данная микрокоманда фактически прибавляет единицу в младший разряд частного, если результат деления отрицательный. При положительном частном коррекция не выполняется.

| <b>Л</b> нрос |          |                          | Μı             | ікроком  | анда           |               |               |       | Коммента-                             |

|---------------|----------|--------------------------|----------------|----------|----------------|---------------|---------------|-------|---------------------------------------|

| Адрес         | $I_0$    | $I_4I_3I_2I_1$           | $I_8I_7I_6I_5$ | EA       | <del>OEY</del> | $A_3$ - $A_0$ | $B_3$ - $B_0$ | $C_0$ | рий                                   |

| A2            | 1<br>S=Q | 0100<br>S+C <sub>0</sub> | 0110<br>F→Q    | 0<br>R=A | X              | 0000          | 0001          | 1     | Деление в<br>доп. коде<br>(коррекция) |

Сводная таблица специальных функций может быть представлена в следующем виде:

Таблица 10

| Мк.<br>код.            |                                                        | P         | $F_3$     |        |           |               |      |                | $\overline{P}/O$ | VR             | $\overline{G}$ | $F_3$          |         | Z       |                  |

|------------------------|--------------------------------------------------------|-----------|-----------|--------|-----------|---------------|------|----------------|------------------|----------------|----------------|----------------|---------|---------|------------------|

| $Bx$ $I_8-I_5$         | Функция<br>АЛУ                                         | Cm.MIIC   | Мл.Ср.МПС | $PF_0$ | $PQ_3$    | $PQ_0$        | W    | C <sub>4</sub> | Ст.МПС           | Ст.МПС         | Ст.МПС         | Мл.Ср.МПС      | Ст.МПС  | Cp.MIIC | $M_{\Pi}.M\Pi C$ |

| 1. Умножение без знака |                                                        |           |           |        |           |               |      |                |                  |                |                |                |         |         |                  |

| 0000                   | $F=S+C_0$ $npu z=0,$ $F=S+R+C_0$ $npu z=1$             | $R_{off}$ | Bx        | $F_0$  | Bx        | $Q_{\theta}$  | 0    | $C_4$          | OVR              | $\overline{P}$ | $F_3$          | $\overline{G}$ | Bx      | Вх      | $Q_0$            |

|                        |                                                        |           | 2. Y.     | множ   | сение     | в доп         | олни | ітел           | ьном к           | оде            |                |                |         |         |                  |

| 0010                   | $F=S+C_0$ $npu \ z=0$ , $F=S+R+C_0$ $npu \ z=1$        | $R_{off}$ | Bx        | $F_0$  | Bx        | $Q_{\theta}$  | 0    | $C_4$          | OVR              | $\overline{P}$ | $F_3$          | $\overline{G}$ | Bx      | Вх      | $Q_0$            |

|                        |                                                        |           |           | 3.     | Инкр      | ремен         | тир  | ован           | ие               |                |                |                |         |         |                  |

| 0100                   | $F = S + I + C_0$                                      | Bx        | Bx        | P      | $R_{off}$ | $R_{off}$     | 0    | C <sub>4</sub> | OVR              | $\overline{P}$ | $F_3$          | $\overline{G}$ | z       | z       | Z                |

|                        | 4. Пр                                                  | реобр     | азова     | ние «  | число     | со зн         | акол | $u - \partial$ | ополні           | ител           | ьный           | і код          | <i></i> |         |                  |

| 0101                   | $F=S+C_0$ $npu \ z=0,$ $F= \gamma \ S+C_0$ $npu \ z=1$ | Bx        | Bx        | Р      | $R_{off}$ | $R_{o\!f\!f}$ | 0    | $C_4$          | OVR              | $\overline{P}$ | *              | $\overline{G}$ | $S_3$   | Вх      | Bx               |

| Мк.<br>код                                        |                                                                 | Pi                      | $F_3$        |               |                   |                   |       |                | $\overline{P}$   | OVR            | $\overline{G}$ | $F_3$          |                                       | Z       |        |

|---------------------------------------------------|-----------------------------------------------------------------|-------------------------|--------------|---------------|-------------------|-------------------|-------|----------------|------------------|----------------|----------------|----------------|---------------------------------------|---------|--------|

| $I_8-I_5$                                         | Функция<br>АЛУ                                                  | Ст.МПС                  | Мл.Ср.МПС    | $PF_0$        | $P \mathcal{Q}_3$ | $P \mathcal{Q}_0$ |       | C <sub>4</sub> | Ст.МПС           | Ст.МПС         | Ст.МПС         | $M\pi.Cp.M\Pi$ | Ст.МПС                                | Cp.MIIC | Мл.МПС |

| 5. Последний цикл умножения в дополнительном коде |                                                                 |                         |              |               |                   |                   |       |                |                  |                |                |                |                                       |         |        |

| 0110                                              | $F=S+C_0$<br>$npu \ z=0$ ,<br>F=S-R-<br>$-1+C_0$<br>$npu \ z=1$ | $R_{o\!f\!f}$           | Bx           | $F_0$         | $R_{o\!f\!f}$     | $Q_0$             | 0     | $C_4$          | OVR              | $\overline{P}$ | $F_3$          | $\overline{G}$ | Bx                                    | Bx      | $Q_0$  |

|                                                   | •                                                               |                         | 6            | . Нор         | мализ             | вация             | обыч  | ной д          | линь             | ı              |                |                |                                       |         |        |

| 0111                                              | $F=S+C_0$                                                       | $F_3$                   | $F_3$        | $R_{o\!f\!f}$ | $Q_3$             | Bx                | 0     | *              | $Q_2 \oplus Q_I$ | P              | $Q_3$          | $\overline{G}$ |                                       | ***     |        |

|                                                   |                                                                 |                         | 7            | ". Нор        | мали              | зация             | двой  | ной д.         | лины             | ı              |                |                |                                       |         |        |

| 1010                                              | $F=S+C_0$                                                       | $R_3 \oplus F_3$        | $F_3$        | Вх            | $Q_3$             | Bx                | 0     | ***            | $F_2 \oplus F_I$ | $\overline{P}$ | $F_3$          | $\overline{G}$ | :                                     | ****    | k      |

|                                                   |                                                                 |                         | 8.           | Делег         | ние в             | допол             | іните | 2льнол         | и код            | )e             |                |                |                                       |         |        |

| 1100                                              | $F=S+R+C_0$ $npu z=0,$ $F=S-R-$ $-l+C_0$ $npu z=1$              | $\neg (R_3 \oplus F_3)$ | $F_3$        | Bx            | $Q_3$             | Bx                | 0     | C <sub>4</sub> | OVR              | $\overline{P}$ | $F_3$          | $\overline{G}$ | * * * * * * * * * * * * * * * * * * * | Bx      | Bx     |

|                                                   |                                                                 | 9. )                    | <b>Делен</b> | ие в д        | )ополі            | нител             | вном  | коде           | (кор             | рекц           | ия)            |                |                                       |         |        |

| 1110                                              | $F=S+C_0$ $npu\ z=0,$ $F=S-R-$ $-I+C_0$ $npu\ z=1$              | $F_3$                   | $F_3$        | $R_{off}$     | $Q_3$             | Вх                | 0     | $C_4$          | OVR              | $\overline{P}$ | $F_3$          | $\overline{G}$ | *<br>*<br>*<br>*<br>*<br>*            | Bx      | Вх     |

<sup>\*</sup>  $F_3$ , если z=0;  $S_3 \oplus F_3$ , если z=1.

\*\*  $Q_3 \oplus Q_2 - \partial$ ля Ст.МПС,  $C_4 - \partial$ ля остальных МПС.

\*\*\* z регистра Q.

\*\*\*\*  $F_3 \oplus F_2 - \partial$ ля Ст.МПС,  $C_4 - \partial$ ля остальных МПС.

<sup>\*\*\*\*</sup> z выходов АЛУ и регистра Q.

<sup>\*\*\*\*\*</sup>  $\overline{R_3 \oplus F_3}$ .

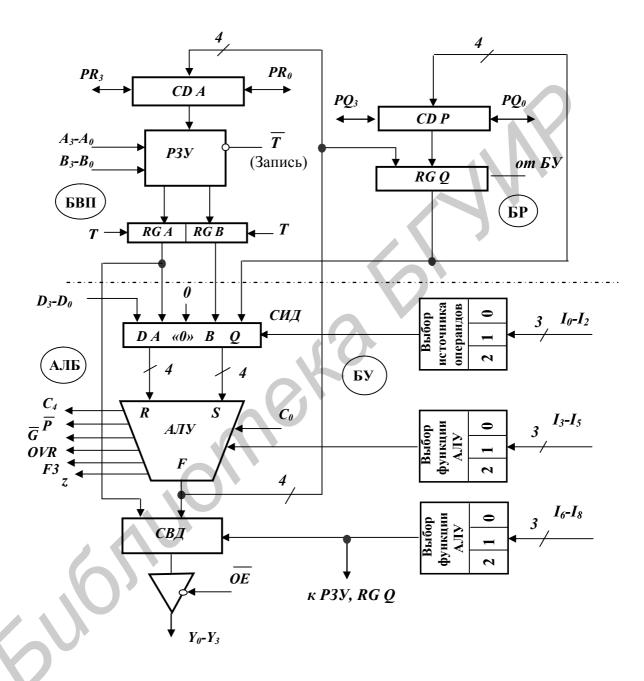

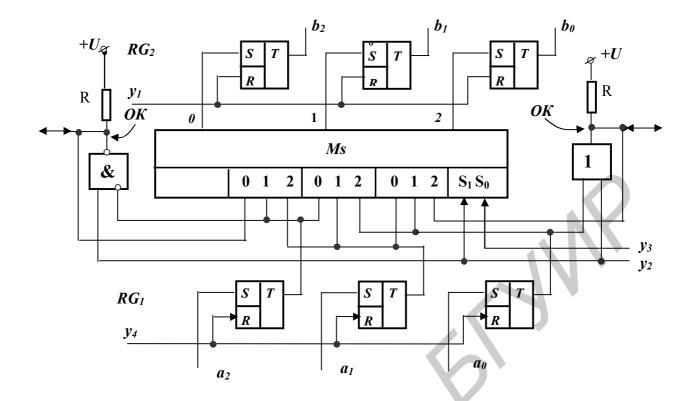

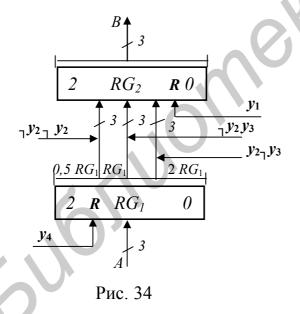

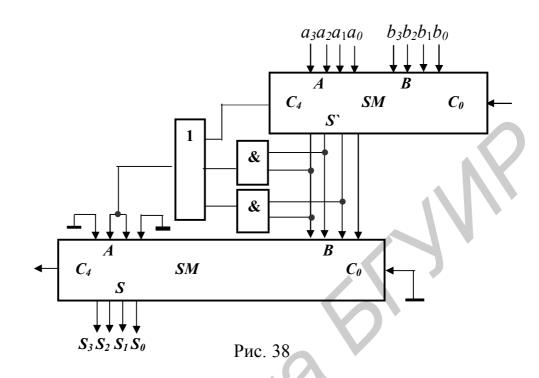

## 2.3. Построение операционных устройств на базе МПС К1804ВС1

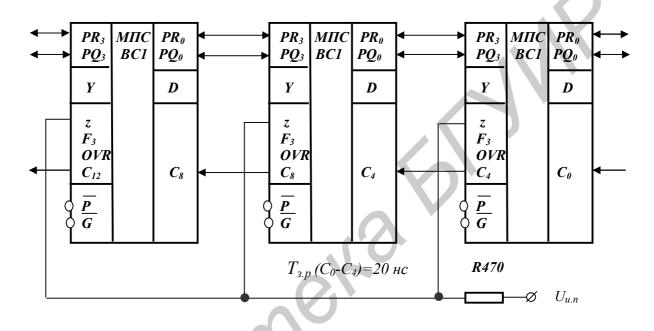

Требуемая разрядность операционного устройства обеспечивается объединением необходимого числа микропроцессорных секций. Например, если разрядность обрабатываемых в компьютере слов D равна 12, то схема вычислительного блока для данного частного случая будет иметь вид

Рис. 18

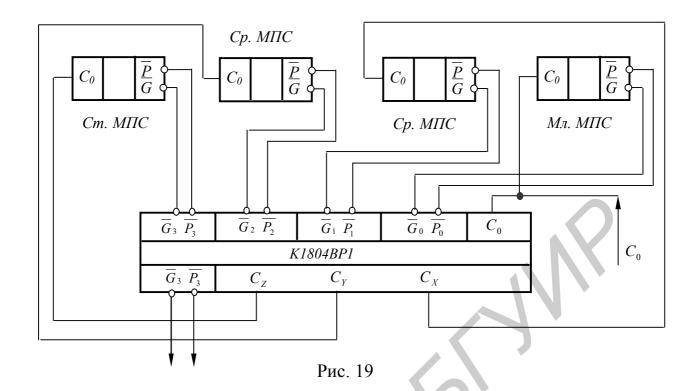

Приведенное соединение *МПС* обеспечивает последовательное распространение переноса от младших к старшим разрядам. В связи с этим при синтезе многоразрядных процессоров приходится *решать задачу* уменьшения времени задержки распространения переноса с целью повышения скорости выполнения арифметических операций. Для решения данной задачи при проектировании применяют схемы ускоренного переноса (*CУП*) *К1804ВР1* (рис. 19).

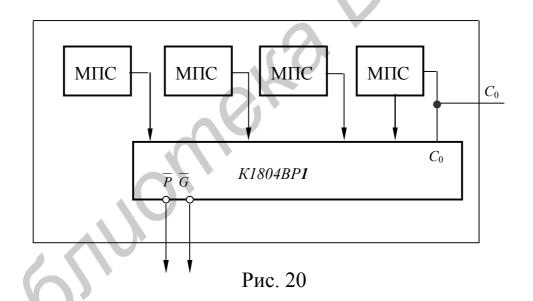

Выходы  $\overline{P}$ ,  $\overline{G}$  схемы ускоренного переноса используются для каскадного соединения нескольких *ИМС К1804ВР1*. В этом случае схема, приведенная на рис. 19, рассматривается как единый блок (рис. 20).

Рассмотрим схему распространения переноса в процессоре без блока СУП, а также при наличии данного быстродействующего модуля.

Для первой  $M\Pi C$  в блоке время задержки распространения определяется разницей во времени между моментом появления переноса  $C_4$  на выходе  $M\Pi C$  и моментом подачи двоичного кода на адресные входы P3V. Это время составляет величину примерно 70 нс. Для остальных секций время задержки распространения определяется равным  $t_{3.p}$  ( $C_0 - C_4$ )=20 нс. Таким образом, в схеме, приведенной на рис. 19,  $t_{3.p}$  переноса  $C_{12}$  на выходе 3-й микросхемы составит 70 + 20 + 20 = 110 нс.

В схеме с  $CУ\Pi$  аналогичный выход обозначен как  $C_z$ . Его время задержки определяется задержкой появления сигналов  $\overline{P}$ ,  $\overline{G}$   $M\Pi C$  относительно времени подачи адресов на входы P3V и задержкой в  $CY\Pi$ , равной 20  $\mu c$  (общая задержка для всех UMC). Итого:  $t_{3,p} = 79$   $\mu c$ .

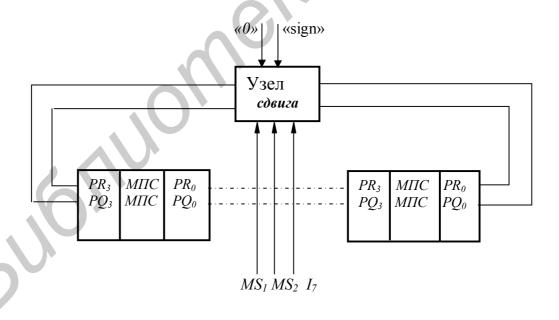

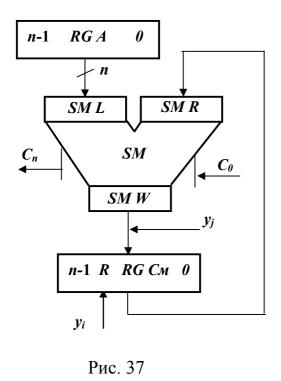

*Другая задача*, решаемая при объединении *МПС*, состоит в построении цепей передачи информации при организации сдвигов. Принципиально она может быть решена путем непосредственного соединения выходов  $PR_3$   $PQ_3$  младших МПС со входами  $PR_0$   $PQ_0$  старших секций. Однако в операционном устройстве остаются свободными соответствующие выходы младшей и старшей секций. Кроме того, решение ряда задач в процессоре может потребовать выполнения различных типов сдвигов. Каждая разновидность таких операций определяет различное соединение оставшихся свободными выводов или подачу на их входы определенной информации. Как правило, требуемые коммутации в БОД (блоке обработки данных) осуществляются с помощью специальной схемы — узла сдвига данных (рис. 21).

Рис. 21

На практике узел сдвигов может быть реализован с использованием мультиплексоров, управление которыми осуществляется сигналами  $MS_1$   $MS_2$ , а также сигналом микрокоманды  $I_7$ , который определяет направление сдвига. В

общем случае эти сигналы вносятся в структуру микрокоманды в специально отведенные разряды.

*Третья задача*, решаемая при построении операционных устройств, — это формирование и обработка слова состояния процессора, т.е. признаков, предназначенных для выполнения условных переходов.

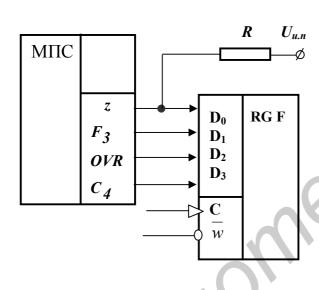

Слово состояния операционного устройства включает в себя сигналы  $PR_3$   $PQ_3$  на выходах старшей  $M\Pi C$ ,  $PR_0$   $PQ_0$  на выходах младшей  $M\Pi C$ , признаки z,  $F_3$ , OVR,  $C_4$ . Для хранения признаков в компьютерах используется регистр состояния RG C или регистр флагов (рис. 22).

Рис. 22

Запись признаков в регистр осуществляется по синхросигналу C на соответствующем входе RG F. Сигнал на входе  $\overline{w}$  используется для запрещения записи и организации ветвления в микропрограмме по нескольким условиям. При этом переход по каждому флагу осуществляется, как правило, с помощью отдельной микрокоманды. В связи с этим в течение всего времени ветвления по состоянию RG F (от n-й микро-

команды) вновь формируемые признаки результатов не запоминаются.

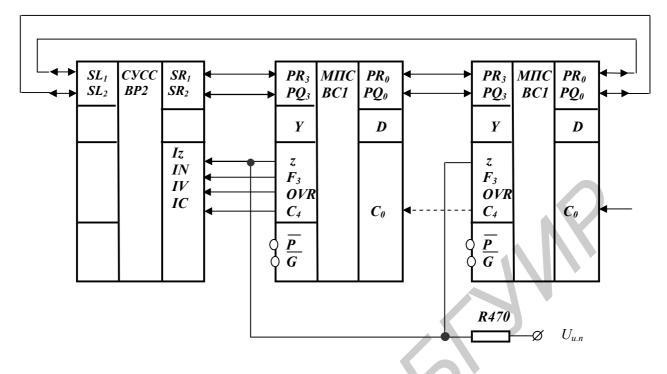

Для ускорения процесса ветвления и усложнения условия перехода используются специальные аппаратные средства, реализованные в виде *БИС К1804ВР2*. Данная схема предназначена для выполнения микроопераций сдвига и обработки слова состояния процессора. Схема соединения *СУСС* (схема управления состояниями и сдвигами) и *МПС* имеет вид, показанный на рис. 23.

БИС K1804BP2 осуществляет следующие функции:

1) формирует сигналы входного переноса в МПС и схему ускоренного переноса;

Рис. 23

- 2) выполняет арифметические, логические и циклические сдвиги чисел обычной и двойной длины;

- 3) осуществляет преобразование как целого  $CC\Pi$ , так и отдельных бит любого из 2 регистров состояния ( $RG\ F_1$  и  $RG\ F_2$ ), входящих в состав CYCC;

- 4) выполняет проверку за один такт одной из 16 различных комбинаций условий, поступающих из внутренних регистров состояния или из *МПС*.

# 2.4. Микропрограммирование МПС

Определение: элементарная функциональная операция, выполняемая за один тактовый интервал времени и приводимая в действие одним управляющим сигналом, называется микрооперацией. Соответственно совокупность микроопераций, выполняемых параллельно во времени, называют микрокомандой.

Выполнение всех действий в процессоре осуществляется в виде отработки множества команд (процессоры с фиксированной архитектурой) или микроко-

манд. В частности, микропроцессорная секция *К1804ВС1* функционирует под действием микрокоманд, хранящихся в управляющей памяти. При этом всю последовательность микрокоманд, предназначенных для реализации некоторого преобразования, называют микропрограммой.

Стандартная структура микрокоманды обычно включает в свой состав две основные части: операционную и адресную. Адресная часть используется при формировании адреса следующей микрокоманды. При этом в состав компьютера включается специальный блок (EMV), который позволяет выполнять различные действия над адресами.

Управление процессом преобразования данных осуществляется операционной частью микрокоманды. В этом случае микрооперации кодируются двоичными кодами и для кодирования используют три основных способа:

1. Вертикальное кодирование или микропрограммирование. Данный метод предполагает, что всей совокупности микроопераций присваиваются коды, образующие ряд целых чисел без знака. При отработке таких микрокоманд специальный дешифратор преобразует код микрокоманды в один управляющий сигнал, который и является сигналом микрооперации. Недостаток способа заключается: 1) в необходимости построения достаточно сложного дешифратора; 2) в увеличении длины микропрограммы (в одной микрокоманде содержится только одна микрооперация); 3) в отсутствии наглядности функционального назначения микрокоманды.

Число разрядов в операционной части при вертикальном микропрограм-мировании определяется по формуле

$$n_{o.4} = \operatorname{int} \log_2 m ,$$

где int — это ближайшее большее целое число; m — количество микроопераций.

2. Горизонтальное микропрограммирование. При данном способе каждому разряду операционной части микрокоманды ставится в соответствие определенная микрооперация. Наличие в разряде единицы говорит о том, что некото-

рая микрооперация выполняется, причем выполнение действий под управлением i разряда не зависит от состояния других j разрядов. Длина операционной части при горизонтальном микропрограммировании составляет число m, т.е. соответствует количеству микроопераций.

Достоинства метода: 1) возможность выполнения одновременно любого числа функционально совместимых микроопераций; 2) отсутствие схем дешифрации. Недостатки: 1) большая длина микрокоманды, достигающая в отдельных случаях сотен бит; 2) большая разрядность 3V микрокоманд или большая длительность выборки управляющих слов при малой разрядности 3V  $M\kappa$ .

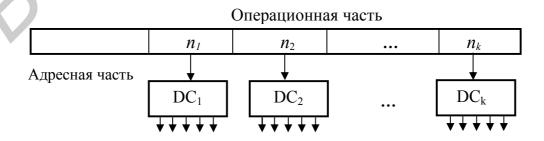

3. Смешанный способ микропрограммирования. В данном случае сочетаются горизонтальный и вертикальный способы кодирования, при этом множество микроопераций m разбивается на k подмножеств, а в составе микрокоманды каждому подмножеству выделяется свое поле:

$$m = \bigcup_{i=1}^k m_i.$$

Соответственно каждое поле имеет свое функциональное назначение, а микрооперации внутри подмножества (поля) кодируются вертикально.

Длина операционной части микрокоманды (рис. 24) при смешанном микропрограммировании определяется величиной

$$n_{o.4} = \sum_{i=1}^{k} \operatorname{int} \log_2 m_i ,$$

где k – число функциональных групп;  $m_i$  – число микроопераций в группе.

Рис. 24

Смешанный способ микропрограммирования применяется наиболее часто. Однако в данном случае требуется решать задачу разбиения множества всех микроопераций на непересекающиеся подмножества, т.е. микрооперации подмножества  $m_i$  не должны включаться в подмножество  $m_j$  и наоборот. Например:  $M\Pi C\ 1804BC1$  реализует 24 микрооперации, которые разбиты на 3 группы по 8 микроопераций. Каждая группа имеет свое функциональное назначение, принципиально отличное от преобразований, кодируемых в другой группе.

Теперь, с учетом методов кодирования микроопераций, рассмотрим процесс формирования структуры микрокоманды, достаточной для управления БИС К1804ВС1.

Итак, на первом этапе в состав микрокоманды включаются три поля для сигналов управления  $I_0 - I_8$ , что позволяет получить следующую структуру:

$$I_8 - I_6$$

$I_5 - I_3$   $I_2 - I_0$  ...  $RGMk$

Далее, будем учитывать наличие в архитектуре процессора  $POH_i$ , назначение которых состоит в хранении операндов или другой информации, используемых в вычислительном процессе. В общем случае номера регистров указываются явно, хотя допускается и неявное указание при адресации, например, регистра Q. Используя явный принцип адресации регистров, на данном этапе получаем следующую структуру  $RG\ Mk$ :

Рис. 26

Приведенная структура содержит основную информацию, необходимую для выполнения действий в *МПС*. Однако, как правило, в состав *RG Mk* включают ряд дополнительных сигналов или полей, необходимых для управления

другими структурными компонентами компьютера. К ним относят сигналы управления памятью, блоком микропрограммного управления, системой вводавывода, схемами внутреннего интерфейса.

Реализация адресной части микрокоманды зависит от используемого способа преобразования адресов и имеющегося комплекта аппаратных средств. Основные поля в этой части — это поле управления адресом следующей микрокоманды  $P_{i-1} - P_{0}$ , и поле адреса следующей микрокоманды  $BR_{j-1} - BR_{0}$ .

Поле управление адресом определяет источник адреса в  $\mathit{EMV}$ , который подключается к адресной шине, если выполнено некоторое заданное условие или безусловно. При выполнении безусловного перехода адрес микрокоманды, как правило, извлекается из разрядов поля  $\mathit{BR}_{j-1} - \mathit{BR}_0$ , где программируется предварительно.

Заполнение полей любой микрокоманды производится в соответствии с ориентацией ее на выполнение определенных действий. При этом множество микроопераций *МПС* допускает многовариантность кодовых наборов при выполнении одной и той же логической или арифметической операции.

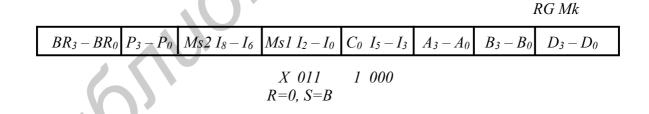

Для примера рассмотрим методику составления микрокоманды для управления данными в системе, использующей архитектуру процессорного комплекта K1804BC1.

Пусть требуется выполнить увеличение содержимого регистра общего назначения с номером 0000, входящего в состав  $M\Pi C$ . Структуру микрокоманды, достаточную для управления данной системой, будем считать априорно заданной в виде

|                 |               |                 |                 | R               | RG Mk       |           |             |

|-----------------|---------------|-----------------|-----------------|-----------------|-------------|-----------|-------------|

| $BR_3$ - $BR_0$ | $P_3$ - $P_0$ | $Ms2 I_8 - I_6$ | $Ms1 I_2 - I_0$ | $C_0 I_5 - I_3$ | $A_3 - A_0$ | $B_3-B_0$ | $D_3 - D_0$ |

Рис. 27

Здесь сигналы Ms2, Ms1 — это биты управления сдвигами (см. рис. 21);  $D_3$  —  $D_0$  — непосредственный операнд.

Пусть в начальный момент времени в регистре с адресом 0000 храниться нулевая константа. Тогда по табл. 2 (управление функцией  $A\Pi Y$ ) находим микрокод  $I_5 - I_3 = 000$ , определяющий операцию суммирования вида  $R + S + C_0$ , где R и S – входы  $A\Pi Y$   $M\Pi C$ . Полагая значение  $C_0$  равным «1», определим содержимое третьей тетрады RG Mk в виде (рис. 28).

Рис. 28

Далее определим источники информации на входах R и S AЛУ. Для простоты положим один из операндов, например по входу R, равным нулю. Тогда из табл. 1 (управление данными) выберем микрокод  $I_2 - I_0 = 011$ , соответствующий подаче на входы AЛУ содержимого POH по адресу из  $B_3 - B_0$  и технологически «зашитой» константы «0». Таким образом, в структуре RG Mk на данный момент будут определены 2 поля:

Рис. 29

Выберем в качестве приемника результата тот же POH, который является источником операнда. Адрес этого регистра указываем в поле B и определяем запись результата в P3V по форме  $F \rightarrow B$ . Это действие в  $M\Pi C$  производится под управлением микрокода  $I_8 - I_6 = 011$  (см. табл. 3). В общем случае номер регистра, адресуемый в  $RG\ Mk$ , может быть любой в диапазоне  $0-F_{16}(15_{10})$ . В частном

случае при  $POH_i$ =0000 поле  $B_3$  —  $B_0$  будет иметь значение 0000, а структура микрокоманды вид

$RG\ Mk$   $BR_3-BR_0\ P_3-P_0\ Ms2\ I_8-I_6\ Ms1\ I_2-I_0\ C_0\ I_5-I_3\ A_3-A_0\ B_3-B_0\ D_3-D_0$   $Aдресная\ часть$   $X\ 011\ X\ 011\ 1\ 000\ XXXX\ 0000\ XXXX$   $F{

ightarrow}B\ R=0,\ S=B\ R+S+C_0\ RG_0$

Рис. 30

Адресные линии  $A_3 - A_0$  в нашем примере не используются, поэтому здесь может быть указан произвольный код XXXX. Программирование адресной части требует специальных знаний и может быть рассмотрено после изучения темы «Устройства управления».

# 2.5. Процессоры с фиксированной архитектурой

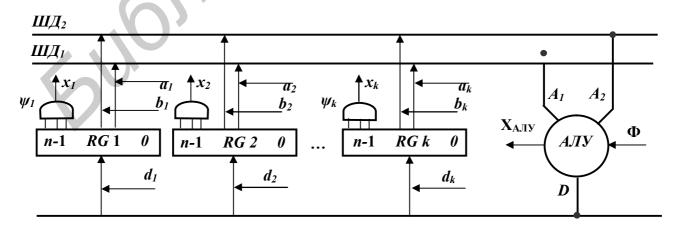

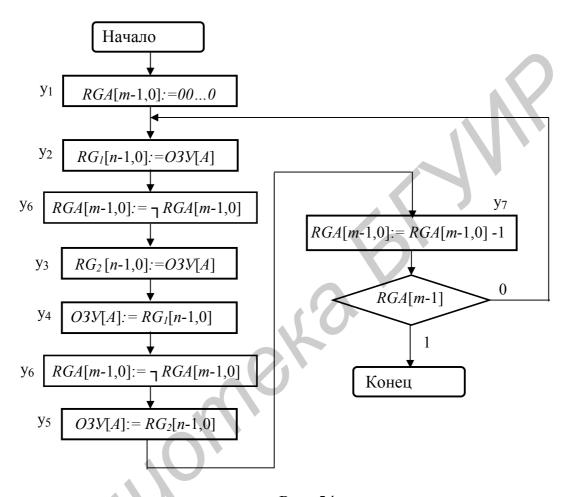

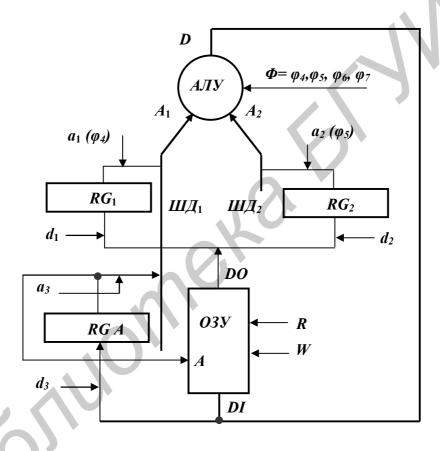

Деление структуры процессора на управляющий и операционный автоматы позволяет синтезировать исполнительную часть схемы в соответствии с некоторыми общими правилами.

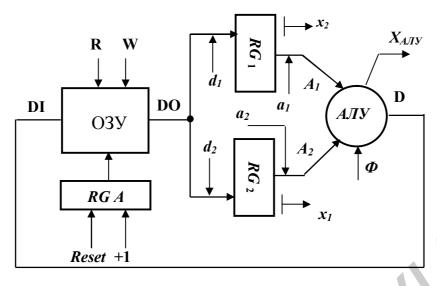

Исходные данные для построения OA формируются на основе выполняемых проектируемым процессором функций:

- 1) множество входных слов  $DI=\{DI_1, ..., DI_i\}$ , представляющих собой исходные операнды решаемой задачи;

- 2) множество выходных слов  $DO = \{DO_1, ..., DO_j\}$ , представляющих собой результаты операций;

- 3) множество внутренних слов  $R = \{R_1, ..., R_p\}$ , используемых для представления промежуточных результатов в процессе выполнения операций;

- 4) множество микрокоманд  $Y = \{y_1, ..., y_m\}$ , инициирующих преобразования над словами информации вида

$$y_q) R_u := \varphi_q \{R_t, ..., R_s\},$$

где  $\varphi_q$  – вычисляемая функция.

5) множество логических условий  $X=\{x_1, ..., x_l\}$ , где  $x_w= \coprod_z \{R_t, ..., R_s\}$ , z=1, 2, ..., l, а  $\coprod_z$  – булева функция.

Таким образом, функция операционного автомата считается заданной, если определены множества DI, DO, R, Y, X и алгоритмы преобразования данных.

Правило синтеза канонической структуры операционного автомата заключается в выполнении следующих действий:

- 1. Словам R, определяемым алгоритмом в качестве внутренних, ставятся в соответствие регистры DL длиной, равной длине слов. Если слово DL разделяется на поля, то в соответствующем регистре выделяются подрегистры, ориентированные на хранение содержимого подполей.

- 2. Словам DI, определяемым алгоритмом в качестве входных, ставятся в соответствие входы структурной схемы OA. Каждый вход соединяется с соответствующим регистром входной шиной.

- 3. Словам DO, которые определены как выходные, ставятся в соответствие выходы структурной схемы OA. Каждый выход соединяется с соответствующим регистром выходной шиной.

- 4. Каждой микрокоманде  $y_q$ , которая определяется оператором присваивания  $R_u := \varphi_q\{R_t, ..., R_s\}$ , ставится в соответствие комбинационная схема  $\varphi_q$ , причем входы этой схемы подключаются к регистрам  $R_t$ , ...,  $R_s$ , а выходы соединяются управляемой шиной с регистром  $R_u$ .

- 5. Каждому логическому условию  $x_w = \text{ш}_z\{R_t, ..., R_s\}$  ставится в соответствие комбинационная схема, входы которой соединяются с регистрами, а выходы отмечаются сигналами  $x_w$  и используются управляющим автоматом для ветвления программы. В некоторых случаях комбинационная схема может отсутствовать, если сигнал  $x_w$  является выходом одиночного разряда регистра.

# 2.6. Типовые решающие узлы ОА

Микрооперация передачи информации между регистрами встречается в компьютерных системах наиболее часто. Схемотехнически она реализуется с

помощью группы логических элементов, управляемых от схемы YA. На практике межрегистровые связи организуются с учетом реальных требований к быстродействию и сокращению затрат на реализацию компьютерных устройств.

Наиболее часто встречаются следующие схемы передачи:

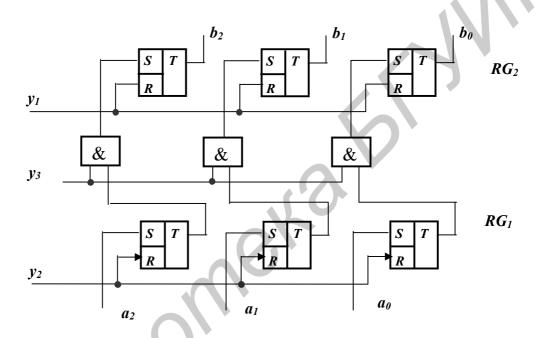

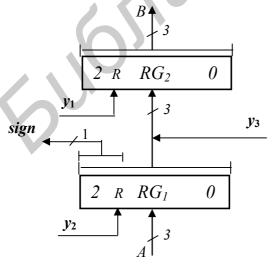

- 1. Прямая передача данных (рис. 31, 32).

- 2. Передача данных со сдвигом влево или вправо на один разряд (рис. 33, 34).

- 3. Передача данных с инверсией (образование обратного кода), со сдвигом на два разряда и т.д.

Рис. 31

Рис. 32

На структурных схемах межрегистровая передача изображается в виде шины передачи информации, управляемой сигналом микрооперации (см. рис. 32). В приведенной схеме реализуются микрооперации:

$$y_1$$

)  $RG_2[2,0]$ :=0

$y_2$ )  $RG_1[2,0]$ :=0

$y_3$ )  $RG_2[2,0]$ := $RG_1[2,0]$ .

Рис. 33

В схеме (см. рис. 33, 34) реализуются следующие механизмы сдвига (OK — открытый коллектор):

$$\overline{y}_2 y_3$$

)  $RG_2 [2,0] := RG_1 [2,0]$ ;

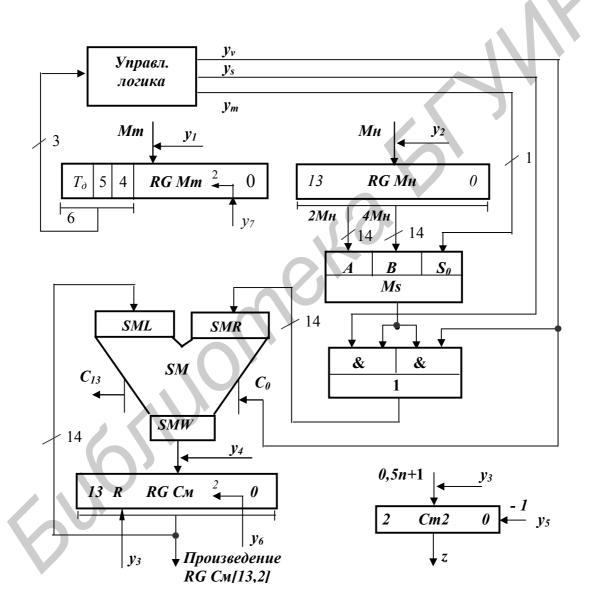

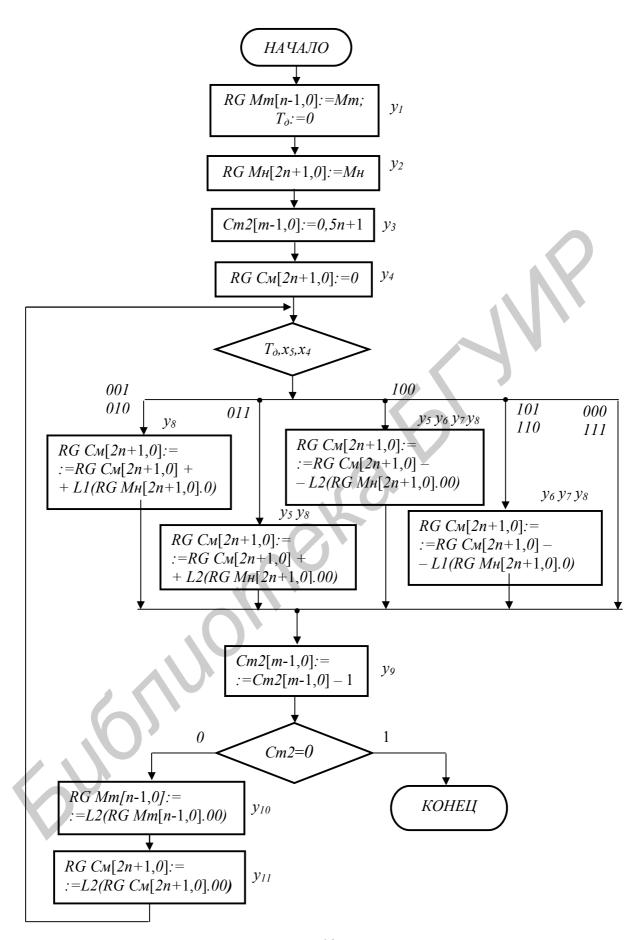

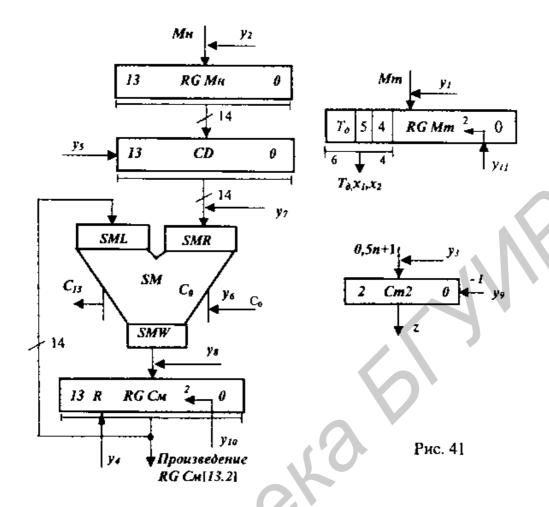

$\overline{y}_2 \overline{y}_3$ )  $RG_2 [2,0] := R1 (0.RG_1 [2,0])$ ;

$y_2 \overline{y}_3$ )  $RG_2 [2,0] := L1(RG_1 [2,0].0)$ ;

$y_2 y_3$ ) — запрещено.

$\overline{y}_i = \neg y_i$

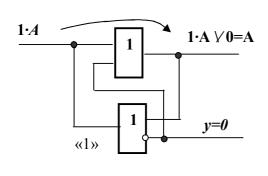

4. Для обмена данными в цифровых устройствах используют информационные каналы, которые называют шинами. В общем случае информация может передаваться по шине в виде последовательности бит по одной линии связи или же в виде слов по нескольким линиям. Соответственно и шины подразделяют на параллельные и последовательные. При построении схем часто используют шинные формирователи (ШФ), позволяющие осуществить двунаправленную передачу данных. Одна из реализаций ШФ имеет вид, показанный на рис. 35.

Рис. 35

В приведенной схеме выходы элементов коммутирующей логики должны быть выполнены по схеме с открытым коллектором. Тогда при y=0 на выходе нижнего элемента будет сформирована логическая единица. Потенциал логической единицы, умноженный на передаваемую информацию монтажно, дизъюнктивно складыва-

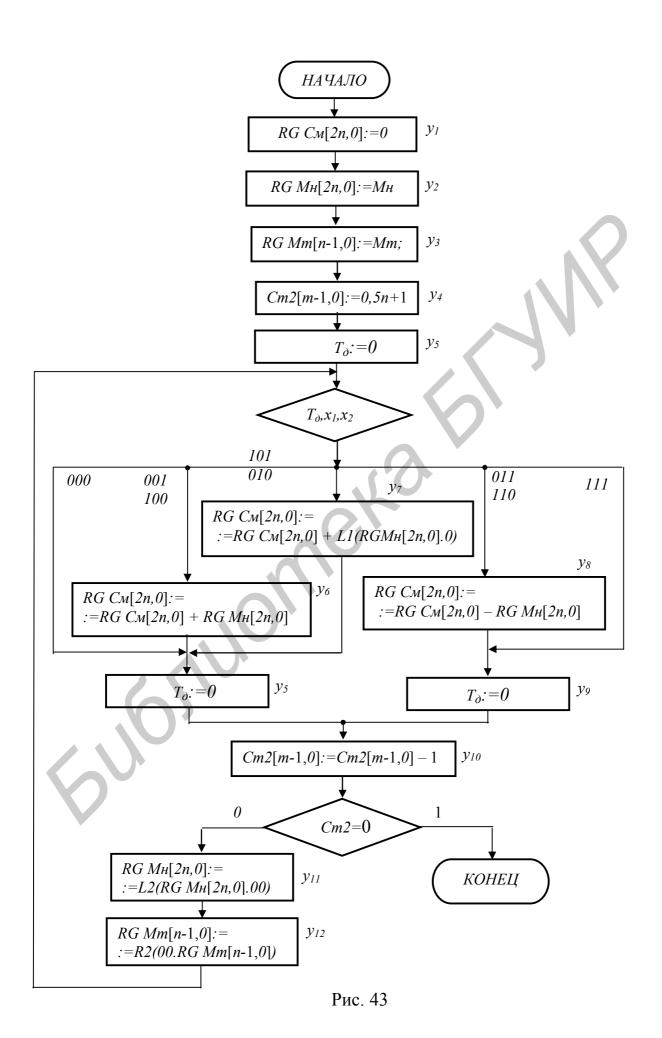

ется с сигналом y=0 на верхнем логическом элементе. В итоге в правую сторону по двунаправленной шине передается неискаженная информация.