# Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

Кафедра микро-и наноэлектроники

А.Г. Черных, С.В. Ригольд

# ТЕХНОЛОГИЧЕСКИЕ МАРШРУТЫ ИЗГОТОВЛЕНИЯ ИС

Лабораторный практикум по курсам «Маршрутная технология интегральных схем» и «Технологические процессы микроэлектроники» для студентов специальностей I-41 01 02 «Микро- и наноэлектронные технологии и системы» и I-41 01 03 «Квантовые информационные системы» всех форм обучения

# Рецензент: доц. кафедры ЭТТ БГУИР, канд. техн. наук В.Л. Ланин

### Черных А.Г.

Ч 49 Технологические маршруты изготовления ИС: Лаб. практикум по курсам «Маршрутная технология интегральных схем» и «Технологические процессы микроэлектроники» для студ. спец. I-41 01 02 «Микро- и наноэлектронные технологии и системы» и I-41 01 03 «Квантовые информационные системы» всех форм обуч. / А.Г. Черных, С.В. Ригольд. — Мн.: БГУИР, 2006.— 35 с.: ил.

ISBN 985-488-016-8

Лабораторный практикум позволяет получить представления о технологии изготовления биполярных ИС на ТТЛШ-элементах, КМОП ИС, полупроводниковых оперативных запоминающих устройств (ОЗУ) на п-канальных МОП структурах, СВЧ ИС, БиКМОП ИС, запоминающих элементов электрически стираемых программируемых постоянных запоминающих устройств (ЭСППЗУ), изучить технологические маршруты и контрольные операции после различных этапов изготовления ИС, приобрести практические навыки измерений параметров тестовых структур (ТС) и научиться проводить анализ технологического процесса по результатам измерений тестовых структур (ТС).

> УДК 621.382.8 (075.8) ББК 32.844.1 я 73

### СОДЕРЖАНИЕ

| 1 Цель работы                                                 | 4   |

|---------------------------------------------------------------|-----|

| 2 Последовательность выполнения работ                         |     |

| 3 Технологические маршруты изготовления ИС                    | 4   |

| 3.1 Технологический маршрут изготовления ИС на ТТЛШ-элементах |     |

| 3.2 Технологический маршрут изготовления ИС оперативного      |     |

| запоминающего устройства на n- канальных МОП структурах       | 6   |

| 3.3 Технологический маршрут изготовления КМОП ИС              | 8   |

| 3.4 Технологический маршрут изготовления СВЧ ИС               | .10 |

| 3.5 Технологический маршрут изготовления БиКМОП ИС            | .13 |

| 3.6 Технологический маршрут изготовления запоминающих         |     |

| элементов ЭСППЗУ                                              | .15 |

| 4 Тестовый контроль в технологии ИС                           | .17 |

| 4 Тестовый контроль в технологии ИС                           | .26 |

| 6 Требования техники безопасности при работе с                |     |

| измерительным комплексом                                      | .31 |

| измерительным комплексом                                      | .32 |

| Литература                                                    | .34 |

|                                                               |     |

## 1 ЦЕЛЬ РАБОТЫ

Получить представление о технологических процессах изготовления ИС; изучить технологический маршрут и контрольные операции после различных этапов изготовления ИС; приобрести практические навыки измерений параметров ТС и научиться проводить анализ технологического процесса по результатам измерений ТС.

В лабораторном практикуме рассматриваются шесть технологических маршрутов изготовления ИС:

- технологический маршрут изготовления ТТЛШ ИС;

- технологический маршрут изготовления ИС оперативного запоминающего устройства на n- канальных МОП структурах;

- технологический маршрут изготовления КМОП ИС;

- технологический маршрут изготовления СВЧ ИС;

- технологический маршрут изготовления БиКМОП ИС;

- технологический маршрут изготовления ЭСППЗУ

# 2 ПОСЛЕДОВАТЕЛЬНОСТЬ ВЫПОЛНЕНИЯ РАБОТ

- 2.1 Получить у преподавателя задание на выполнение лабораторной работы. Изучить требования по технике безопасности (раздел 6) и описание программы по проведению лабораторной работы на ЭВМ (раздел 5).

- 2.2 Ознакомиться с технологическим маршрутом изготовления ИС (раздел 3). Изучить технологический маршрут изготовления ИС на ЭВМ.

- 2.3 Изучить конструкцию тестовых модулей и топологию TC на кремниевых пластинах. Ознакомиться с основными TC для изучаемого технологического процесса изготовления ИС (раздел 4).

- 2.4 Приступить к выполнению экспериментальной части работы измерению основных параметров TC на ЭВМ.

- 2.5 После окончания измерений основных параметров ТС построить гистограммы распределения значений параметров ТС. Сопоставить реальные распределения значений параметров с оптимальными.

- 2.6 Представить результаты эксперимента на утверждение преподавателя.

- 2.7 Для защиты работы подготовить рекомендации по изменению технологического процесса изготовления ИС.

## 3 ТЕХНОЛОГИЧЕСКИЕ МАРШРУТЫ ИЗГОТОВЛЕНИЯ ИС

3.1 Технологический маршрут изготовления ИС на ТТЛШ-элементах

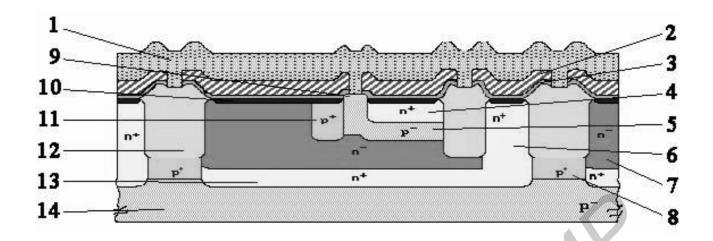

На рисунке 1 показано сечение структуры n-p-n-транзистора с диодом Шоттки, как наиболее характерного в ТТЛШ ИС. В качестве исходного материала используется подложка легированная примесью p-типа (КДБ-10). После окисления подложек проводят фотолитографию для создания скрытого n+-слоя. Для уменьшения сопротивления коллекторной области транзистора поверхно-

стное сопротивление скрытых слоев необходимо уменьшать, насколько это возможно. С этой целью скрытые слои подвергают сильному легированию. Такой сильнолегированный скрытый слой приводит к чрезмерной диффузии примеси в слаболегированный эпитаксиальный коллектор п-типа и может стать причиной образования дефектов в эпитаксиальном слое. При выборе примеси для легирования скрытого слоя обычно отдают предпочтение мышьяку или сурьме, а не фосфору, поскольку они имеют более низкий коэффициент диффузии. Скрытый слой получают путем ионной имплантации сурьмы с последующим термическим отжигом в окисляющей атмосфере. Затем окисел удаляют со всей поверхности подложки и проводят процессы для создания скрытого р+слоя, после чего выращивают эпитаксиальный слой. Эпитаксиальный слой проводимостью п-типа служит в качестве коллекторной области. Чем слабее легирован эпитаксиальный слой, тем меньшей емкостью обладает переход коллектор – база полупроводникового прибора. Эта емкость является основной паразитной емкостью, ограничивающей быстродействие биполярных транзисторов. Однако слишком низкий уровень легирования эпитаксиального слоя очень сложно проконтролировать в ходе эпитаксиального выращивания из-за процесса автолегирования примесью из скрытого слоя.

После создания скрытых слоев и эпитаксиального слоя переходят к процессам получения изоляции. Для этого на подложку с эпитаксиальным слоем последовательно наносят маскирующие слои  $SiO_2$  и  $Si_3N_4$  и проводят фотолитографию для локального окисления. Изолирующий окисел выращивается таким образом, чтобы его верхняя поверхность и поверхность кремния лежали в одной плоскости. С этой целью проводят травление кремния под локальный окисел. Термическое окисление осуществляют на глубину 1,6 мкм. Скрытый р-слой позволяет сократить толщину термического окисла, а также уменьшить микрорельеф поверхности. Одновременно скрытый р-слой исключает инверсионные каналы под локальным окислом, что повышает электрическую прочность изоляции.

После создания изоляции переходят к процессам создания активных областей транзистора. Базовая область создается в две стадии путем ионного легирования бором с использованием двух фотолитографий. Высоколегированная эмиттерная область получена ионным легированием фосфора с последующим кратковременным отжигом.

На заключительном этапе технологического маршрута проводятся процессы создания металлизации и диода Шоттки. В качестве металла для получения диода Шоттки на коллекторно-базовых областях используют силицид платины, который одновременно выполняет функции контактирующего слоя с областями эмиттера и коллектора. После напыления и вжигания платины, проводятся процессы создания металлизации, которая состоит из двух слоев: TiN - барьерного и Al - проводящего. Заключительным процессом получения микросхемы является пассивация, которая проводится с помощью низкотемпературных слоев  $SiO_2$  или  $Si_3N_4$ .

Рисунок 1 – Сечение структуры n-p-n-транзистора с диодом Шоттки:

1 — Пассивирующий слой (ФСС); 2 — Проводящий слой (Al); 3 — Барьерный слой (TiW); 4 — Эмиттер (P); 5 — База (B); 6 — Коллектор (P); 7 — Эпитаксиальный слой ; 8 — Скрытый слой (B); 9 — Защитный окисел; 10 — Металл для создания диода Шоттки (PtSi); 11 —  $p^+$  база (B); 12 — Изолирующий окисел; 13 — Скрытый слой (Sb); 14 — Исходная пластина

# 3.2 Технологический маршрут изготовления ИС оперативного запоминающего устройства на n-канальных МОП структурах

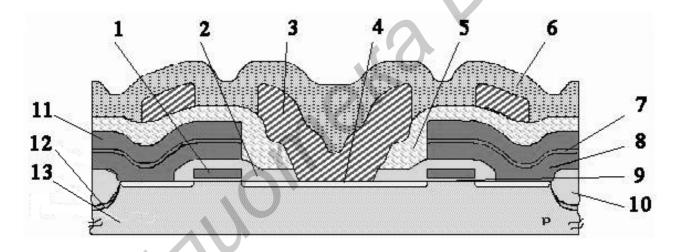

В ИС динамического оперативного запоминающего устройства (ДОЗУ) часто используется ячейка с так называемым этажерочным запоминающим конденсатором, выполненным в виде двух поликремниевых обкладок, разделенных тонким (8-25 нм) слоем диэлектрика. В качестве диэлектрического слоя чаще всего используется пленка нитрида кремния, характеризующаяся более высокой по сравнению с окислом кремния диэлектрической проницаемостью и обеспечивающая тем самым более высокую удельную емкость конденсатора. Результирующая структура ячейки имеет содержит четыре проводящих слоя: три слоя поликремния и один слой металлизации. В ДОЗУ емкостью 1-4М в качестве затворов передающих транзисторов, выполненных в первом проводящем слое, используется полилицид (поликремний, шунтированный слоем силицида тугоплавкого металла).

На рисунке 2 показано сечение структуры ячейки ДОЗУ 256К КР565357 с этажерочным конденсатором. В качестве подложки используется высокоомная кремниевая пластина типа КДБ-12. Это уменьшает емкости p-n-переходов структуры и коэффициент влияния подложки, обеспечивая повышение быстродействия структуры и стабильность пороговых напряжений транзисторов.

После формирования охранных р+ областей, предохраняющих канальную утечку между соседними активными областями и изоляции, проводится подлегирование приповерхностного слоя ионами В для регулировки порогового напряжения транзисторов. Подлегирование проводится через тонкий слой окисла кремния, предотвращающий загрязнение поверхности посторонними примесями в процессе имплантации, который впоследствии удаляется.

Затем производится подзатворное окисление, осаждение поликремния, фотолитография и формирование рисунка затворов.

Формирования исток-истоковых областей транзистора производится с помощью ионной имплантации As с использованием в качестве маски изолирующего окисла и затворов транзисторов. Фоторезист перед ионным легированием As снимается, что предотвращает его дополнительное задубливание вследствие большой дозы легирования и облегчает его снятие.

Затем на структуру со сформированным рисунком затворов наносится пиролитический окисел, в котором формируются контактные окна для обеспечения контакта между истоками транзисторов и нижней обкладкой запоминающего конденсатора.

На сформированный рисунок нижней обкладки конденсатора наносится пленка нитрида кремния и третий слой поликремния.

После формирования рисунка верхней обкладки конденсатора на поверхность структуры осаждается слой ФСС, оплавляемого при высокой температуре с целью обеспечения планарности. Завершающими этапами изготовления структуры являются формирование контактных окон к стоковым областям, металлизация и пассивация.

Рисунок 2 – Сечение структуры ячейки ДОЗУ:

1 — Поликремний; 2 — Планаризующий окисел; 3 — Металлизация (Al); 4 — Истокстоковые области (As); 5 — Борфосфорсиликатное стекло; 6 - Пассивирующий слой (ФСС); 7 —  $Si_3N_4$ ; 8 — Нижняя обкладка конденсатора (poli-Si); 9 — Подзатворный диэлектрик; 10 — Изолирующий окисел; 11 — Верхняя обкладка конденсатора (poli-Si); 12 — Охранная область; 13 — Исходная пластина

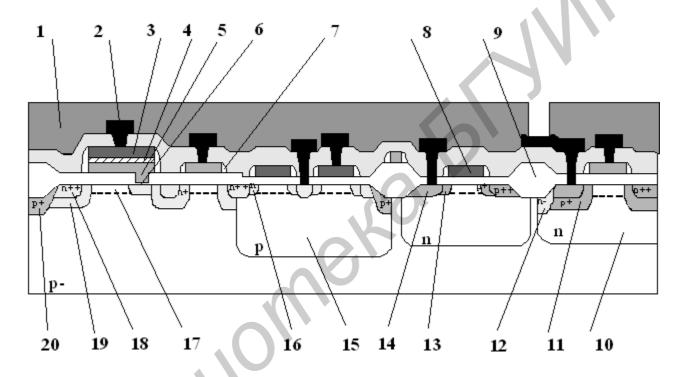

# 3.3 Технологический маршрут изготовления КМОП ИС

КМОП технология вобрала в себя все преимущества и достижения полупроводниковой планарной технологии и стала одной из наиболее важных технологических сфер формирования ИС.

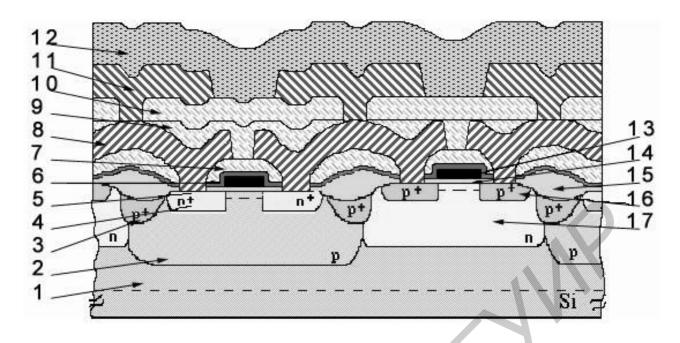

В лабораторной работе рассматривается технологический маршрут изготовления базового матричного кристалла (БМК) на КМОП структурах. Такой технологический маршрут характерен для многих современных ИС, включающих 200 тыс. и более транзисторных элементов. Основу элементной базы БМК составляют п- и р-канальные МОП-транзисторы с поликремниевым затвором, сформированные на одной положке.

В качестве материала подложки используется кремний монокристаллический КЭФ 4,5. Как n-, так и р-канальные транзисторы формируются в n- и р-карманах соответственно. Введение двух самосовмещенных карманов необходимо для повышения устойчивости микросхем к защелкиванию и улучшения их параметров.

Карман р-типа формируется ионным легированием бора с энергией 40 кэВ и дозой 2,0 мкКл/см². Карман п-типа формируется ионным легированием фосфора с энергией 75 кэВ и дозой 0,5мкмКл/см². Разгонка карманов происходит при 1200 °С в течение 2 часов в атмосфере кислорода и 8 часов в атмосфере аргона. Охранные области формируются ионным легированием бора с энергией 100 кэВ и дозой 250 мкмКл/см2. Локальный окисел для LOKOS-изоляции (1,0 мкм) выращивается при повышенном давлении с использованием маски из нитрида кремния. Технологический маршрут рассчитан для проектных норм на топологию 2 мкм, в связи с чем толщина подзатворного диэлектрика выбрана 0,027 мкм. Соответственно эффективная длина канала для п-канального транзистора составляет 1,1 мкм, а р-канального - 1,4 мкм.

В качестве подзатворного диэлектрика используется пирогенный окисел. Затвор формируется из поликремния (0,45 мкм) путем анизотропного плазмохимического травления. Истоки (стоки) n+ создаются ионным легированием фосфора с энергией 40 кэВ и дозой 1000 мкмКл/см². Истоки (стоки) p+ создаются ионным легированием бора с энергией 30 кэВ и дозой 300 мкмКл/см². Затем проводится активация примеси при 850°C в сухом кислороде в течении 30 минут.

Так как концентрация и р-кармане достаточно низкая, пороговое напряжение п-канальных транзисторов зависит в основном от дозы ионов бора, имплантированных в канал. Пороговое напряжение р-канального транзистора определяется в основном уровнем легирования в области канала. Величины пороговых напряжений р- и п-канальных транзисторов составляют 1,1+0,2 В.

Удельные поверхностные сопротивления слоев составляют:

первый слой металлизации (материал Al+1%Si) — 0,1Om/квадрат при толщине слоя 0,6-0,8 мкм; 2) второй слой металлизации — 0,1 Om/квадрат при толщине слоя 1,0-1,1 мкм; 3) кремний поликристаллический — 30 Om/квадрат;

4) кремний n+-60; 5) кремний p+-10; 6) р-карман -2500; 7) n-карман -4000Ом/квадрат.

Для получения требуемых размеров элементов необходимо иметь соответствующие точности литографических процессов. С этой целью можно использовать проекционную фотолитографию. Точность проведения фотолитографических операций определяется прежде всего качеством шаблонов и возможностями установок экспонирования и мультипликации.

В конструкции микросхем используется двухуровневая металлизация с шагом в слоях – 6 мкм (шина – 4,2 мкм, зазор – 1,8 мкм). Столь малые топологические размеры требуют максимальной планаризации рельефа. В качестве первого межслойного диэлектрика используется борофосфорно—силикатное стекло (БФСС) толщиной 0,6мкм. Достоинством БФСС является его низкая температура оплавления (850 °C), что позволяет позволить планаризацию как по затвору, так и после травления контактных окон. При травлении происходит "подтрав" кремния в области контактных окон (на глубину 0,1 мкм), что приводит к снижению поверхностной концентрации в п-области и, как следствие, к увеличению контактного сопротивления. С целью исключения данного выхода брака необходимо проводить дополнительное легирование п-области с использованием дополнительной литографии.

С целью исключения обрывов по второму слою металла проводится дополнительная планаризация методом сквозного протравливания. Метод заключается в следующем: после создания первого уровня металлизации наносится фосфорно—силикатное (ФСС) (0,8 мкм) и разжиженный фоторезист. После сушки и задубливания фоторезиста проводится плазмохимическое травление фоторезиста и ФСС, причем режимы травления подбираются таким образом, чтобы скорость травления фоторезиста и ФСС были одинаковыми. Наилучшая планаризация получается, когда травление проводится до остаточной толщины ФСС (0,3 мкм).

После формирования металлизации проводит пассивацию кристаллов для защиты структур от механических и климатических воздействий. На рисунке 3 показано сечение КМОП структуры.

Рисунок 3 – Сечение КМОП структуры

1 – Исходная подложка; 2 – Карман р-типа; 3 – Охранная область; 4 – Исток-стоковые области; 5 – Контактная область 6 – ФСС; 7 – Борфосфорсиликатное стекло; 8 – Первый слой металлизации; 9 – Планаризирующий слой ФСС; 10 – Межуровневый диэлектрик;

11 – Второй слой металлизации; 12 – Пассивирующий слой; 13 – poli-Si;

14 – Подзатворный окисел; 15 – Изолирующий окисел; 16 – Исток-стоковые области; 17 – Карман n-типа

# 3.4 Технологический маршрут изготовления СВЧ ИС

Цифровые арсенид-галлиевые ИС изготавливаются по различным технологическим вариантам, которые отличаются главным образом методами создания легированных и изолирующих областей. Когда для изоляции используется мезотехнология, возникают проблемы, связанные с паразитными емкостями, увеличением длины межсоединений и снижением их надежности на ступеньках, образующихся при травлении мезоструктур. Другой технологический вариант предусматривает создание планарной структуры с изоляцией путем имплантации ионов бора или кислорода. При этом активные слои могут изготавливаться различными методами. Для снижения сопротивления контактов может применяться локальная имплантация доноров в приконтактные области.

Еще один вариант технологии изготовления планарной структуры ИС использует локальную имплантацию непосредственно в высокоомную подложку, как для создания активных областей приборов, так и для изготовления сильнолегированных областей. Основными достоинствами этой технологии являются возможность оптимизации профиля распределения примеси в активных областях схем и снижение паразитных сопротивлений в транзисторах и диодах за счет создания сильнолегированных областей.

Технология арсенид-галлиевых СВЧ ИС весьма отличается от технологии кремниевых приборов. Она обладает рядом особенностей, в числе которых 10

можно назвать возможность создания спиральных структур индуктивности, монолитных конденсаторов и перемычек с воздушным зазором. Активные элементы в СВЧ ИС создаются как и в цифровых ИС, методами эпитаксии или ионного легирования.

Важнейшими блоками при изготовлении СВЧ ИС являются омический контакт (ОК) и барьер Шоттки (БШ).

Изготовление ОК с малым сопротивлением представляет более сложную задачу, чем для Si, вследствие химической активности материала и трудностей создания несплавных контактов к GaAs. Наиболее распространенный метод формирования ОК заключается в вакуумном осаждении двухслойной системы. Первый слой обеспечивает химическую стойкость, а второй служит для образования n+ слоя. Наиболее часто используют систему Au-Ge в комбинации с поверхностным слоем из никеля, который служит для предотвращения каплеобразования в процессе вжигания. Полученный контакт вначале обладает запирающими свойствами. Для их устранения проводят нагрев до эвтектической температуры (425°C) в инертной атмосфере или в водороде с образованием жидкой фазы на поверхности раздела и последующей кристаллизацией. Полученные таким образом контакты обладают удельным сопротивлением менее 10 Ом-см. Снижения величины удельного сопротивления ОК можно добиться путем лазерного или электронно-лучевого воздействия на металлические и ионнолегированные слои. С применением импульсной обработки возможно создание стабильных и надежных контактов к GaAs на основе тугоплавких металлов, например Ti-Pt-Au. Металлизация таких контактов обычно формируется взрывным способом.

Важным этапом в технологии создания СВЧ ИС является формирование БШ. Высокие значения БШ в GaAs, независимость высоты этих барьеров от большинства параметров и способов подготовки поверхности делают GaAs особенно привлекательным для создания ИС на полевых транзисторах с барьером Шотки (ПТШ).

Наиболее распространенным материалом затвора является Al, часто используют Ti-Au, Ti-Pt-Au. При использовании Ti между ним и Au вводят барьерный слой Mo, W, Ni или Pd, предотвращающих диффузию Au через Ti в GaAs. Выбор металла затвора определяется необходимостью обеспечить близкие значения тепловых коэффициентов линейного расширения GaAs и металла. БШ создают методом взрывной литографии. В качестве маски обычно используют  $Si_3N_4$ ,  $SiO_2$ , фоторезист.

БШ создают в специальном углублении, что увеличивает его эффективность. Необходимо отметить, что при создании углубления формируется канал ПТШ с заданным напряжением отсечки ( $U_{\rm orc}$ ). Углубленный на 0,2-0,3 мкм затвор позволяет снизить коэффициент шума на 2-3 dB. Обычно углубление создается химическим травлением в сернокислом или перикисно-аммиачном травителях. Химическое травление должно обеспечивать низкие скорости травления и однородный фронт травления.

После затвора вакуумным напылением и "взрывной" литографией создают первый слой металлизации с одновременным формированием индуктивности и нижних обкладок конденсатора. При этом одновременно увеличивают толщину металлизации истоков-стоков, уменьшая их распределенное сопротивление. В качестве диэлектрика для конденсаторов используют SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> и другие диэлектрики. Верхняя обкладка конденсаторов формируется со вторым слоем металлизации - разводкой. В качестве металлизации разводки используют V-Al, Ti-Au, Cr-Au, Ti-Pt-Au. В многозатворных ПТШ разводку истоковстоков осуществляют, как правило, воздушными мостами.

Верхние обкладки конденсаторов для устранения влияния обрыва диэлектрика на первом уровне металлизации также разводят "мостами". При создании "мостов" применяют гальваническое выращивание Au с последующим его травлением и вымыванием фоторезиста из-под перемычек.

Большинство схемотехнических решений СВЧ ИС предполагает заземление истоков по ВЧ. Наиболее распространены два типа заземления - через торец кристалла и через сквозное отверстие. Первый подход наиболее прост в технологическом отношении и обеспечивает высокий выход годных. Однако ПТШ при таком подходе надо располагать по краю кристалла из соображений минимальной индуктивности выводов. Сквозное заземление характеризуется меньшей индуктивностью и облегчает проектирование топологии. Для реализации сквозного заземления подложка утоняется химическим травлением до 100 мкм. Затем химическим или плазменным травлением в ней создают отверстие, которое металлизируют гальваническим Аи, контактирующим с планарной стороны с истоками ПТШ. Заключительным этапом при создании ПТШ является пассивация кристалла (рис.4).

Рисунок 4 – Сечение структуры транзистора GaAs ИС:

1 — Эпитаксиальный слой; 2 — Затвор; 3 — Контактный слой; 4 — Металлизация — первый слой; 5 — Слой Аu; 6 — Воздушный мост; 7 — Верхняя обкладка конденсатора; 8 — Диэлектрик; 9 — Нижняя обкладка конденсатора; 10 — Окисел; 11 — Утонение подложки; 12 — Эпитаксиальный слой n+ слой; 13 — Эпитаксиальный слой; 14 — As Ga-пластина; 15 — Второй слой Au

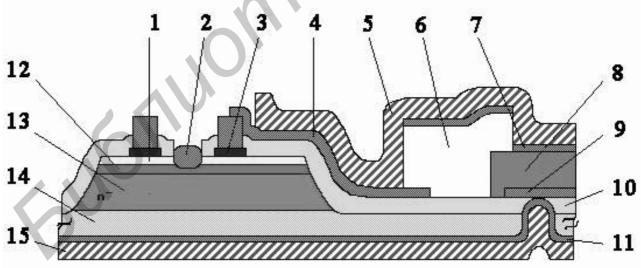

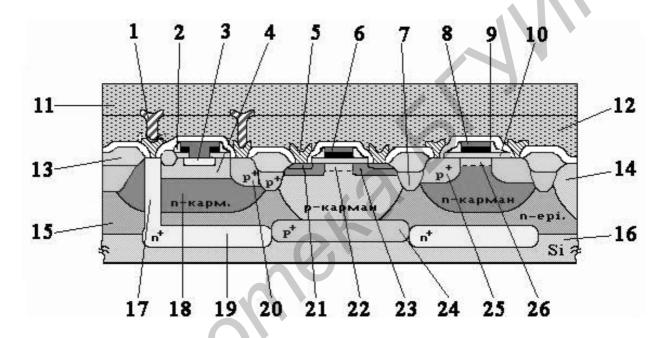

## 3.5 Технологический маршрут изготовления БиКМОП ИС

При разработке БиКМОП-технологии обычно используются отработанные блоки биполярных и КМОП-технологий, апробированные конструктивнотехнологические решения, позволяющие получить единый процесс. Подобный подход позволяет создавать различные типы БиКМОП-структур.

В лабораторной работе рассматривается технологический маршрут изготовления БиКМОП ИС, применяемый в производстве быстродействующих цифровых схем. Для реализации данного маршрута необходимо использовать 17 процессов фотолитографий, 14 операций ионного легирования, 9 процессов нанесения диэлектрических слоев и поликремния. Такой маршрут характерен для многих современных ИС с высокой степенью интеграции.

В качестве материала подложки используется кремний монокристаллический с ориентацией <100> и р-легированием. Эпитаксиальный слой 2,15 КЭФ 4,5 выращивается поверх  $n^+$  и р-скрытых слоев. Скрытый  $n^+$ -слой служит коллектором вертикального n-р-n-транзистора и подавляет эффект защелкивания в р-канальных МОП-транзисторах. Формируется слой ионным внедрением Sb (энергия E=60 кэB, доза 250 мкКл/см) с последующей разгонкой при t=1220 °C в течение 1,5 ч в кислородной атмосфере. Слаболегированные области t0 слоя обеспечивают изоляцию элементов за счет смыкания t0 с t0

Карманы n- и p-типа формируются самосовмещением с использованием одной операции маскирования. Режимы ионного легирования для карманов p-типа - D=0,3 мкКл/см, E=75кэB. Разгонка карманов происходит в атмосфере  $N_2$  в течение 1 ч при t=1150°C.

Отдельными операциями маскирования и легирования формируются области глубокого  $n^+$ -коллектора активной базы p-резисторов, что обеспечивает улучшение характеристики биполярного транзистора.

Поликремниевые эмиттеры и n-затворы МОП-транзисторов формируются в одном процессе за один этап маскирования. Особенности формирования стокистоковых областей определяются топологическими размерами затворов МОП-транзисторов. Для n-МОП длина затвора 1,4 мкм, а для p-МОП - 1,8 мкм. Поэтому для исключения эффекта короткого канала на n-МОП-транзисторах после формирования затворов формируются области n-истоков. Затем на затворах формируются окисные боковые стенки, которыми задаются границы легирования  $n^+$ -истоков. Граница  $p^+$ -истоковый областей задается затворами. Толщина подзатворного диэлектрика 0,03мкм. Локальный окисел для LOCOS изоляции 0,8 мкм выращивается при повышенном давлении с использованием маски  $Si_3N_4$ .

В технологии применяется двухуровневая система металлизации. Особенности формирования первого уровня металлизации определяются использованием поликристалического эмиттера. Для уменьшения деградации коэффи-

циента усиления применяется система TiN+AlSi (d=0,18+0,4 мкм). Второй слой металлизации — система AlSi (1,2 мкм). Применение двухуровневой металлизации требует максимальной планаризации рельефа. В качестве первого диэлектрика используется БФСС. Это позволяет провести планаризацию рельефа за счет низкотемпературного оплавления (850 °C, 45 мин в кислородной атмосфере). Межслойным диэлектриком между первым и вторым слоями металла является либо планаризованное ФСС либо полиамид. При применении в качестве межслойного диэлектрика ФСС, планаризацию проводят методом сквозного протравливания. Для защиты структуры от механических и климатических воздействий проводят пассивацию с использованием пленки полиамида (рисунок 5).

Рисунок 5 – Сечение структуры БиКМОП-элемента ИС:

1 — Второй слой металлизации; 2 — Планаризующий окисел; 3 — Эмиттер биполярного транзистора; 4 — База; 5 — Первый слой металлизации; 6 — Первый слой poli-Si; 7 — Охранный слой; 8 — Второй слой poli-Si; 9 — Борфосфорсиликатное стекло; 10 — Подзатворный окисел; 11 — Пассивирующий слой; 12 — Межуровневый диэлектрик; 13 — Изолирующий окисел; 14 — Карман р-типа; 15 — Эпитаксиальный слой; 16 — Исходная пластина; 17 — Коллектор;

14 — Карман р-типа; 15 — Эпитаксиальный слой; 16 — Исходная пластина; 17 — Коллектор; 18 — п-карман; 19 — Скрытый п+ слой; 20 — Скрытый р+ слой; 21 — п++ приконтактная область; 22 — Подлегирование канала; 23 — Исток-стоковые области; 24 — Скрытый р+ слой;

25 – Исток-стоковые области; 26 – Подлегирование канала

# 3.6 Технологический маршрут изготовления запоминающих элементов ЭСППЗУ

Приборы со встроенными блоками электрически стираемых программируемых постоянных запоминающих устройств (EPROM) в настоящее время являются одними из наиболее используемых типов микросхем. Эти приборы применяются в самых различных устройствах: в кредитных и телефонных карточках, микросхемах для компьютерной техники и в микрокалькуляторах, в электронных часах и оборудовании для телефонии, в торговле и средствах связи. Включение в состав микроконтроллеров блоков энергонезависимой памяти расширяет возможности этого класса микросхем.

Преимуществом таких устройств является то, что информация может храниться в них порядка 10 лет, а стирание информации производится ультрафиолетовым излучением или рентгеновским излучением, туннелированием (в зависимости от технологии и структуры ячейки).

Большое распространение имеют ЭСППЗУ с параллельным стиранием (FLASH ЭСППЗУ), в которых возможна электрическая запись каждой ячейки в отдельности, а электрическое стирание осуществляется для всего кристалла одновременно. В настоящее время около 70% микросхем FLASH памяти разработаны на основе запоминающих ячеек ETOX (EPR0M tunnel oxide).

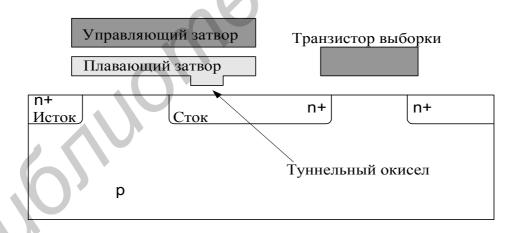

Запоминающие элементы ЭСППЗУ типа ETOX — один из наиболее распространенных базовых элементов энергонезависимой памяти. Структура двухтранзисторной запоминающей ячейки ЭСППЗУ приведена на рисунке 6.

Рисунок 6 – Структура запоминающей ячейки ЭСППЗУ

Толщина окисла между плавающим затвором и подложкой составляет около 10 нм, следовательно, возможно туннелирование электронов с плавающего затвора на исток, если к истоку приложено высокое напряжение при заземленном управляющем затворе. Поэтому пробивное напряжение истокового перехода должно быть достаточно велико. Области истока и стока FLASH ячейки формируются раздельно. В качестве межслойного диэлектрика между

управляющим и плавающим затвором используется структура ONO (окиселнитрид – окисел).

Запрограммированное состояние соответствует наличию отрицательного заряда на плавающем затворе и высокому пороговому напряжению запоминающего транзистора. Для реализации такого состояния к управляющему затвору ячейки прикладывается высокое напряжение при заземленных электродах истока, стока и подложки.

В стертом состоянии на плавающем затворе имеется небольшой положительный заряд, приводящий к отрицательному пороговому напряжению, и к отпиранию запоминающего транзистора. Для реализации такого состояния к управляющему затвору ячейки прикладывается нулевое смещение, электроды истока и подложки заземляются, а к электроду стока прикладывается высокое напряжение.

Механизм программирования — записи запоминающей ячейки идет за счет инжекции «горячих» электронов из канала транзистора на плавающий затвор. Программирование запоминающей ячейки осуществляется при подаче на управляющий затвор напряжения программирования  $U_3=12B$ . Напряжение стока варьировалось от 6B до 12B. Длительность импульса программирования составляла  $t=10^{-4}$  с,  $5\cdot10^{-4}$ с и  $10^{-3}$ с.

Стирание запоминающей ячейки осуществляется при подаче на управляющий затвор напряжения U3=0B. Напряжение стока варьировалось от 9B до 11B. Длительность импульса программирования составляла  $t=10^{-3}$  c,  $5\cdot10^{-3}$  c,  $10^{-2}$  c и  $5\cdot10^{-2}$  c.

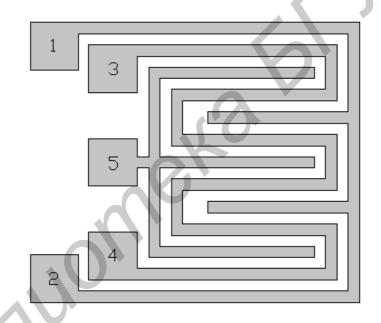

На рисунке 7 приведена топология тестового запоминающего элемента ЭСППЗУ – транзистора с плавающим затвором.

Рисунок 7 – Топология тестового запоминающего элемента ЭСППЗУ:

L – длина канала запоминающего транзистора, определяется слоем «n – сток-1» ;

W – ширина запоминающего транзистора, определяется слоем «разделение»;

P – выход плавающего затвора на локальный окисел; A – длина плавающего затвора; B – ширина плавающего затвора

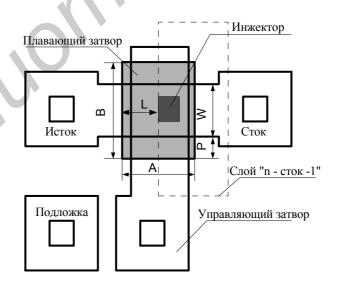

Эволюция формирования структуры ЭСППЗУ показана в ознакомительной части программы. Технологический маршрут изготовления ЭСППЗУ включает 30 фотолитографий и позволяет одновременно сформировать высоковольтную часть блока управления ЭСППЗУ, блок запоминающих ячеек ЭСППЗУ и низковольтную часть. Затворы высоковольтных транзисторов и плавающие затворы запоминающих ячеек расположены в первом уровне поликремния на подзатворном окисле толщиной 35нм, затворы низковольтных транзисторов и управляющие затворы запоминающих ячеек расположены во втором уровне поликремния. Толщина подзатворного окисла в низковольтной части составляет 16нм, толщина межслойного диэлектрика — 35нм. Сечение структуры ячейки ЭСППЗУ показано на рисунке 8.

Рисунок 8 – Сечение структуры ячейки ЭСППЗУ

1 — Пассивирующий слой; 2 — Металлизация; 3 — Второй слой poli-Si, управляющий затвор; 4 — Межслойный Si<sub>3</sub>N<sub>4</sub>; 5 — Первый слой poli-Si, плавающий затвор; 6 — Туннельный окисел; 7 — Планаризующий окисел; 8 - Второй слой poli-Si 9 — Изоляционный окисел; 10 — Карман п-типа; 11 — Слаболегированные стоки; 12 — Охранная область; 13 — Слаболегированные стоки; 14 — Сильнолегированные стоки; 15 — Карман р-типа; 16 — Слаболегированные стоки; 17 — Подлегирование канала; 18 — Сильнолегированные стоки; 19 — Слаболегированные стоки; 20 — Охранная область

# 4 ТЕСТОВЫЙ КОНТРОЛЬ В ТЕХНОЛОГИИ ИС

Тестовую структуру (TC) можно определить как микроэлектронный прибор, используемый для измерения параметров физической структуры ИС и изготавливаемый одновременно с рабочими схемами. ТС разделяют по назначению на функциональные (предназначены для исследования функциональных

свойств компонентов после окончания технологического цикла) и параметрические (предназначены для исследования физических параметров во время технологического цикла). ТС могут быть использованы для:

- оценки качества полупроводниковых материалов;

- оценки и управления воспроизводимостью техпроцесса;

- измерения параметров схем и приборов;

- получение данных о случайных отказах;

- оценки оборудования и проверки квалификации операторов.

Применение ТС позволяет автоматизировать операции контроля на основе использования сравнительно простых зондовых устройств и несложных алгоритмов пересчета данных. В процессе такого контроля измеряются параметры ТС, вычисляются статистические характеристики их распределения, которые могут быть использованы для оценки качества выполнения технологических операций и в дальнейшем для организации автоматических систем управления технологическими процессами на основе специализированных информационно-измерительных компонентов, управляемых ЭВМ

Размещению ТС на пластине придается большое значение, поскольку это определяет количество изготовленных ТС относительно рабочих кристаллов для получения более достоверной тестовой информации, а кроме того, связано с использованием рабочей площади пластины, что отображается на экономикотехнологических параметрах приборов.

Для операционного контроля наиболее широко используются TC, расположенные на краях рабочего кристалла микросхем. Для общего контроля в связи со сложностью технологии и большим количеством контролируемых параметров применяют тестовый модуль, который размещается среди рабочих кристаллов на пластине. В ряде случаев тестовый модуль располагают по всей площади пластины. Такое размещение дает возможность определить и локализовать некоторые виды отказов в микросхемах, а также определить плотность дефектов по пластине. Такой подход к организации размещения TC при всех достоинствах имеет недостаток — уменьшается размер активной части пластины.

Тестовые структуры должны обеспечивать анализ всех отказов, встречающихся в ИС. При этом каждый вид отказа исследуется с помощью специальной ТС, которая выявляет только определенный механизм отказа.С точки зрения контролируемых параметров ТС можно разделить на пять групп.

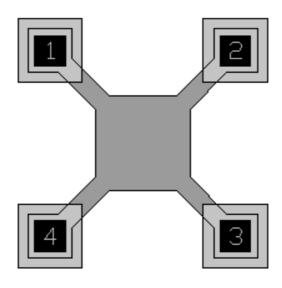

Первая группа — TC для контроля удельного поверхностного сопротивления  $(R_s)$ . Это, например, необходимо для оценки пространственной однородности легированных, а также проводящих и эпитаксиальных слоев. Относительная простота определения  $R_s$  делает его полезным при оценке характеристик технологического процесса. Наиболее распространенной TC является классический резистор Ван дер Пау, позволяющий контролировать  $R_s$  областей, размеры которых ограничены только разрешающей способностью процесса литографии. На базе этой TC создан ряд модификаций (греческий крест, квадратный крест, скомпенсированный квадратный крест и др.). Разнообразие TC этого типа объ

ясняется стремлением получить более точную оценку  $R_s$  по эмпирической формуле Ван дер Пау, учитывающей геометрию TC.

Вторая группа — ТС для контроля ширины линии. В результате многократного повторения процесса литографии фактические размеры топологических элементов могут отличаться от проектных. Поэтому необходимо контролировать такой параметр как ширина сформированных линий W. Он используется и для оценки характеристик литографического оборудования, точности соблюдения режимов технологических операций процесса литографии.

Третья группа — ТС для проверки качества совмещения рисунков при формировании двух последовательных топологических слоев или двух последовательно используемых фотошаблонов в комплекте. Эта группа ТС используется для оценки характеристик ТО, например проекционных систем совмещения и установок пошаговой мультипликации. Оценка качества совмещения топологических слоев, получаемая с помощью ТС для количественной оценки качества совмещения рисунков по осям X и Y одновременно, не зависит от величины подтрава, боковой диффузии или изменения геометрических размеров фотошаблонов.

Четвертая и пятая группы — TC для оценки дефектов, таких как короткое замыкание металлизированных линий, отсутствие контакта металл — полупроводник и т.п. Подобные TC обеспечивает необходимую информацию для выбора оптимального набора проектных норм, оценки выхода годных приборов.

**Измерение поверхностных сопротивлений** производится двумя методами: мостовым методом и методом Ван дер Пау. Мостовой метод основан на измерении сопротивления резистора без учета контактного сопротивления (для чего используются потенциальные отводы). В этом случае поверхностное сопротивление рассчитывается по формуле 1:

$$R_{S} = \left(\frac{U}{I}\right) \cdot \left(\frac{W}{L}\right),\tag{1}$$

где  $R_S$  – поверхностное сопротивление, Ом·м;

U – падение напряжения на потенциальных отводах, В;

I – протекающий по телу резистора ток. А;

W – ширина резистора, м;

L – длина резистора, м.

Метод Ван дер Пау реализуется на тестовой структуре, показанной на рисунке 9.

Рисунок 9 – Тестовая структура по методу Ван дер Пау

Поверхностное сопротивление определяется тогда по формуле 2:

$$R_{S} = \left(\frac{\pi}{\ln 2}\right) \cdot \left(\frac{U}{I}\right),\tag{2}$$

где  $R_S$  – поверхностное сопротивление, Ом·м; U – падение напряжения на потенциальных отводах 3, 4, B; I – протекающий через токовые отводы 1, 2 ток. A.

Достоинством метода Ван дер Пау является нечувствительность результатов измерения к измерению размеров контролируемых проводящих областей, а также возможность измерения Rs в локальных областях.

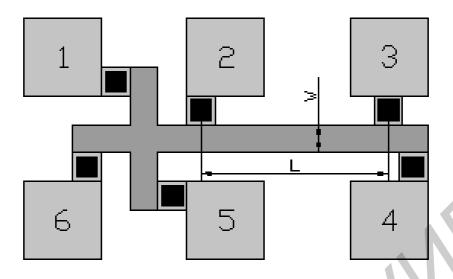

Измерение ширины проводящих областей и зазоров между ними. Для измерения двух параметров используется ТС, представляющая собой комбинацию двух методов: Ван дер Пау и мостового (рисунок 10). Для измерения ширины линии сначала методом Ван дер Пау измеряется поверхностное сопротивление проводящего слоя Rs, затем — сопротивление резистора в мостовой части R (исключая при этом влияние переходных контактных сопротивлений), после чего вычисляется ширина линии проводящего слоя в области мостовой части по формуле 3.

Рисунок 10 – Комбинировання тестовая структура

$$W = \frac{R_S \cdot l}{R},\tag{3}$$

где W – ширина мостовой части структуры, м;

$R_S$  – поверхностное сопротивление, Ом·м;

R – сопротивление резистора в мостовой части, Ом;

1 – длина резистора в области мостовой части структуры, м.

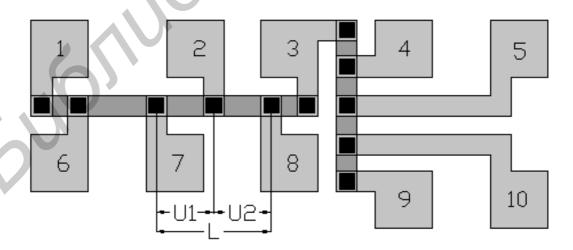

**Измерение рассовмещения топологических слоев.** Для оценки качества литографии при проведении операций совмещения используется ряд ТС. Для оценки качества совмещения проводящего слоя с контактным окном к нему используется ТС, показанная на рисунке 11.

Рисунок 11 – Тестовая сруктура для оценки качества совмещения

Она состоит из двух расположенных во взаимно перпендикулярном направлении мостовых резисторов. В центре каждого из них на равном расстоянии от потенциальных выводов топологически закладывается контактное окно, от которого имеется вывод на отдельную контактную площадку. При проведении операции совмещения на установке фотолитографии за счет рассовмещения контактное окно сдвигается из центрального положения, что приводит к различию в величинах падения напряжения в областях между контактным окном и правым и левым (верхним и нижним) потенциальными отводами при пропускании электрического тока через мост. Рассовмещение вдоль направления течения электрического тока рассчитывается по формуле 4:

$$r = \frac{l(U_1 - U_2)}{2(U_1 + U_2)},\tag{4}$$

где 1 – длина мостовой части между потенциальными отводами, мм;

$U_1$  — падение напряжения между одним из потенциальных отводов и центральным контактным окном, B;

$U_2$  – падение напряжения между другим потенциальным отводом и контактным окном, B.

Данный метод измерения получил широкое распространение при построении векторных полей рассовмещений, позволяющих разделять ошибки литографического оборудования. Другой метод измерения рассовмещения между проводящими слоями описан в. Здесь для оценки рассовмещения предлагается использовать ТС, напоминающую нанесенную шкалу, выполненную на основе проводящего слоя (рисунок 12).

Рисунок 12 – Тестовая структура для оценки рассовмещения

Указанная структура позволяет одновременно производить оценки с помощью электрических измерений и визуальным способом, что дает возможность не включать специальные фигуры визуального контроля.

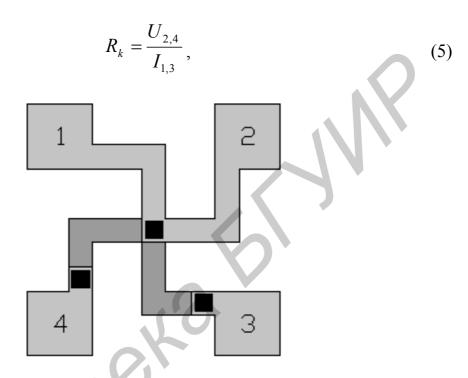

**Измерение контактного сопротивления.** Известны два основных способа измерения переходного контактного сопротивления. В [6] описан метод

Кельвина и показана соответствующая тестовая структура для измерения  $R_k$  (рисунок 13).

Измерение  $R_k$  производятся при задании тока в контакт и снятии величины падения напряжения непосредственно на контакте. Ток задается в площадки 1, 3, падение напряжения снимается с контактов 2, 4. Контактное сопротивление вычисляется по формуле:

Рисунок 13 – Тестовая структура по методу Кельвина

Данный метод соответствует одномерной модели контакта, используемого в элементах схемы. Для реализации другого метода измерения контактного сопротивления используется тестовая структура, представляющая собой прямолинейный проводник, к которому формируются несколько контактных окон, находящихся друг от друга на расстояниях, которые удовлетворяют соотношению 1:2:3:...:n, где n - количество сформированных контактов.  $R_k$  вычисляется с использованием исходного уравнения по формуле 6:

$$R = 2R_k + \frac{R_S \cdot L}{W}, \tag{6}$$

где R – сопротивление резистора, Ом;

$R_k$  – контактное сопротивление, Ом;

$R_S$  – поверхностное сопротивление, Ом·м;

W – ширина структуры, м;

L – длина резистора, м.

Измеряемые величины R(L) содержат постоянное слагаемое  $2R_k$ , откуда легко можно вычислить  $R_k$ , используя метод наименьших квадратов. При этом также вычисляется Rs слоя, на основе которого сформирован проводник. Точность измерения  $R_k$  зависит от конструкции и модификации применяемой тестовой структуры. Экспериментально показано, что 4-х зондовый метод Кельвина может быть использован при условиях, когда поверхностное сопротивление нижней области, к которой производится контакт, меньше или равно сопротивлению контакта, а также когда расстояние от края контакта до края области под контактом стремится к нулю. Рассмотрено несколько модификаций тестовых структур, показано, что оптимальной является структура с переменной длиной области проводника.

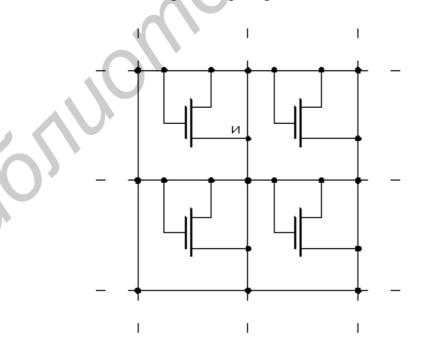

Контроль случайной дефектности. Случайная дефектность определяется с помощью либо тестовых структур, объединяющих большое количество тестовых компонентов, соединенных последовательно или параллельно, либо одной структуры с геометрическими размерами, соизмеримыми с размерами сомой схемы или ее узлов. Тестовые структуры для контроля случайных дефектов конструируются таким образом, что выход из строя одного из элементов или небольшой части тестовой структуры резко измерял контролируемые параметры всей тестовой структуры. Таким образом построена, например, сборка транзисторов (рисунок 14), предназначенная для оценки дефектности транзисторов ИС. Количество транзисторов в сборке равно 100. Затворы сборки соединены по строкам, истоки по столбцам, а стоки закорочены на землю. Подобное соединение дает возможность просканировать каждый транзистор в отдельности, что позволяет анализировать распределение по их видам.

Рисунок 14 – Сборка транзисторов.

Подобную матрицу можно построить для КМОП транзисторов. Если объединить все затворы и истоки, можно проектировать тестовые структуры с любым количеством транзисторов, т.е. с любой чувствительностью к случайным дефектам.

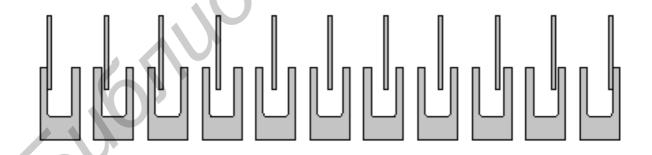

Другой распространенной ТС контроля случайных дефектов является ТС, изображенная на рисунке 15. Она представляет собой меандр из проводящего слоя с двумя вложенными в него гребенками. ТС формируется с помощью фотолитографии.

При пропускании тока через сформированный меандр определяется наличие обрыва, а при смешении напряжения на одной из гребенок относительно меандра определяется наличие закороток. При этом критичным является длина периметра, ширина меандра и затвор между ним и гребенкой. Данную ТС можно сформировать на рельефе одного из технологических слоев, что позволяет оценить уровень обрывов на ступеньках. Методология проектирования подобных ТС применима к КМОП технологиям.

Рисунок 15 – Тестовая структура – меандр

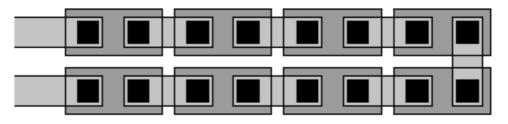

Большое применение имеют ТС для контроля обрывов и определения дефектности в переходных контактных областях. Такие ТС представляют собой цепочки контактов между различными областями (рисунок 16).

Рисунок 16 – Цепочка контактов

#### 5 СТРУКТУРА ПРОГРАММЫ НА ЭВМ

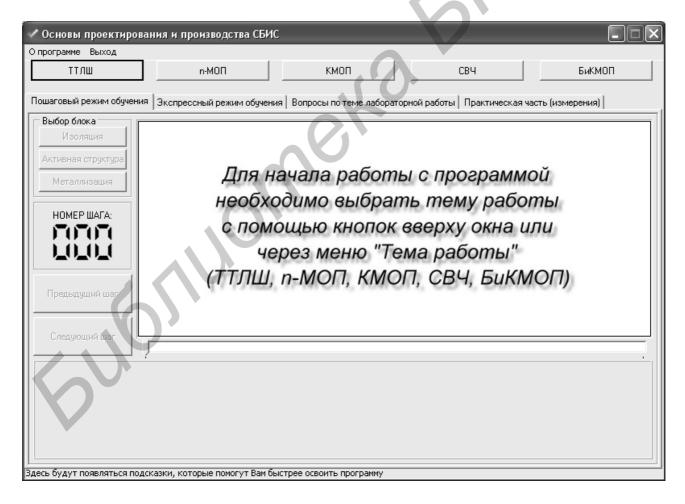

Программа состоит из двух блоков. Первый блок теоретический, а второй – практический. В первом блоке обучающийся изучает эскизный маршрут изготовления БИС. Предусмотрено два варианта изучения: пошаговый и "экспресс" методы. Вариант изучения выбирается из меню выбора варианта.

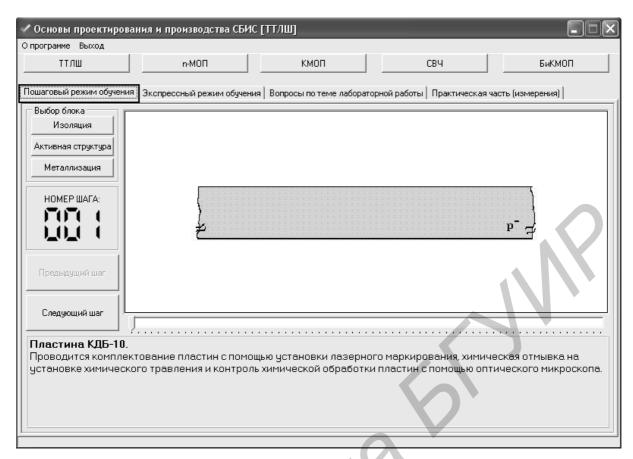

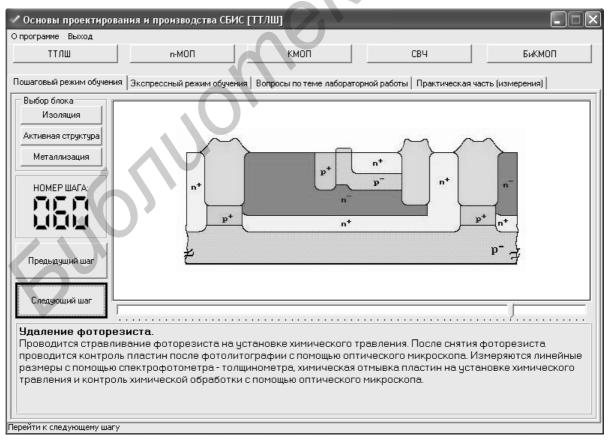

В первом варианте последовательно выводятся сечения структур после каждой технологической операции. Движение вперед осуществляется путем нажатия кнопки "Следующий". Каждое сечение снабжено информативной строкой, в которой отражается название операции с комментарием. Из комментария обучающийся может получить более подробную информацию о технологической операции (оборудование, режимы и т.п.). Если в процессе изучения по какой-либо причине понадобилось вернуться на один или несколько шагов назад, то для этого предусмотрена кнопка "Предыдущий". Несколькими нажатиями на эту кнопку можно вернуться к любому ранее показанному сечению структуры. В конце выводится конечное сечение полупроводниковой структуры.

Рисунок 17 – Выбор технологического маршрута

Рисунок 18 – Выбор варианта изучения технологического маршрута

Рисунок 19 – Пошаговый метод изучения технологии

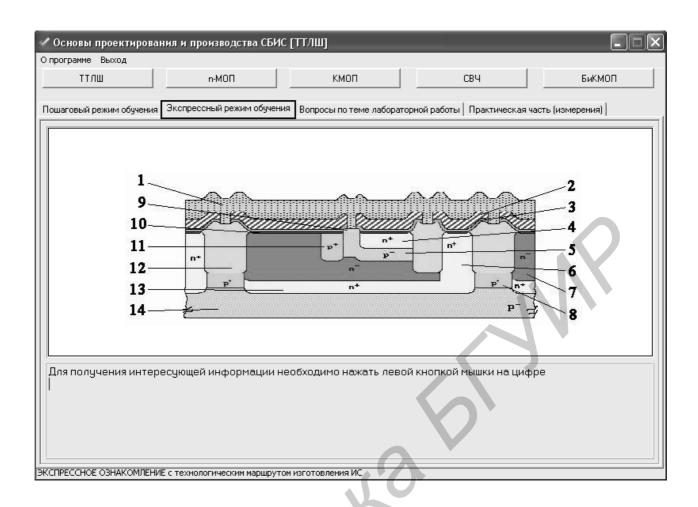

Рисунок 20 – Экспресс- метод изучения технологии

Второй вариант предназначен для тех, кто уже имеет некоторые знания по данному технологическому процессу. При выборе этого варианта появляется меню выбора рисунка. Пользователь может, введя номер, получить на экране соответствующую информацию по выбранной части технологического маршрута.

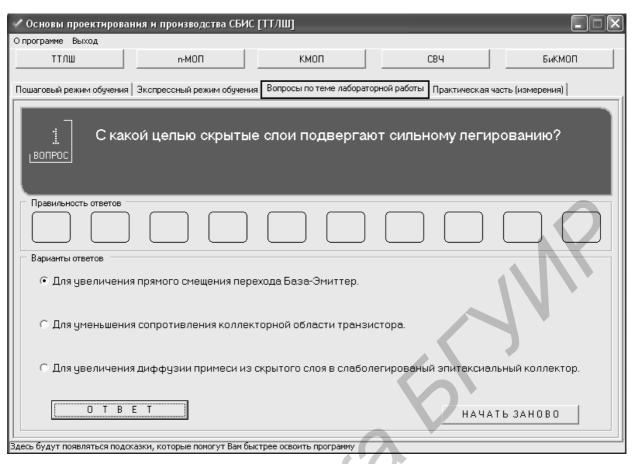

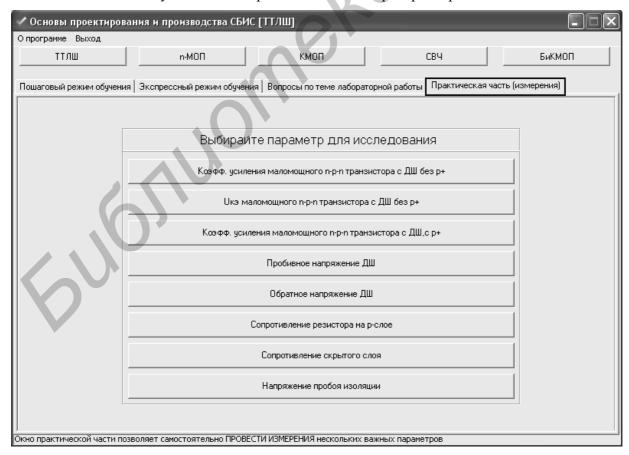

Теоретическая часть заканчивается контролем уровня усвоения технологического процесса (Рисунок 21). Пользователю предоставляется возможность ответить на блок вопросов. Для каждого вопроса предусмотрено несколько вариантов ответов, один из которых правильный. На этом первый ("Теоретический") блок заканчивается. Во втором блоке обучающийся проводит анализ технологии изготовления ИС. Это происходит посредством имитации тестового контроля. Программа позволяет провести контроль восьми параметров ТС по каждому технологическому маршруту изготовления ИС. Обучающийся получает у преподавателя задание в виде наименований параметров, которые следует проконтролировать. Выбор параметров в программе осуществляется из меню выбора параметра, приведенного на рисунке 22. Движение по меню происходит стандартным методом с помощью клавиш управления курсором.

Рисунок 21 – Вопросы по теме лабораторной работы

Рисунок 22 – Меню выбора исследуемого параметра

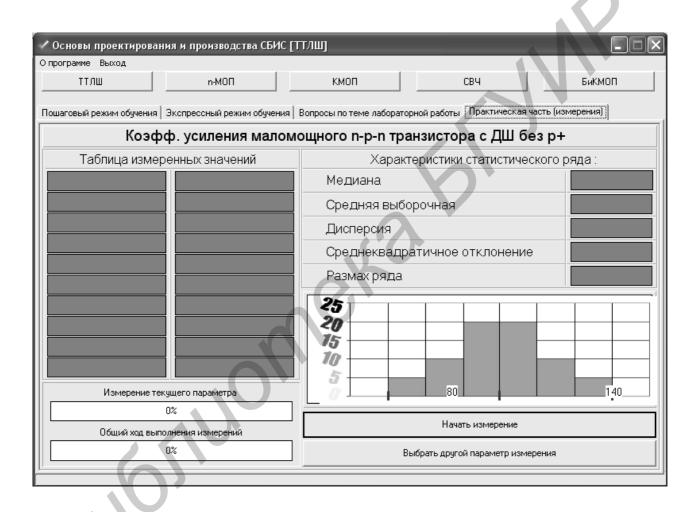

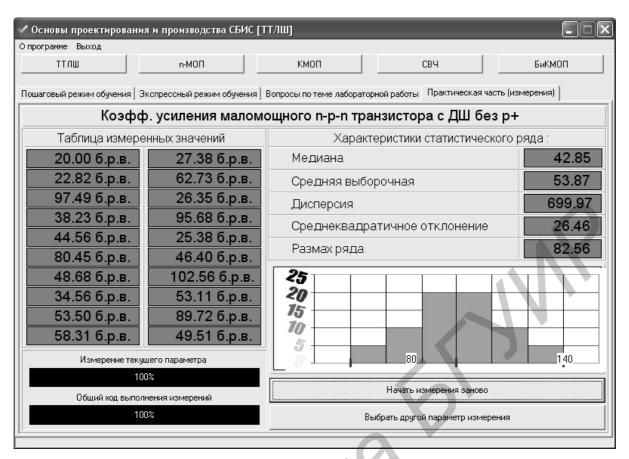

После того как пользователь выбрал один из измеряемых параметров, программа переходит в режим имитации процесса измерения (рисунок 23). Проводятся измерения параметра ТС на 20 пластинах. Экран при этом разделен на две части: таблица результатов и измерительное табло. Под таблицей результатов находятся два индикатора процесса (индикатор хода процесса измерения данной пластины и индикатор хода всего процесса измерения). В таблицу заносятся результаты измерений параметров, в ходе процесса измерения. После окончания процесса измерения обучающийся должен переписать эти результаты и внести их в отчет (рисунок 24).

Рисунок 23 – Экран перед проведением измерений

Рисунок 24 – Результаты измерений и статистического анализа

По полученным данным необходимо построить реальное распределение параметров, сопоставить реальное и идеальное распределение на едином графике, объяснить возможные причины отклонений (если таковые имеются) и дать рекомендации по изменению режимов технологических операций для устранения расхождений.

При выполнении работы студенту необходимо провести анализ трех различных параметров TC.

## 6 ТРЕБОВАНИЯ ТЕХНИКИ БЕЗОПАСНОСТИ ПРИ РАБОТЕ С ИЗМЕРИТЕЛЬНЫМ КОМПЛЕКСОМ

- 1 К работе с измерительным комплексом допускаются студенты, прошедшие инструктаж по технике безопасности в технологической лаборатории и изучившие порядок работы с измерительным комплексом.

- 2 Перед включением приборов в сеть необходимо проверить наличие заземления на измерительном комплексе и в блоке питания микроскопа. Заземление приборов проводит лаборант.

- 3 Категорически запрещается: 1) вскрывать защитные кожухи на приборах; 2) прикасаться при включенных приборах к токоведущим проводам и клеммам.

#### 7 КОНТРОЛЬНЫЕ ВОПРОСЫ

#### **7.1** ТТЛІЦ ИС

- 1. Назовите конструкторско-технологические методы повышения быстродействия биполярных ИС.

- 2. Объясните назначение диодов на основе барьеров Шоттки в биполярных транзисторах.

- 3. Назовите основные этапы технологического маршрута формирования биполярного транзистора с диодом Шоттки.

- 4. Нарисуйте профиль легирования биполярного транзистора. Объясните необходимость проведения двухстадийного процесса ионного легирования при получении базовой области.

- 5. Объясните назначение различных ТС в биполярных ИС.

- 6.В чем заключаются технологические особенности изготовления скрытого n+ слоя?

- 7.Объясните принципы создания основных промышленных методов изоляции в биполярных ИС.

- 8.С какой целью используется многослойная металлизация? Объясните на конкретном примере функциональное назначение различных слоев металлизации в биполярных ИС.

## 7.2 ИС на п-МОП структурах

- 1. Схематически изобразите варианты конструкций ячейки ДОЗУ. Объясните принципы их работы.

- 2. В чем заключаются особенности технологии изготовления полупроводниковых ЗУ?

- 3. Назовите основные этапы технологического маршрута формирования ДОЗУ большой емкости.

- 4. Какое назначение имеет каждый слой поликремния в технологии ДОЗУ? Сформулируйте технологические требования к этим слоям.

- 5. Объясните технологические особенности процессов планаризации ДОЗУ. С помощью каких тестовых структур можно проверить качество планаризации?

- 6. Изобразите конструкцию ТС, с помощью которых можно оценить качество контактов в слоях поликремния и металлизации.

#### 7.3 КМОП ИС

- 1. Назовите основные этапы технологического маршрута формирования КМОП структур.

- 2. Каким образом с помощью ТС можно обеспечить воспроизводимость технологического процесса?

- 3. С помощью каких технологических процессов можно управлять пороговым напряжением n- и p- канальных транзисторов при их формировании ?

- 4. С какой целью при создании КМОП ИС используется эпитаксиальная структура?

- 5. Какие эффекты могут возникнуть при уменьшении размеров элементов в КМОП- структуре?

#### 7.4 СВЧ ИС

- 1. Из каких этапов состоит технологический маршрут изготовления ИС на GaAs?

- 2. Дайте сравнительную характеристику технологии изготовления ИС на Si и GaAs.

- 3. Назовите причины, сдерживающие широкое развитие GaAsтехнологии.

- 4. Перечислите основные особенности конструкции ПТШ на GaAs.

- 5. Объясните необходимость применения мезотехнологии при создании ПТШ на GaAs.

- 6. Какие параметры TC могут указывать на изменения процессов в технологических блоках создания ОК и БШ?

#### 7.5 БиКМОП ИС

- 1. Назовите основные конструкторско-технологические особенности изготовления БиКМОП ИС.

- 2. Укажите главные области применения ИС, изготовленных по БиКМОП- технологии.

- 3. Назовите основные этапы технологического процесса формирования БиКМОП ИС.

- 4. Объясните необходимость и особенности проведения тестового контроля в БиКМОП- технологии.

- 5. Объясните назначение различных структур тестового модуля БиКМОП ИС.

### 7.6 Запоминающий элемент ЭСППЗУ

- 1. Объясните механизм программирования ячейки ЭСППЗУ.

- 2. Назовите назначение всех элементов двухтранзисторной ячейки ЭСППЗУ.

- 3. Назовите основные этапы технологического процесса формирования двухтранзисторной ячейки ЭСППЗУ.

- 4. Объясните конструктивно-технологические особенности изготовления транзистора с плавающим затвором.

#### ЛИТЕРАТУРА

- 1 Зи С. Технология СБИС: В 2 т. Т. 1-2. М.: Мир, 1986.

- 2 Степаненко И. П. Основы микроэлектроники.— М.: Лаборатория базовых знаний,  $2000.-488\ c.$

- 3 Clein D. CMOS IC layout : concepts, methodologies, and tools. Boston: Butterworth–Heinemann, 2000. 261 p.

- 4 Рындин Е.А., Коноплев Б.Г. Субмикронные интегральные схемы: элементная база и проектирование. Таганрог, 2001. 146 с.

- 5 Kuo J., Lin Sh. Low- voltage SOI CMOS VLSI devices and circuits. New York: John Wiley & Sons, Inc., 2001. 407 p.

- 6 Razavi B. Design of analog CMOS integrated circuits. New York: McGraw-Hill, 2001.- 684 p.

- 7 Campbell S. A. The science and engineering of microelectronic fabrication. New York: Oxford university press, 2001. -603 p.

- 8 Haraszti T. P. CMOS memory circuits. New York: Kluwer Academic Publishers, 2002. 551 p.

- 9 Rabaey J., Chandrakasan A., Nikolic B. Digital Integrated Circuits: A Design Perspective, second edition. New York: Prentice Hall, 2003. 747 p.

- 10 Goddard W. A., Brenner D. W., Lyshevski S. E., Iafrate G. J. Handbook of nanoscience, engineering, and technology. New York: CRC Press, 2003. 709 p.

- 11 Bhushan B. Handbook of nanotechnology. Berlin: Springer-Verlag, 2004. 1222 p.

#### Учебное издание

**Черных** Александр Георгиевич, **Ригольд** Сергей Валентинович

## ТЕХНОЛОГИЧЕСКИЕ МАРШРУТЫ ИЗГОТОВЛЕНИЯ ИС

Лабораторный практикум по курсам «Маршрутная технология интегральных схем» и «Технологические процессы микроэлектроники» для студентов специальностей 1-41 01 02 «Микро- и наноэлектронные технологии и системы» и 1-41 01 03 «Квантовые информационные системы» всех форм обучения

Ответственный за выпуск А.Г. Черных

Подписано в печать 23.06.2006.

Гарнитура «Таймс». Уч.-изд. л. 2,2. Формат 60х84 1/16. Печать ризографическая.

Тираж 100 экз.

Бумага офсетная. Усл. печ. л. 2,21. Заказ 197.

Издатель и полиграфическое исполнение: Учреждение образования «Белорусский государственный университет информатиеи и радиоэлектроники» ЛИ №02330/0056964 от 01.04.2004. ЛП №02330/0131666 от 30.04.2004