## АВТОМАТИЗИРОВАННОЕ ПОСТРОЕНИЕ ТОПОЛОГИ ЯЧЕЕК МАКРОБЛОКОВ СБИС

С. Э. Миронов, Н. М. Сафьянников, А. К. Фролкин Кафедра вычислительной техники, Санкт-Петербургский Государственный электротехнический университет «ЛЭТИ» им. В. И. Ульянова (Ленина) Санкт-Петербург, Россия

E-mail: semironovspb@yandex.ru, anfrolkin@gmail.com

Статья посвящена формализации построения топологии ячеек макроблоков СБИС. Представленная методика построения топологии позволяет генерировать топологию ячейки в соответствии со структурнотопологическим планом проектируемого макроблока.

## Введение

Расширение номенклатуры разрабатываемых интегральных схем, сокращение сроков проектирования СБИС, а также постоянное совершенствование проектных норм требуют автоматизации проектирования. Автоматизируется перевод языкового описания в системное и логическое представление, автоматизируется расположение блоков и межблочные трассировки, автоматизируется электрическое моделирование блоков и т.д. Эта работа посвящена вопросам автоматизации проектирования топологии ячеек макроблоков СБИС. Причем описанные в ней методика и программные средства применимы для построения топологии ячеек как регулярных, так и нерегулярных макроблоков, отличающихся характером расположения выводов.

Регулярные макроблоки СБИС собираются из заказных специализированных ячеек с топологией, оптимизированной под конкретную схему, в соответствии с топологическим планом, более или менее однозначно определяемым спецификой реализуемой схемы, например, реализуемым аппаратным образом алгоритмом. Использование таких ячеек позволяет повысить плотность упаковки макроблока. Построение нерегулярных макроблоков СБИС осуществляется путем последовательного итерационного применения программ размещения и трассировки из стандартных библиотечных ячеек, выводы которых располагаются в строго определенных местах с координатами, кратными шагу трассировки.

## I. Автоматическое построение эскиза топологии по электрической схеме ячейки

Представленная методика реализует построение топологии ячейки по имеющейся электрической схеме в EDIF-файле. Это текстовый формат описания графического отображения электрических схем, позволяющий хранить информацию о транзисторах ячейки и связях между ними. Результатом работы программ размещения транзисторов и трассировки внутренних связей в ячейке является технологически инвариантный эскиз топологии ячейки, который с помощью программы TopDesign [1] настраивается на требуемые проектные нормы. Перед запуском программ размещения транзисторов и трассировки внутренних связей в ячейке задается топологическая модель ячейки, описывающая расположение выводов и шин земли и питания и топологический слой, в котором они организуются.

Программа размещения транзисторов позволяет строить две полоски транзисторов N и Р типа из схемы в EDIF-файле. Посредством совмещения стоковых/истоковых областей у соседних транзисторов можно значительно сократить площадь ячейки [2]. В представленной программе происходит нахождение минимального количества разрывов в связке транзисторов N и Р типа, аналогично решению задачи Эйлера. Существует ряд похожих программ, например Topologizer [3], которая к тому же еще и делит транзисторы с большой шириной затвором на части. Поскольку стояла задача создания простой программы размещения транзисторов, была реализована программа, которая перебором находит оптимальную последовательность двух полос транзисторов. Сложность алгоритма составляет n\*n, где n – это количество транзисторов. Для небольшой ячейки это не много и поиск оптимальных последовательностей транзисторов N и Р типа занимает до одной минуты на стандартном персональном компьютере.

Метод трассировки внутренних связей в ячейке основан на методе Соукупа [4]. Достоинствами этого алгоритма можно считать простоту в реализации, быструю трассировку сразу всех соединений. Этот алгоритм сводится к ортогональному распространению волн и восстановлению путей по точкам. В отличии от алгоритма Ли метод позволяет бороться с ситуациями «блокировок» не соединенных терминалов, путем назначения приоритетов.

## II. ПРИМЕР СОЗДАНИЯ ЯЧЕЙКИ

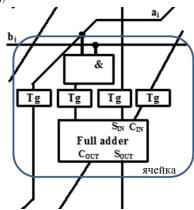

Примером создания топологии составной ячейки может служить фрагмент из топологии конвейерного матричного умножителя. В структуре умножителя [5], можно вычленить повторяющийся фрагмент — базовую ячейку, представ-

ленную на рис. 1. В базовой ячейке осуществлятся:

- вычисление i-го разряда j-го частичного произведения путем умножения разряда  $a_i$  множимого на разряд  $b_j$  множителя на элементе «2И»;

- двоичное суммирование этого разряда частичного произведения с полученной ранее суммой частичных произведений на двоичном одноразрядном полном сумматоре (Full adder);

- сохранение і-го разряда аі множимого и промежуточных результатов в триггерах (tg).

Рис. 1 – Фрагмент структуры конвейерного матричного умножителя – базовая ячейка

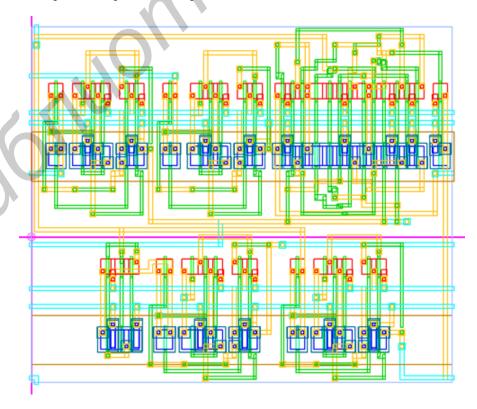

На рис. 2 приведен топологический чертеж базовой ячейки умножителя, полученный после настройки сгенерированного топологического эскиза на один из вариантов проектных норм.

Для ячейки был выбран вариант топологической модели, в котором шины земли и питания организуются в топологическом слое верхнего металла и располагаются между транзисторами N и P типа.

Аналогичным образом строятся остальные ячейки умножителя. В дальнейшем, специализированный кремневый компилятор может собирать из таких ячеек топологию конвейерного матричного умножителя требуемой разрядности. Используя представленную методику, можно создавать топологии ячеек для любых интегральных схем, как с регулярной так и с нерегулярной структурой. Работа выполнена при поддержке РФФИ, грант № 14-07-31098.

- Зуев, И. С. Технологически инвариантная система проектирования топологии стандартных фрагментов МОП БИС / И. С. Зуев, А. Б. Максимов, С. Э. Миронов, Н. М. Сафьянников // Известия вузов. «Электроника». – 2003. – № 3. – С. 63–70.

- 2. Миронов, С. Э. Средства автоматизации проектирования топологии ячеек СБИС. / С. Э. Миронов, А. К. Фролкин // Изв. СПбГЭТУ «ЛЭТИ». 2014. Вып. 6. С. 40–43.

- 3. Kollaritsch, P. W., Topologizer: An expert system translator of transistor connectivity to symbolic cell layout / P. W. Kollaritsch, N.H.E. Weste // Solid-state circuits, 1985. Vol. 20, № 3, P. 799–804.

- Soukup, J. Fast maze router / J. Soukup // ACM/IEEE Design Automation Conf., 1978. – P. 100–102.

- 5. Миронов, С. Э. Методика структурнотопологической оптимизации регулярных макроблоков СБИС / С. Э. Миронов, Н. М. Сафьянников, А. К. Фролкин // Изв. СПбГЭТУ «ЛЭТИ». – 2015. – Вып. 1. – С. 17–23.

Рис. 2 – Топологический чертеж базовой ячейки конвейерного матричного умножителя