### Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

Кафедра систем управления

А.П. Пашкевич, О.А. Чумаков

### МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ УПРАВЛЕНИЯ

Конспект лекций для студентов специальности I-53 01 07 «Информационные технологии и управление в технических системах» дневной формы обучения

В 2-х частях

Часть 2

УДК 004.31(075.8) ББК 32.973.26-04 я 73 П 22

> Рецензент: доц. кафедры ЭВМ БГУИР, канд. техн. наук Н.И. Силков

#### Пашкевич А.П.

П 22 Микропроцессорные системы управления: Конспект лекций для студ. спец. I-53 01 07 «Информационные технологии и управление в технических системах» дневн. формы обуч.: В 2 ч. Ч. 2 / А.П. Пашкевич, О.А. Чумаков. – Мн.: БГУИР, 2006. – 72 с.: ил.

ISBN 985-444-986-6 (ч. 2)

Во второй части издания рассмотрены вопросы, связанные с принципами построения однокристальных микроконтроллеров семейств MCS-48 и MCS-51, а также особенностями их применения в цифровых системах управления. Описаны их функциональные возможности, электрические параметры и система команд. Приводятся технические характеристики современных однокристальных микроконтроллеров, базирующихся на архитектуре MCS-51.

Часть I издана БГУИР в 2005 г.

УДК 004.31 (075.8) ББК 32.973.26-04 я 73

# Содержание

| Введение                                                  | 5  |

|-----------------------------------------------------------|----|

| 1. Основы архитектуры микроконтроллеров                   | 6  |

| 1.1. Основные типы микроконтроллеров                      | 6  |

| 1.2. Память микроконтроллеров и их программирование       | 7  |

| 1.3. Питание и управление энергопотреблением              |    |

| 2. Семейства MCS-48, MCS-51 и их модификации              | 9  |

| 2.1. Микроконтроллеры фирмы Intel                         | 9  |

| 2.2. Микроконтроллеры фирмы Philips                       | 10 |

| 2.3. Микроконтроллеры фирмы Atmel                         | 10 |

| 2.4. Микроконтроллеры фирмы Analog Devices                | 11 |

| 2.5. PIC-микроконтроллеры фирмы Microchip                 | 12 |

| 2.5. PIC-микроконтроллеры фирмы Microchip                 | 13 |

| 3.1. Архитектура микроконтроллеров MCS-48                 | 13 |

| 3.2. Блок управления и синхронизации                      | 15 |

| 3.3. Арифметико-логическое устройство                     |    |

| 3.4. Память микроконтроллеров семейства MCS-48            | 17 |

| 3.5. Память программ                                      | 18 |

| 3.6. Память данных                                        | 20 |

| 3.7. Организация ввода/вывода информации                  | 21 |

| 3.8. Система обработки прерываний                         | 24 |

| 3.9. Таймер/счётчик                                       | 26 |

| 3.10. Система команд MCS-48                               | 27 |

| 3.11. Команды пересылки данных                            | 28 |

| 3.12. Арифметические команды                              | 30 |

| 3.13. Логические команды                                  | 32 |

| 3.14. Команды передачи управления                         | 33 |

| 3.15. Команды управления режимами работы микроконтроллера | 36 |

| 3.16. Загрузка прикладных программ в резидентную память   |    |

| 4. Семейство микроконтроллеров MCS-51                     | 39 |

| 4.1. Архитектура микроконтроллеров MCS-51                 | 39 |

| 4.2. Арифметико-логическое устройство                     | 42 |

| 4.3. Память микроконтроллеров семейства MCS-51            | 42 |

| 4.4. Параллельные порты ввода/вывода                      |    |

| 4.5. Система прерываний MCS-51                            | 46 |

|   | 4.6. Таймеры/счётчики                            | 49 |

|---|--------------------------------------------------|----|

|   | 4.7. Последовательный интерфейс                  | 52 |

|   | 4.8. Управление энергопотреблением               | 57 |

|   | 4.9. Сброс в начальное состояние и синхронизация | 58 |

|   | 4.10. Загрузка прикладных программ               | 59 |

|   | 4.11. Система команд семейства MCS-51            | 61 |

|   | 4.12. Команды пересылки данных                   | 62 |

|   | 4.13. Команды арифметических операций            | 65 |

|   | 4.14. Команды логических операций                | 67 |

|   | 4.15. Команды операций над битами                | 68 |

|   | 4.16. Команды передачи управления                | 68 |

|   | Литература                                       | 71 |

| 4 | Subniuomeka                                      |    |

#### Введение

Большинство современных цифровых систем управления реализуются на базе *микроконтроллеров* (МК) — специализированных микропроцессорных устройств, ориентированных на выполнение управляющих функций. Интегрируя на одном кристалле высокопроизводительный процессор, память и набор периферийных устройств, микроконтроллеры позволяют с минимальными затратами реализовать высокоэффективные системы и устройства управления.

В настоящее время однокристальные микроконтроллеры являются наиболее массовыми представителями микропроцессорной техники, объем выпуска которых составляет около 2,5 млрд. штук в год. Их производством занимается ряд фирм (Intel, Motorola, Philips, Siemens, Atmel, Dallas, Temic, Oki, AMD и др.), которые предоставляют потребителям большую номенклатуру изделий, начиная с относительно простых 8-разрядных моделей и кончая 32-разрядными устройствами, ядром которых служат CISC-и RISC-процессоры.

В изделиях массового применения наибольшее распространение получили 8-разрядные однокристальные микроконтроллеры, которые имеют практически одинаковое вычислительное ядро, но отличаются объемом и типом внутренней памяти, номенклатурой размещенных на кристалле периферийных устройств и рядом технических характеристик. У истоков производства микроконтроллеров стоит фирма Intel с семействами восьмиразрядных микроконтроллеров МСS-48 и МСS-51. Первые модификации МСS-48/51 были выполнены по n-MOS технологии и являлись функционально завершенными однокристальными микро ЭВМ гарвардской архитектуры, один из основных принципов которой состоит в логическом разделении адресных пространств памяти программ и данных. Последующие версии контроллеров МСS-51 стали изготавливать по более совершенной и низкопотребляющей СМОS технологии.

сегодняшний Ha день существует более 200 модификаций микроконтроллеров семейства MCS-51, выпускаемых почти 20-ю компаниями. Эти модификации включают в себя кристаллы с широчайшим набором периферии: от простых 20-выводных МК с одним таймером и резидентной памятью программ объемом 1 Кбайт до сложнейших 100-выводных кристаллов с 10-разрядными АЦП, массивами таймеров/счетчиков, аппаратными разрядными умножителями и резидентной памятью программ до 64 Кбайт. Каждый год появляются все новые варианты представителей семейства MCS-51 с повышенным быстродействием, пониженным энергопотреблением, большим объемом памяти, а также с возможностью подключения сложных периферийных устройств на основе CAN и USB интерфейсов.

В данном курсе лекций рассматривается архитектура типичных представителей семейств микроконтроллеров MCS-48 и MCS-51, а также приводятся рекомендации по их использованию в цифровых системах управления.

### 1. Основы архитектуры микроконтроллеров

#### 1.1. Основные типы микроконтроллеров

Микроконтроллер — это устройство, выполненное по технологии БИС и объединяющее на одном кристалле микропроцессор, память, порты ввода-вывода, а также средства поддержки работы в реальном масштабе времени (таймеры, обработчики прерываний и т.д.).

В однокристальных микроконтроллерах используется *гарвардская* архитектура. Согласно ее концепциям память программ и память данных имеют раздельные адресные пространства, при обращении к которым используются различные механизмы адресации. Содержимое памяти программ формируется либо на заводе-изготовителе (масочное программирование), либо с использованием программатора пользователя (электрическое программирование).

Современные микроконтроллеры можно разделить на три основных типа: а) встраиваемые 8-разрядные микроконтроллеры; б) 16- и 32-разрядные микроконтроллеры; в) цифровые сигнальные процессоры.

Во встраиваемых микроконтроллерах все необходимые ресурсы (память, таймеры, порты ввода-вывода и т.д.) располагаются на одном кристалле с процессорным ядром, благодаря чему обеспечивается их включение в систему управления с использованием минимального количества дополнительных компонентов. Для них характерны небольшие по современным понятиям объемы памяти программ (ROM объемом от 1 до 128 Кбайт) и памяти данных (RAM объемом от 64 байт до 4 Кбайта. Кроме того, обычно исключается возможность записи в память программ, что уменьшает вероятность ошибок, и имеется защита от несанкционированного копирования содержимого этой памяти. Типичный микроконтроллер для встроенных приложений потребляет ток от микроампер до десятка миллиампер и обычно работает в температурном диапазоне от –55 до +125°С. Программируются такие контроллеры на языках ассемблер или С.

В более сложных *микроконтроллерах* (16- и 32-разрядных) используют только внешнюю память, которая включает в себя как память программ (ROM), так память данных (RAM). Они применяются в системах, где требуется большой объем памяти и относительное небольшое количество устройств (портов) ввода/вывода. Типичным примером применения такого МК с внешней памятью является котроллер жесткого диска (HDD) с буферной кэш-памятью, который обеспечивает промежуточное хранение и распределение больших объемов данных (порядка нескольких мегабайт). Внешняя память позволяет такому микроконтроллеру работать с более высокой скоростью, чем встраиваемый МК.

*Цифровые сигнальные процессоры* (DSP) предназначены для цифровой обработки аналоговых сигналов, т.е. для решения задач, которые традиционно решала аналоговая схемотехника. Они обеспечивают ввод данных от аналогового источника, их обработку и формирование соответствующего выходного сигнала в

реальном масштабе времени. К сигнальным процессорам предъявляются специфические требования. От них требуются максимальное быстродействие, малые габариты, легкая стыковка с аналого-цифровыми и цифро-аналоговыми преобразователями, большая разрядность обрабатываемых данных и небольшой набор математических операций, обязательно включающий операцию умножения-накопления и аппаратную организацию циклов. На процессорах такого типа сделано большинство модемов, а также различные системы обработки звука и видео.

Для подключения внешних устройств в микроконтроллерах применяются как *параллельные* порты ввода/вывода, так и *последовательные* шины типа I2C (Inter-Integrated Circuit bus) или SPI (serial peripheral interface). Благодаря этим шинам для подключения периферийных микросхем к процессору достаточно двух-трех линий. Соответственно, уменьшается число выводов микросхем, позволяя уменьшить габариты устройств, повысить надежность и упростить разработку устройств.

Следует также различать *CISC* и *RISC*-микроконтроллеры. Команды RISC-процессоров очень просты и почти всегда выполняются за один такт. Для реализации операции, обрабатываемой CISC-процессором как одна команда, RISC должен выполнить последовательность микрокоманд. Достоинством CISC-микроконтроллеров является сокращенный объем программного кода и экономия усилий программиста, затраченных на его написание. Однако RISC-процессоры производительнее, занимают меньше места на кристалле и потребляют значительно меньше энергии, чем CISC. Поэтому в последнее время появляется все больше типов микроконтроллеров с RISC-архитектурой.

### 1.2. Память микроконтроллеров и их программирование

В микроконтроллерах используется три основных вида памяти: память программ, память данных, регистры. *Память программ* представляет собой постоянную память, предназначенную для хранения программного кода и констант. Она не изменяет содержимого в процессе выполнения программы. *Память данных* предназначена для хранения переменных в ходе выполнения программы. *Регистры* включают внутренние регистры процессора и регистры, используемые для управления периферийными устройствами. Следует заметить, что в микроконтроллерах семейств MCS-48/51 в качестве регистров используется специальная область внутренней (резидентной) памяти данных. Кроме того, наряду с внутренней памятью большинство микроконтроллеров могут использовать и внешнюю память программ и данных.

Для хранения программ обычно служит один из видов постоянной памяти: ROM (масочные ПЗУ), PROM (однократно программируемые ПЗУ), EPROM (электрически программируемые ПЗУ с ультрафиолетовым стиранием) или EEPROM (ПЗУ с электрической записью и стиранием, к этому виду также относятся современные микросхемы Flash-памяти). Все эти виды памяти

являются энергонезависимыми, т.е. содержимое такой памяти сохраняется после выключения питания.

Для программирования микроконтроллеров (т.е. записи в них программ) обычно используются специальные устройства — программаторы, подключаемые к персональному компьютеру. Исключением является микроконтроллеры с ROM-памятью, программирование которых осуществляется в процессе изготовления. Однако в настоящее время программирование EEPROM-памяти можно осуществлять и непосредственно на плате проектируемого или уже готового устройства. Такой способ получил название — ISP (In System Programming), он позволяет обновлять программное обеспечение микроконтроллера без удаления из платы, что дает большую экономию времени на этапе разработки.

Последние модели микроконтроллеров содержат встроенную Flash-память, которая функционально мало отличается от EEPROM. Основное различие состоит в способности стирания записанной информации. В памяти EEPROM стирание производится отдельно для каждой ячейки, а во Flash-памяти стирание осуществляется целыми блоками.

Для хранения данных используется RAM — оперативное запоминающее устройство. Число циклов чтения и записи в такой памяти неограниченно, но при отключение питания вся информация теряется.

#### 1.3. Питание и управление энергопотреблением

Первые микроконтроллеры были рассчитаны на напряжение питания 5В. Однако в последнее время появляется все больше устройств с номинальным напряжением 3,3В и менее. Это связано в первую очередь с расширяющейся сферой применения микроконтроллеров в устройствах с автономным питанием.

Кроме того, во многих микроконтроллерах предусмотрена возможность управления потребляемой мощностью, путем их перевода программными средствами в режим хода или режим останова. Режим холостого хода характеризуется тем, что работа процессорного ядра приостанавливается, в рабочем состоянии остаются лишь генератор синхросигналов и сторожевой таймер. Регистры сохраняют свое значение. Выход из этого режима возможен по прерыванию или по сигналу сброса. Также может быть предусмотрен специальный таймер холостого режима, который периодически "пробуждает" выполнения активных действий. В этом режиме микроконтроллер ДЛЯ микроконтроллер потребляет около 30% номинальной мощности. В режиме останова работа внутри кристалла полностью остановлена. Выход из режима возможен по сигналу сброса (иногда по сигналу внешнего прерывания). В режиме останова потребляемый ток может достигать 1 мкА и менее.

### 2. Семейства MCS-48, MCS-51 и их модификации

#### **2.1.** Микроконтроллеры фирмы Intel

Микроконтроллеры Intel 8048 и 8051, изготовленные по технологии n-MOS, заложили основу архитектуры однокристальных устройств семейств MCS-48 и MCS-51. Следующим принципиальным шагом стал переход на CMOS-технологию (модификация 8хС51), что позволило реализовать режимы Idl (холостой ход) и PowerDown (пониженное энергопотребление). В дальнейшем фирмой Intel были выпущены микроконтроллеры 8хС51FA/FB/FC и 8хС51RA/RB/RC со встроенными специализированными таймером/счетчиком (PCA) и сторожевым таймером (WDT), позволяющими существенно снизить время реакции на внешние события. Архитектура этих микроконтроллеров оказалась настолько удачной, что стала промышленным стандартом.

Изначально наиболее "узкими" местами MCS-51 были 8-разрядное АЛУ и довольно большое время выполнения команд (12 тактов). Для устранения этих было создано семейство микроконтроллеров недостатков обеспечивающих адресацию до 16 Мбайт памяти и выполняющих 16-битные арифметические и логические операции за 2 такта. Система команд MCS-251 включает два набора инструкций - первый набор является копией системы команд MCS-51, а второй – содержит расширенные инструкции, реализующие преимущества архитектуры MCS-251. Перед использованием микроконтроллера его необходимо сконфигурировать, т.е. определить, какой из наборов станет активным после включения питания. Для пользователей, ориентированных на MCS-251 В качестве замены MCS-51, применение выпускаются микроконтроллеры MCS-151, уже запрограммированные на активизацию системы команд MCS-51.

управления системах также широко используются микроконтроллеры семейства MCS-96, основанные на несколько иной архитектуре. Базовый представитель этого семейства 8096 содержит разрядный процессор, 8 Кбайт внутренней программной памяти с возможностью внешнего расширения до 64 Кбайт, 232 байта ОЗУ с возможностью внешнего расширения до 64 Кбайт, развитые средства поддержки режима реального времени, скоростной ввод-вывод. Он позволяет осуществлять операции в форматах "байт" (8 бит), "слово" (16 бит), а а также "двойное слово" (32 бит). Такие микроконтроллеры обладают усовершенствованной системой команд, а также разнообразием встроенной периферии (параллельные и последовательные событий, порты, блоки процессоров многоканальные аналого-цифровые преобразователи, широтно-импульсные модуляторы, трехфазные генераторы, генераторы меандра, сторожевые таймеры и пр.). Типичные области применения для этих микроконтроллеров – управление двигателями, модемы, контроллеры жестких и оптических дисков.

### 2.2. Микроконтроллеры фирмы Philips

Фирма Philips производит более 100 модификаций семейства MCS-51, в состав которых входят микроконтроллеры в корпусах от 24 до 80 выводов, работающие при тактовой частоте до 40 МГц и напряжении питания от 1,8 В. Изделия этой фирмы ориентированы на рынок бытовой электроники. В таких микроконтроллерах используется стандартное ядро MCS-51, дополненное широчайшим набором периферии, среди которой следует отметить: 10-разрядные АЦП; ЦАП; широтно-импульсные 8-разрядный модуляторы; массивы таймеров/счетчиков; программируемых интерфейсы I2C, CAN: специализированную периферию для телевизионной, видео- и аудиотехники. Кроме того, Philips выпускает микроконтроллеры MCS-51, обладающие функцией снижения электромагнитных помех (Lower EMI).

Новое оригинальное решение Philips по развитию архитектуры семейства MCS-51 реализовано в семействе микроконтроллеров 51XA ("расширенная архитектура 51"). При этом разработчики решили отказаться от достижения совместимости кодов команд нового микроконтроллера с 8051. Такое решение, с одной стороны, сделало невозможным прямую замену микроконтроллера MCS-51 на микроконтроллер семейства 51XA, но с другой стороны позволило создать полноценное 16-разрядное ядро, обеспечивающее почти 100-кратное увеличение быстродействия по сравнению с традиционной архитектурой MCS-51.

#### 2.3. Микроконтроллеры фирмы Atmel

Фирма Atmel является одним из мировых лидеров по производству однокристальных микроконтроллеров. Архитектура MCS-51 реализована в ее контроллерах семейства AT89, которые имеют встроенную Flash-память для хранения программ и данных, а также обладают возможностью внутрисхемного (загрузки программного программирования кода) ПО последовательному интерфейсу. Имеются также модификации микроконтроллеров этого семейства, конструктивно исполненных в 20-выводных корпусах (вместо стандартных 40выводных). Кроме того, выпускаются микроконтроллеры с архитектурой MCS-51, которые программируются по заказу покупателя на предприятии-изготовителе АТ80) или допускают (семейство лишь однократное программирование пользователем (семейство АТ87).

В настоящее время более широкое распространение получают новые изделия фирмы Atmel — 8-разрядные микроконтроллеры с AVR-ядром и 32-разрядные контроллеры с ARM-ядром. Они построены на базе RISC—процессоров и имеют более высокую производительность, чем MCS-51 при меньшем энергопотреблении.

AVR-архитектура реализована в семействе AT90 и объединяет 8-разрядный гарвардский RISC-процессор, 32 регистра общего назначения, каждый из которых может работать как аккумулятор, и развитую систему команд фиксированной

16-битной длины. Большинство команд выполняются за один машинный такт с одновременным исполнением текущей и выборкой следующей команды, что обеспечивает производительность до 1 MIPS на каждый МГц тактовой частоты.

микроконтроллеры AVR имеют встроенную Bce Flash-память возможностью внутрисхемного программирования через последовательный 4проводной интерфейс. Их периферия включает: таймеры-счётчики, широтноимпульсные модуляторы, поддержку внешних прерываний, аналоговые компараторы, 10-разрядный 8-канальный АЦП, параллельные порты (от 3 до 48 линий ввода и вывода), интерфейсы UART и SPI, сторожеой таймер и устройство три сброса включению питания. Имеется подсемейства микроконтроллеров (tiny AVR, classic AVR mega AVR), отличающиеся производительностью и объемом памяти.

AMR-архитектура реализована в семействе AT91 и основана на 32разрядном RISC-процессоре. Микроконтроллеры этого семейства отличаются наиболее высокой производительностью выпускаются различными комбинациями RAM, ROM и Flash-памяти. Их достоинством является также ЕВІ-интерфейса (External Bus Interface), обеспечивающего высокоскоростной доступ к дополнительной внешней памяти и внешним периферийным устройствам.

### 2.4. Микроконтроллеры фирмы Analog Devices

В устройствах обработки аналоговых сигналов широко применяются микроконтроллеры ADuC8xx со встроенным прецизионными АЦП и ЦАП семейства MicroConverter фирмы Analog Devices. В этих изделиях используется процессорное ядро 8051/52, встроенная Flash-память и блок ввода-вывода аналоговой информации, включающий многоканальные ЦАП и АЦП с разрядностью 12 бит и более. Имеется также встроенный датчик температуры и источник опорного напряжения с функциями термостабилизации.

В качестве типичного примера приведем технические характеристики микроконтроллера ADuC812, называемого также "однокристальной системой сбора данных". Это устройство выполнено в 52-выводном корпусе и имеет 8-разрядный микропроцессор с тактовой частотой 12-16 МГц и системой команд МСS-51, 8 Кбайт резидентной Flash-памяти программ, 640 байт резидентной Flash-памяти данных и 256 байт резидентной RAM-памяти данных. Имеется также возможность адресации до 16 Мбайт внешней памяти данных и до 64 Мбайт внешней памяти программ. Аналоговый интерфейс включает в себя 8-канальный прецизионный 12-разрядный АЦП с быстродействием 5 мкс, два 12-разрядных ЦАП, DMA контроллер для передачи данных от АЦП в память. Встроенные периферийные модули обеспечивают последовательную передачу данных через порты типа UART, SPI и I2C. Питание осуществляется от источника с напряжением от 3 до 5 В, имеется схема слежения за напряжением питания и два режима пониженного энергопотребления.

Новые изделия этой фирмы ADuC702х основаны на 32-разрядном процессорном ARM-ядре и имеют расширенный набор аналоговых входоввыходов. Они предназначены для применения в бортовой автоэлектронике и промышленной автоматике, что обеспечивается аппаратной поддержкой шин типа LIN и LIN, а также простотой сопряжения с электромагнитными, ультразвуковыми и оптическими датчиками положения.

### 2.5. PIC-микроконтроллеры фирмы Microchip

Микроконтроллеры типа PIC (Peripheral Interface Controller) появились в конце 80-х годов и составили серьёзную конкуренцию контроллерам MCS-51. В их основу была положена 8-разрядная RISC-архитектура с системой простых однословных команд (в базовой модели PIC16C5х используется только 33 команды). Все команды (кроме команд перехода) выполняются за один машинный цикл (четыре такта).

Отличительной особенностью PIC-микроконтроллеров, реализованных по CMOS-технологии, является низкое энергопотреблении: 2 мА при питании 5 В на тактовой частоте 4 мГц; 15 мкА при питании 3 В на тактовой частоте 32 кГц и менее 3 мкА в режиме ожидания. Диапазон питающих напряжений составляет от 2 В до 6 В. Это обуславливает широкое применение таких микроконтроллеров в портативных приборах с батарейным питанием.

В настоящее время Microchip выпускает четыре основных семейства 8разрядных РІС-микроконтроллеров, программно совместимых снизу вверх:

- PIC15Cx базовое семейство с 12-разрядными командами и минимальной периферией;

- PIC12Cxxx семейство с 12-разрядными командами, выпускаемое в миниатюрном 8-выводном исполнении;

- PIC16x/7x/8x/9x среднее семейство с 14-разрядными командами, средствами аналогового ввода/вывода, контроллерами SPI, USART и I2C;

- PIC17C4x/5xx высокопроизводительное семейство с 16-разрядными командами, увеличенным объёмом памяти, развитой системой ввода/вывода и повышенной тактовой частотой (до 33 МГц).

Перспективное пятое семейство РІС-контроллеров РІС18Сххх будет иметь расширенное RISC-ядро, оптимизированное под использование нового Сикомпилятора, адресное пространство программ до 2 Мбайт, до 4 Кбайт встроенной памяти данных и производительность 10 млн. операций в секунду.

### 3. Семейство микроконтроллеров MCS-48

### 3.1. Архитектура микроконтроллеров MCS-48

Микроконтроллеры семейства MCS-48 являются одним из первых представителей однокристальных ЭВМ, которые в отличие от классических процессоров имеют встроенную память, таймер и интерфейсы для связи с внешними устройствами. Это обусловило их широкое применение в системах управления, где преимущества однокристального исполнения оказались более существенными, чем некоторое снижение быстродействия, характерное для такой архитектуры. Первым представителем этого семейства стала микросхема i8048 разработанная фирмой Intel и использованная в клавиатуре первых компьютеров IBM PC. В её структуре использовано множество архитектурных элементов восьмиразрядных микропроцессоров 8080/85. Далее это семейство развивалось путём повышения степени интеграции, быстродействия (тактовой частоты) и снижения энергопотребления табл. 1.

Таблица 1 Микроконтроллеры, входящие в состав семейства MCS-48

| Тип              | Аналог   | Тип ПЗУ             | Объем<br>ПЗУ,<br>Кбайт | Объем<br>ОЗУ,<br>байт | Тактовая частота, МГц | Ток<br>потребления,<br>мА |

|------------------|----------|---------------------|------------------------|-----------------------|-----------------------|---------------------------|

|                  |          | П                   | ервое поко             | ление                 |                       |                           |

| 8035             | 1816BE35 | внешнее             | VA                     | 64                    | 6                     | 135                       |

| 8048             | 1816BE48 | с УФ -<br>стиранием | 1                      | 64                    | 6                     | 135                       |

| Второе поколение |          |                     |                        |                       |                       |                           |

| 8039             | 1816BE39 | Внешнее             |                        | 128                   | 11                    | 110                       |

| 8049             | 1816BE49 | Масочное            | 2                      | 128                   | 11                    | 110                       |

| Третье поколение |          |                     |                        |                       |                       |                           |

| 80C35            | 1830BE35 | Внешнее             |                        | 64                    | 6                     | 8                         |

| 80C48            | 1830BE48 | Масочное<br>ПЗУ     | 1                      | 64                    | 6                     | 8                         |

Все функции микроЭВМ в семействе MCS-48 реализуются с помощью единственной микросхемы. В состав семейства MCS-48 входит целый ряд микросхем с одной неизменной частью, – ядром, определяющим систему команд, что позволяет использовать для разработанного устройства микросхемы различных фирм-производителей без изменения принципиальной схемы устройства и программы. Отличия микросхем в семействе MCS-48 определяются периферийными компонентами, позволяющими выполнять как задачи управления

различными устройствами, так и реализовывать отдельные узлы аналоговой схемы.

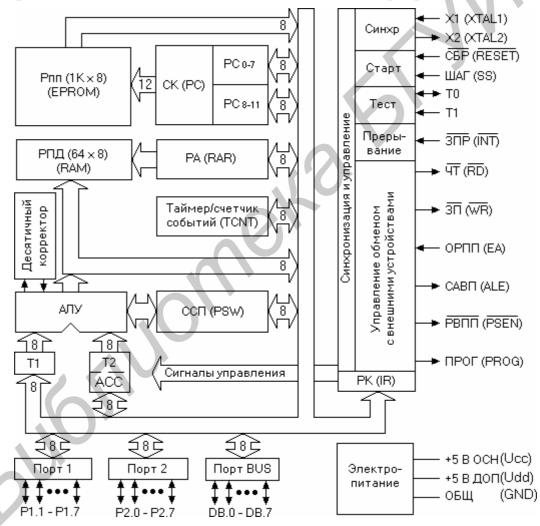

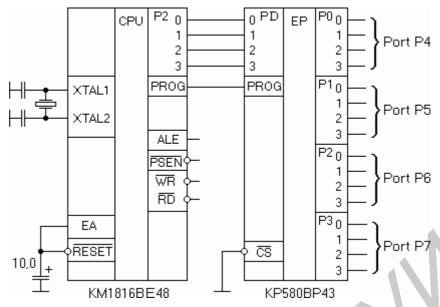

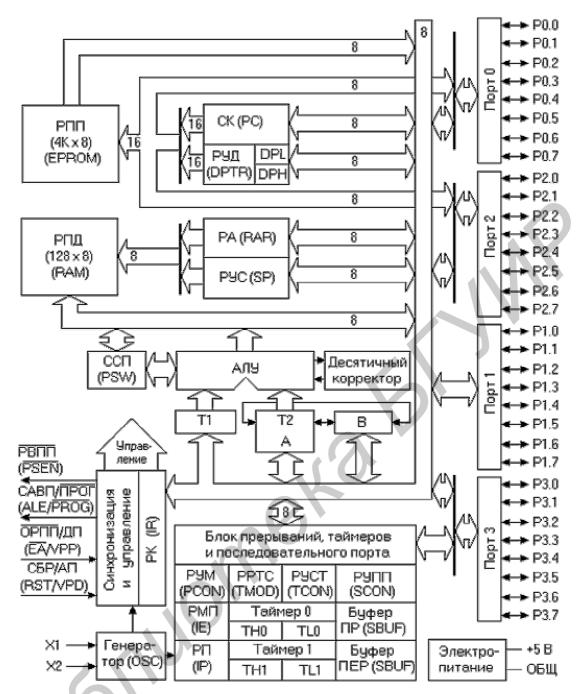

Основу микроконтроллера (рис. 1) составляет двунаправленная восьмиразрядная системная шина, связывающая между собой все основные компоненты микросхемы:

- блок синхронизации и управления;

- арифметико-логическое устройство (АЛУ);

- блок таймеров/счётчиков;

- блок последовательного интерфейса и прерываний;

- программный счётчик;

- резидентную память данных (РПД) и память программ (РПП).

Рис. 1. Структурная схема микроконтроллера 1816ВЕ48

Конструктивно микроконтроллер выполнен в корпусе БИС с 40 внешними выводами, электрически совместимыми с элементами ТТЛ. Питание МК осуществляется с помощью двух выводов: первый, — для подачи основного, и второй, — дополнительного напряжения для питания резидентной памяти данных или программирования резидентной памяти программ. К выводам X1 и X2

подключается кварцевый резонатор или внешний источник синхронизации. Сигнал SS (ШАГ) совместно с сигналом ALE (САВП) позволяет при отладке выполнять программу с остановом после исполнения очередной команды. Выводы Т1 и Т0 опрашиваются командами условного перехода и могут использоваться для подсчёта внешних событий. Сигнал запроса прерывания ЗПР от внешнего источника вызывает подпрограмму обслуживания прерывания. Высокий уровень на входе ЕА (ОРПП) заставляет МК выполнять выборку команд только из внешней памяти программ, что позволяет тестировать прикладную программу при её отладке. Этот вывод также используется для подачи напряжения программирования +25В. Контроллер имеет три параллельных восьмиразрядных порта ввода/вывода, которых BUS ИЗ порт может использоваться внешней качестве шины данных процессорного В ядра контроллера.

### 3.2. Блок управления и синхронизации

Совместную работу блоков микроконтроллера во всех режимах работы координирует блок управления и синхронизации. В его состав входят: устройство синхронизации, логика ввода-вывода, регистр команд, дешифратор команд, логика управления ЭВМ.

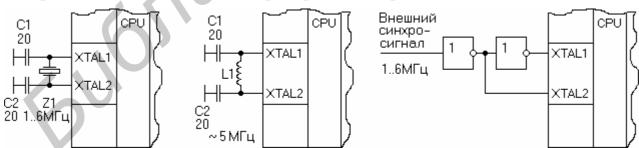

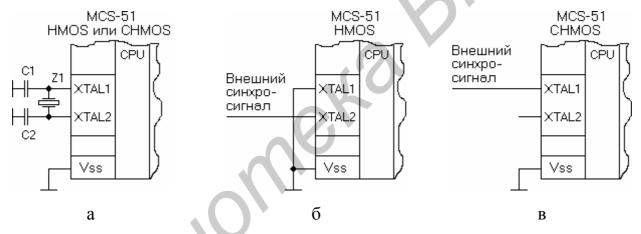

Опорную частоту синхронизации определяет либо кварцевый резонатор, подключаемый к выводам X1 и X2, либо LC-цепь (рис. 2а и 26 соответственно). X1 является входом, а X2 — выходом генератора, способного работать в диапазоне частот от 1 до 6 МГц. На вход X1 может подаваться сигнал от источника внешней синхронизации рис. 2в. В состав генератора МК входят два счётчика с модулями пересчёта 3 и 5. Первый используется для формирования сигнала системной синхронизации (0,5 мкс). Этот же сигнал поступает на счётчик машинных циклов, на выходе которого через каждые пять сигналов синхронизации формируется сигнал ALE (2,5 мкс), идентифицирующий машинный цикл и использующийся в расширенных МК-системах для стробирования адреса внешней памяти.

Рис. 2. Варианты схем синхронизации MCS-48

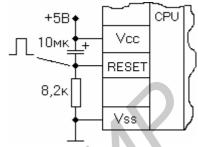

Сброс микроконтроллера в обслуживаемых МК-системах осуществляется с помощью кнопки "Сброс", которая заземляет вход RESET (рис. 3а). В необслуживаемых МК-системах, ко входу RESET подключается конденсатор ёмкостью 1 мкФ, что обеспечивает подачу сигнала близкого к потенциалу земли,

длительностью не менее 50 мкс после установки в номинальное значение напряжения питания (рис. 3б). Сигнал RESET производит следующие действия: сбрасывает счётчик команд (РС) и указатель стека (SP); устанавливает порт BUS в высокоимпедансное состояние, а порты P1 и P2 – в режим ввода (FF в выходном буфере); выбирает банк регистров 0 и банк памяти 0; запрещает прерывания; останавливает таймер и выдачу синхросигнала на вывод Т0; сбрасывает флаг переполнения таймера ТF и флаги пользователя F0 и F1.

Рис. 3. Схемы начальной установки MCS-48

Для записи и хранения восьмиразрядного кода операции выполняемой команды предназначен регистр команд. Код операции, с помощью дешифратора команд и логики управления преобразуется в микропрограмму выполнения команды, считанной из ПЗУ.

# 3.3. Арифметико-логическое устройство

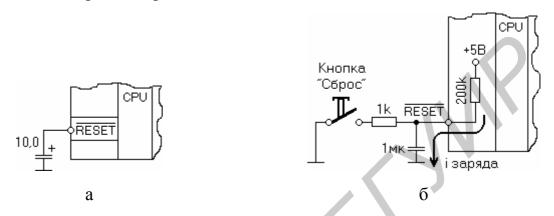

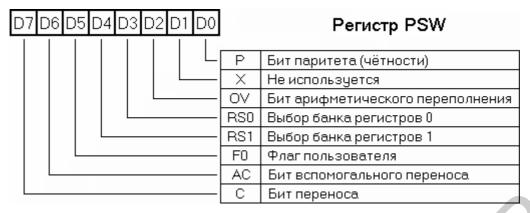

Восьмиразрядное арифметико-логическое устройство обеспечивает выполнение арифметических и логических операций и состоит из регистров временного хранения Т1 и Т2, аккумулятора (АСС), ПЗУ констант, арифметико-логического устройства и регистра слова-состояния программы (PSW).

Программно недоступные восьмиразрядные регистры временного хранения (Т1 и Т2) используются для временного хранения второго операнда при выполнении двухоперандных команд. Результат выполнения арифметикологических операций или операций сдвига сохраняется в восьмиразрядном аккумуляторе. ПЗУ констант обеспечивает генерацию корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант.

Арифметико-логическое устройство представляет собой схему комбинационного типа с последовательным переносом, предназначенную для выполнения операций сложения, вычитания и логических операций И, ИЛИ, исключающего ИЛИ, инкремента, декремента, инверсии, циклического сдвига вправо и влево, десятичной коррекции содержимого аккумулятора и обмена тетрад в байте.

При выполнении операций обработки данных в АЛУ, формируются флаги:

- переноса (С);

- вспомогательного переноса (АС);

- нулевого содержимого аккумулятора (Z);

- наличия единицы в заданном бите аккумулятора.

Следует заметить, что в регистре слова состояния программы PSW (рис. 4) сохраняются только два из этих флагов (C, AC). Остальные флаги формируются комбинационной схемой и не фиксируются, но логика условных переходов позволяет выполнять команды передачи управления (JZ, JNZ, JB0..JB7) без их фиксации триггерами. Кроме этого имеются условные переходы по "флагам пользователя" F0 и F1, по флагу переполнения таймера TF, а также по сигналам на тестируемых входах T0 и T1. Программист также имеет доступ к флагам рабочего банка регистров BS и выбранного банка внешней памяти программ MB. Кроме того, после окончания каждого машинного цикла опрашивается флаг разрешения/запрета прерывания.

Рис. 4. Формат регистра слова-состояния программы PSW

Счётчик команд (Program Counter) формирует текущий 12-разрядный адрес памяти программ. В состав счётчика команд входят регистр РС и схема инкремента одиннадцати разрядов адреса (старший разряд РС не инкрементируется).

### 3.4. Память микроконтроллеров семейства MCS-48

В семействе микроконтроллеров MCS-48 подсистема памяти реализована по гарвардской архитектуре, что предполагает её физическое и логическое разделение на память программ и память данных с отдельным адресным пространством. В этих микроконтроллерах имеется три адресных пространства: память программ, внешняя память данных (ВПД) и внутренняя (резидентная) память данных (РПД). Такое построение памяти позволяет создавать максимально надёжные системы.

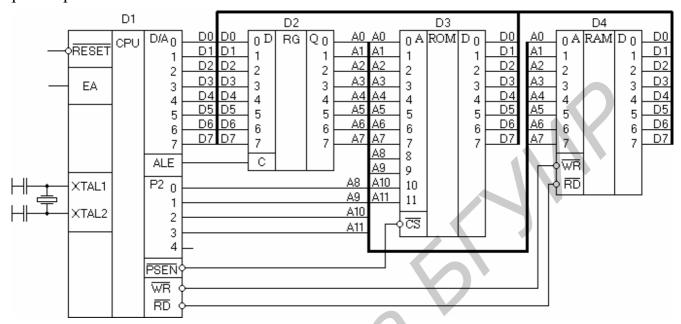

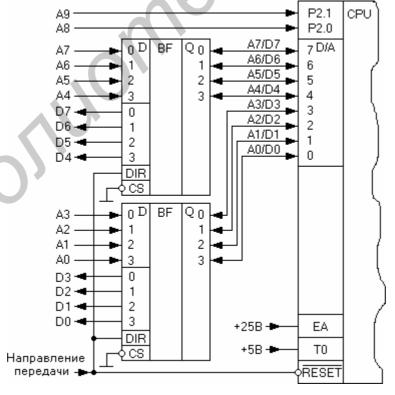

Схема подключения внешних микросхем памяти к микроконтроллерам семейства MCS-48 показана на рис. 5. Регистр адреса D2 на этой схеме

предназначен для запоминания младших восьми бит адреса, передаваемых через шину данных/памяти. Старшие четыре бита адреса передаются через шину адреса, совмещенную с портом P2. Выдача адреса сопровождается синхроимпульсом ALE, который позволяет запомнить младший байт адреса в регистре D2.

Рис. 5. Подключение внешней памяти к микроконтроллерам MCS-48

Для обращения к памяти программ D3 и к памяти данных D4 используется совмещённая шина данных/адреса BUS, а её текущее назначение определяется управляющими сигналами. При чтении памяти программ используется сигнал PSEN, а при чтении памяти данных, — сигнал RD. Запись информации в память данных осуществляется по сигналу WR.

### 3.5. Память программ

Память программ, размещённая на кристалле микроконтроллера, называется резидентной (РПП) и представляет собой постоянное запоминающее устройство. В семейство MCS-48 входят микроконтроллеры с различным объёмом резидентной памяти программ, а у 1816BE35 РПП отсутствует, поэтому они могут работать только с внешней микросхемой ПЗУ ёмкостью до 4 Кбайт. Максимальное адресное пространство памяти программ составляет 4 Кбайта, поэтому счётчик команд двенадцатиразрядный (4 Кбайт =  $4096 = 2^{12}$  байт). Адреса РПП находятся в диапазоне 000h..3FFh. После сброса микроконтроллера выполнение программы начинается с нулевого адреса, соответствующего внутреннему ПЗУ микроконтроллера.

Микроконтроллеры семейства MCS-48 имеют вывод EA, с помощью которого можно запретить работу внутренней памяти, подав на этот вход логический "0". При этом, начиная с нулевого адреса, все обращения происходят

к внешней памяти программ. Поэтому доступ к внешней памяти программ осуществляется в двух случаях:

- 1. при подаче сигнала ЕА=0 независимо от адреса обращения,

- 2. в случае, если счётчик команд (PC) содержит число большее, чем 3FFh.

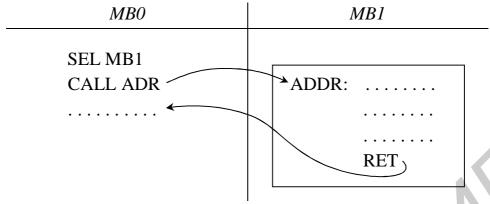

Следует заметить, что при выполнении программы инкрементируются только младшие 11 бит счётчика команд. Поэтому программа из предельного адреса 7FFh (если только по этому адресу не расположена команда передачи управления) перейдёт по адресу 0000h. Состояние старшего бита счётчика команд может быть изменено специальными командами (SEL MB0 и SEL MB1) совместно с командами безусловного перехода JMP и вызова подпрограмм CALL. При этом следует учитывать, что команды SEL MB0 и SEL MB1 изменяют только флаг MB и не воздействуют непосредственно на старший бит счётчика команд. Изменение этого бита осуществляется командами JMP и CALL, которые копируют текущее содержимое MB в старший бит счётчика команд. Поэтому для перехода из нулевого банка в первый требуется выполнить последовательность команд SEL MB1, JMP adr1.

При выполнении переходов между банками по командам SEL MB, необходимо следить за тем, чтобы подпрограммы, взаимно вызывающие друг друга, располагались в пределах одного банка памяти. Иначе возникает необходимость модификации флага MB в вызываемой подпрограмме и восстановления его при возврате в вызывавшую подпрограмму. Но если вызов такой подпрограммы носит условный характер, то проблема восстановления флага может оказаться неразрешимой.

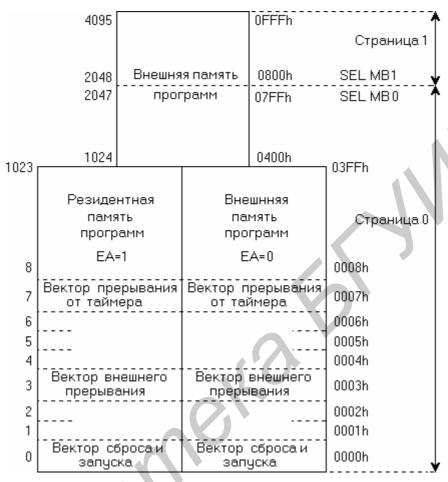

Неполная (11-битная) инкрементация счётчика команд приводит к тому, что память программ разделяется на два банка ёмкостью по 2 Кбайта. Кроме того, в командах условного перехода задаётся 8-битный адрес, что обуславливает разбиение памяти программ на 16 страниц по 256 байт. В случае, когда в программе необходимо иметь много условных переходов, из-за небольшого размера страницы возникает проблема размещения соответствующих программных модулей на двух страницах. Для решения этой проблемы используют комбинации команд условного перехода с 8-разрядным адресом и команды безусловного перехода с 11-разрядным адресом. Адресное пространство памяти программ при этом распределено, как показано на рис. 6.

В резидентной памяти программ имеется три специализированных адреса:

- адрес 0, которому передаётся управление по сигналу RESET; по этому адресу должна находиться команда безусловного перехода к началу программы;

- адрес 3, по которому передаётся управление по сигналу внешнего прерывания;

- адрес 7, по которому передаётся управление по прерыванию от таймера/счётчика.

При обработке запросов прерываний в МК48 старший бит счётчика команд принудительно устанавливается в 0. Это приводит к необходимости располагать подпрограмму обслуживания прерывания и все вызываемые ею подпрограммы в нулевом банке памяти.

Рис. 6. Карта адресов памяти программ 1816ВЕ48

Семейство MCS-48 имеет несколько модификаций, отличающихся объёмом резидентной памяти программ. При использовании портов P1 и P2 в качестве дополнительных адресных расширителей объём внешней памяти программ может быть увеличен до 16 Мбайт.

#### 3.6. Память данных

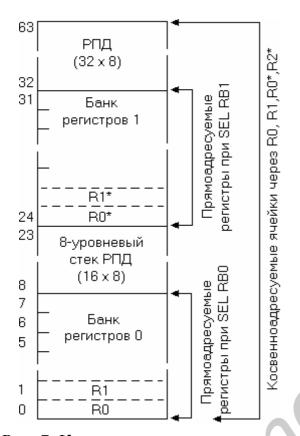

Резидентная память данных (РПД) ёмкостью 64 байта имеет в своём составе два банка рабочих регистров R0...R7, причём программист может выбрать один из них в качестве активного. Для размещения регистров используются ячейки памяти 0-7 и 24-31 (рис. 7), поэтому символу R0 в программе может соответствовать как ячейка памяти 0, так и ячейка с адресом 24. Такая организация позволяет сократить время обработки прерываний, так как вместо традиционного сохранения содержимого регистров в стеке можно переключить активный банк регистров. Выбор активного банка регистров выполняется командой SEL RB.

Любая ячейка РПД доступна по командам с косвенной адресацией через регистры R0, R1. При этом используются символы @R0 и @R1. Однако при адресации ячеек 0-7 и 24-31 предпочтительно использовать символы R0...R7, соответствующие прямой регистровой адресации.

В РПД размещается также стек объёмом 16 байт, имеющий 8 уровней по 2 байта (область памяти с адресами 8-23). В качестве указателя стека используются три разряда слова состояния программы PSW. В стеке сохраняется адрес возврата ИЗ подпрограммы (12 разрядов) и старшая тетрада PSW (4 разряда).

При уровне вложенности подпрограмм меньше восьми, незадействованные в стеке ячейки могут использоваться как ячейки РПД. При переполнении стека трёхбитный указатель стека переходит из состояния 7 в состояние 0.

Семейство MCS-48 не имеет команд загрузки байта в стек или его извлечения из стека, обычно используемые при обработке

Рис. 7. Карта адресов памяти данных прерываний. Поэтому программист должен следить за тем, чтобы вложенные подпрограммы не использовали одни и те же рабочие регистры.

Практически все команды с обращением к РПД оперируют с одним байтом. Однако по командам вызова и возврата осуществляется доступ к двухбайтным словам. В памяти данных слова хранятся так, что старший байт располагается в ячейке с большим адресом. Отметим, что в памяти программ порядок расположения байтов по старшинству при хранении двухбайтных слов обратный.

В МК-системах с внешней памятью данных адресация осуществляется также через регистры R0 и R1 (символы @R0 и @R1), что обеспечивает доступ к памяти объёмом 256 байт.

### 3.7. Организация ввода/вывода информации

Для организации ввода/вывода информации микроконтроллеры семейства MCS-48 имеют 27 линий, в том числе три параллельных порта (BUS, P1 и P2) по восемь линий в каждом, а также три линии, которые могут использоваться для изменения хода программы по командам условного перехода и сигналу прерывания:

- INT для ввода в МК сигнала запроса прерывания от внешнего источника либо для ввода тестируемого сигнала;

- T0 для ввода тестируемого сигнала от двоичного датчика (по команде ENT0 CLK по этой линии выдается сигнал синхронизации);

- T1 для ввода тестируемого сигнала или ввода импульсов для счётчика событий, который запускается по команде STRT CNT.

**Порт BUS** является двунаправленным и имеет буферные каскады с тремя состояниями. Он может использоваться либо в качестве шины данных/адреса при подключении внешней памяти, либо как параллельный порт ввода/вывода.

При подключении внешней памяти данных на линиях порта BUS сначала выставляется 8-разрядный адрес, сопровождаемый сигналом ALE. Затем по тем же линиям порта BUS производится передача байта данных, стробируемых сигналами RD или WR (при чтении или записи соответственно). Поэтому на время передачи данных адрес должен фиксироваться во внешнем регистре (см. рис. 5, регистр D2).

При подключении внешней памяти программ требуется формировать 12-разрядный адрес, младшие 8 разрядов которого передаются аналогично (по линиям порта BUS в сопровождении сигнала ALE) и также запоминаются во внешнем регистре. Старшие 4 разряда передаются через порт P2 (линии P2.0..P2.3) и в течение машинного цикла не изменяются, поэтому для старших разрядов адреса буферизация не требуется. Данные из внешней памяти программ передаются в микроконтроллер в сопровождении сигнала PSEN (РВПП); очевидно, что запись в память программ невозможна.

При работе порта BUS в режиме параллельного интерфейса вывод/вывод выполняется командами OUTL и INS. Кроме того, вводимые и выводимые через порт BUS данные можно модифицировать с помощью команд ORL BUS, #d и ANL BUS, #d, что позволяет выделять и обрабатывать в байте отдельный бит или группу бит. Такая операция называется маскированием.

Заметим, что обмен данными через порт BUS осуществляется командами пересылки MOVX, а также ввода/вывода OUTL и INS. При этом в случае записи во внешнюю память данных командой MOVX  $@R_i$ , А или выводе данных через порт командой OUTL BUS, А соответствующий байт фиксируется в буферном регистре и сохраняется на выводах микроконтроллера до выполнения следующей команды такого типа. Однако при чтении данных командой MOVX A,  $@R_i$  содержимое буфера уничтожается, в то время, как команда ввода INS не изменяет содержимое буферного регистра. Поэтому при работе с портом BUS не рекомендуется попеременное использование команд пересылки данных и команд ввода/вывода.

В отсутствие передач данных линии порта BUS отключаются от нагрузки, переходя в высокоимпедансное состояние.

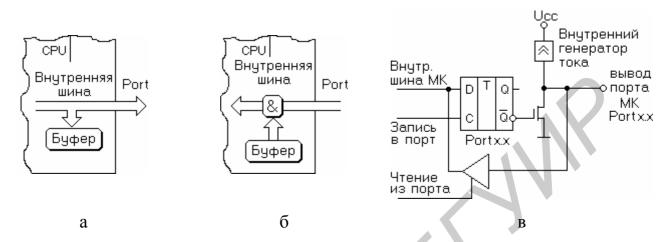

**Порты ввода/вывода Р1 и Р2** являются квазидвунаправленными. Это означает, что вывод информации осуществляется аналогично порту BUS (без 22

искажений), но при вводе производится операция поразрядного логического "И" между входными сигналами и содержимым буфера (рис. 8). Поэтому для ввода данных без изменений перед операцией чтения IN необходимо записать во все разряды буфера логические единицы. Заметим, что по сигналу RESET в буферные регистры портов P1 и P2 автоматически записывается FFh.

Рис. 8. Функциональная схема квазидвунаправленного порта: а – в режиме вывода, б – в режиме ввода данных; в – для одного разряда порта

Для ввода/вывода информации через порты P1 и P2 используются команды IN и OUTL:

IN A, P1 ; ввести данные из порта P1 в аккумулятор OUTL P2, A ; вывести данные из аккумулятора в порт P2.

Квазидвунаправленная структура портов позволяет аппаратно выполнять *маскирование* требуемых линий при вводе, т.е. запись нулей в заданный разряд или группу разрядов. Например, если требуется обрабатывать только младшие 4 линии порта P2, то можно использовать последовательность команд:

MOV A, #0Fh ; запись маски в аккумулятор;

OUTL P2, A ; загрузка маски в буфер порта P2;

IN A, P2 ; ввод младшей тетрады и маскирование старшей,

выполнение которых обеспечивает запись в нулей в старшую тетраду аккумулятора. Следует учитывать, что текущее содержимое буфера P1 и P2 для чтения не доступно, поэтому программист должен быть уверен, что в буфере находится требуемая маска (в противном случае ее необходимо загрузить повторно).

Порты P1 и P2 архитектурно идентичны, за исключением четырёх младших линий порта P2, которые могут использоваться для:

- выдачи старшей тетрады адреса ВПП,

- подключения расширителя КР580ВР43 (рис. 9), позволяющего увеличить количество линий ввода/вывода на шестнадцать (четыре четырёхразрядных порта Р4-Р7).

Рис. 9. Подключение расширителя ввода/вывода

Кроме обычных команд ввода/вывода IN, OUTL для изменения состояния линий P1, P2 можно использовать и логические команды ANL, ORL. Например:

ANL P1, #11100111b; Установить логический "0" на линиях P1.3 и P1.4 ORL P2, #00011000b; Установить логическую "1" на линиях P2.3 и P2.4 Такой приём позволяет заменить одной командой последовательность из трёх команд (ввод, логическая операция с аккумулятором, вывод).

### 3.8. Система обработки прерываний

Система прерываний представляет собой механизм, позволяющий реагировать на особые состояния, возникающие при работе системы управления (срабатывание датчика аварийной ситуации, пропадание питания и т.д.). С точки зрения программиста прерывание — это принудительная приостановка текущей программы и переход на выполнение другой программы (обработчика прерывания), после завершения которой управление возвращается прерванной программе.

Микроконтроллеры семейства MCS-48 позволяют обрабатывать прерывания от двух источников:

- внешнего сигнала на входе INT (адрес вектора прерывания 3);

- флага переполнения таймера-счётчика (адрес вектора прерывания 7).

Прерывание от внешнего источника возникает, когда на входе INT появляется низкий уровень. Состояние сигнала на этом входе анализируется во время выдачи сигнала ALE (в каждом машинном цикле), а обработка прерывания начинается после завершения текущей команды. При обработке внешнего прерывания выполняются следующие действия:

содержимое счётчика команд (адрес возврата, 12 разрядов) и старшей тетрады слова состояния программы (флаги, 4 разряда) сохраняется в стеке; – в счётчик команд записывается значение 003h (по этому адресу должна находиться команда JMP, обеспечивающая переход к обработчику прерывания, расположенному в MB0).

Обработка прерывания должна заканчиваться командой RETR, по которой:

- восстанавливается из стека содержимое счётчика команд (адрес возврата) и старшей тетрады слова состояния программы;

- продолжается выполнение прерванной программы.

Ко входу INT микроконтроллера через «монтажное ИЛИ» могут быть подключены несколько источников прерываний, однако другие запросы прерываний игнорируются до выхода из подпрограммы обработки по команде RETR. В этом случае источник прерывания определяется программно (необходимо предусмотреть возможность ввода сигналов от всех источников прерываний через порт P1 или P2).

Поскольку система прерываний MCS-48 реагирует на уровень сигнала на входе INT (а не на переход из "1" в "0"), то для исключения повторных прерываний сигнал INT должен быть снят до выполнения команды RETR. Эта операция должна выполняться автоматически, в противном случае обработчик прерываний должен снять низкий уровень с линии INT через какую-либо линию порта P1 или P2.

Прерывания от таймера/счётчика возникают, когда флаг переполнения ТF устанавливается в "1". Они обрабатываются аналогично, но переход осуществляется по адресу 007h. Кроме того, флаг TF сбрасывается автоматически при переходе на подпрограмму обработки прерывания.

Приоритет внешнего прерывания выше приоритета прерывания от внутреннего таймера. Это означает, что в случае одновременного запроса прерываний от внешнего источника и запроса от флага переполнения таймера приоритет остается за источником, воздействующим на вход INT.

При необходимости, в МК можно создать двухуровневую систему прерываний. Для этого необходимо загрузить в таймер/счётчик число FFh и перевести его в режим счётчика. Тогда изменение сигнала на входе Т1 из "1" в "0" приведёт к прерыванию по вектору 007h.

Внешние прерывания могут быть запрещены командой DIS I и разрешены командой EN I. Для разрешения и запрещения прерываний от таймера используются команды EN TCNTI и DIS TCNTI. Сигнал RESET запрещает прерывания от обоих источников. Если внешние прерывания запрещены, то вход INT может быть проверен командой условного перехода JNI (при этом он используется в качестве дополнительного тестируемого входа подобно T0 и T1).

При входе в подпрограммы обслуживания прерывании старший бит счётчика команд  $PC_{11}$  принудительно устанавливается в нуль. Поэтому обработчики прерываний должны размещаться в банке памяти MB0.

### 3.9. Таймер/счётчик

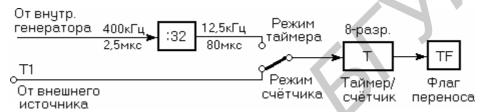

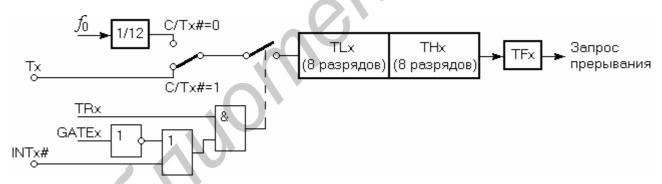

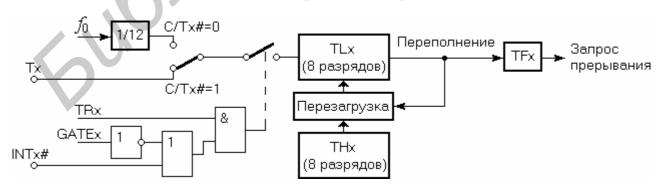

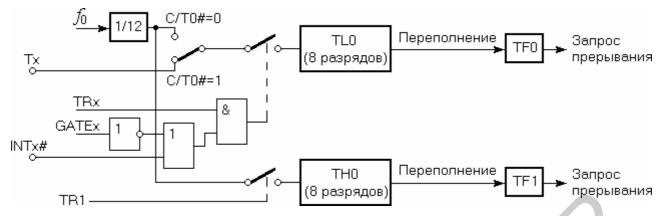

MCS-48 имеет встроенный восьмиразрядный таймер/счётчик (рис. 10), который может подсчитывать импульсы от внутреннего генератора (режим таймера) или импульсы от внешнего источника (режим счётчика).

В режиме таймера через делитель частоты на 32 поступают сигналы основной синхронизации с периодом 2,5 мкс (400 кГц), поэтому состояние счётчика увеличивается на 1 каждые 80 мкс (12,5 кГц). Путём программной установки таймера/счётчика в исходное состояние и анализа флага переполнения могут быть реализованы различные временные задержки, лежащие в диапазоне от 80 мкс до 20,48 мс. Временные задержки, превышающие по длительности 256 состояний счётчика (20,48 мс), могут быть получены накоплением переполнений в рабочем регистре. Заметим, что период работы таймера 20,48 мс примерно соответствует частоте 50  $\Gamma$ ц.

Рис. 10. Таймер микроконтроллеров семейства MCS-48

В режиме счётчика производится аппаратный подсчёт внешних импульсов, поступающих на тестируемый вход Т1. При этом состояние счётчика изменяется в момент перехода входного сигнала из "1" в "0". Количество подсчитанных импульсов можно прочитать командой MOV A, Т. Минимальная длительность импульса на входе Т1 равна 0,5 мкс, а минимальное время между импульсами — 7,5 мкс (при частоте кварцевого резонатора 6 МГц).

Из максимального состояния FFH таймер/счётчик переходит в начальное состояние 00H, при этом устанавливается флаг переполнения TF, что вызывает прерывание по вектору 007h (если оно разрешено командой EN TCNTI). Если прерывания от таймера/счётчика запрещены, то флаг переполнения может быть опрошен командой условного перехода JTF. Выполнение команды JTF, как и переход к подпрограмме обработки прерывания, сбрасывает флаг TF.

Выбор режима работы таймера/счётчика осуществляется специальными командами. Команда STRT Т включает режим таймера, команда STRT CNT включает режим счётчика, а команда STOP TCNT останавливает как таймер, так и счётчик. Заметим, что сигнал RESET также останавливает таймер/счётчик.

Если требуется реализовать временную задержку, кратную 80 мкс, но меньшую 20,48 мс, то можно предварительно загрузить в таймер число, соответствующее количеству тактов в дополнительном коде. Например, для формирования временного интервала 4 мс (50 тактов по 80 мкс) загружается константа 256-50=206, что соответствует CEh:

MOV A, #CEh ; количество периодов (в дополнительном коде)

MOV T, A ; загрузка таймера

STRT Т ; запуск таймера

M0: JTF M1 ; ожидание переполнения таймера

JMP M0

M1: STOP TCNT ; остановка таймера

На основе этой программы также можно реализовать задержки большей длительности. Для этого используется регистр, в который заносится требуемое переполнений таймера, И организуется цикл, внутри которого осуществляется ожидание переполнения флага ТГ. Заметим, что наиболее эффективно таймер используется в режиме прерываний, когда для обнаружения переполнения не используются ресурсы процессора (при этом процессор может программу, обеспечивающую, выполнять другую например, отображение информации или анализ нажатия клавиш).

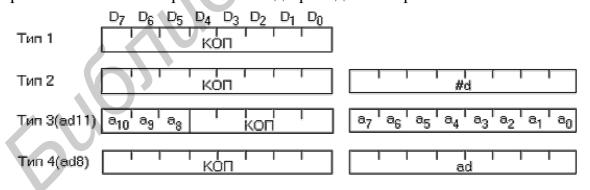

## 3.10. Система команд MCS-48

Система команд микроконтроллеров семейства MCS-48 содержит 96 базовых команд, имеющих длину один или два байта. Большинство команд являются однобайтными и выполняются за один машинный цикл длительностью 2,5 мкс (при частоте 6 МГц). Двухбайтные команды выполняются за 5 мкс.

В микроконтроллерах реализована как побайтовая (8 бит) так и потетрадная (4 бита) обработка данных. К достоинствам системы команд MCS-48 можно отнести: эффективный ввод/вывод, включая маскирование и возможность управления отдельными битами портов; возможность ветвления по значению отдельных бит; возможность обработки как двоичных, так и десятичных двоично-кодированных чисел. Форматы команд приведены на рис. 11.

Рис. 11. Типы команд МК48 (КОП – код операции, #d – непосредственный операнд,  $a_{10..0}$  – адрес)

Систему команд микроконтроллера условно можно разбить на пять групп: арифметические, логические, команды передачи данных, команды ветвления программ и передачи управления, команды управления режимами. В MCS-48 используются четыре способа адресации:

1. **Непосредственная**, – в теле команды содержится восьмибитный операнд (во втором байте команды):

MOV A, #05h ;

$$(A) \leftarrow 05h$$

2. Прямая, – в теле команды содержится адрес операнда (номер регистра):

MOV A, Rn ;

$$(A) \leftarrow (Rn)$$

3. **Косвенная**, – в теле команды содержится адрес адреса операнда (номер регистра, в котором расположен адрес ячейки памяти):

MOV A, @R0 ;

$$(A) \leftarrow ((R0))$$

Косвенная адресация допускается только через два регистра: @R0 или @R1.

4. **Неявная**, — операнд или его адрес не указывается в явном виде, а определяется кодом операции (по умолчанию). Обычно таким операндом является содержимое аккумулятора:

Хотя в мнемонике этой команды аккумулятор указывается явно, в формате команды нет адресного поля (т.е. неявно подразумевается, что операндом может быть только аккумулятор).

#### 3.11. Команды пересылки данных

С помощью этих команд можно произвести копирование либо обмен данных. Ячейка памяти или регистр, в котором располагается исходный байт называется *источником* S (source), а ячейка или регистр, в который производится копирование, — *приёмником* D (destination). Для рассматриваемого микроконтроллера команды пересылки записываются в виде MOV D, S, т.е. сначала указывается приёмник, а затем источник.

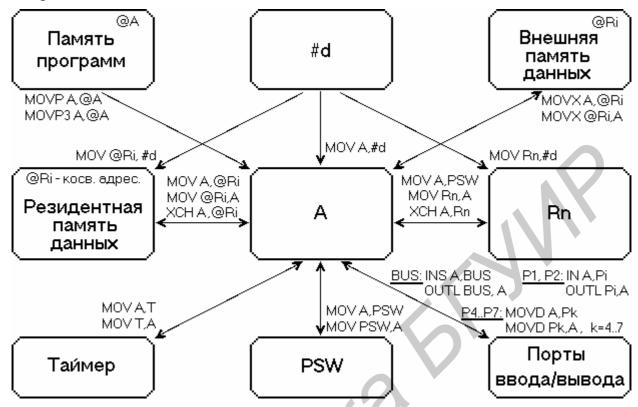

В семействе MCS-48 источником и приёмником могут быть аккумулятор A, регистры R0..R7, ячейки памяти, порты ввода/вывода, а также регистр таймера Т и слово состояния процессора PSW. Однако система команд не позволяет переслать данные из любого источника в любой приёмник, поэтому большинство пересылок выполняется через аккумулятор (рис. 11).

Передача данных возможна в двух режимах: *пересылки* (загрузки) и *обмена*. При этом команды пересылки не изменяют содержимого источника, а команды обмена изменяют значения обоих операндов, участвующих в операции. Команды пересылки внутри микроконтроллера выполняются за один машинный цикл, обмен с внешней памятью и портами требует двух машинных циклов. Все команды пересылки (кроме MOV PSW, A) не изменяют флаги.

Схема возможных пересылок представлена на рис. 12, где показаны 9 типов операндов: аккумулятор A, регистры общего назначения R0..R7, PSW, таймер, порты, непосредственный операнд #d, внешняя и резидентная память данных, а также память программ (только для чтения). Большинство команд выполняет пересылку 8-битных операндов. Существуют также несколько команд,

оперирующих с четырёхбитными операндами (при обращении к 4-битным портам расширителя ввода/вывода Р4..Р7).

Рис. 12. Команды пересылки данных MCS-48

Так как в микроконтроллере существуют три независимых области памяти, а также порты ввода/вывода, то для обращения к ним используются различные команды:

- MOV, XCH пересылка данных внутри микроконтроллера;

- MOVX пересылка данных между аккумулятором и ВПД;

- MOVP пересылка данных из памяти программ;

- IN, OUTL, MOVD пересылка из портов в аккумулятор и наоборот.

Для обращения к резидентной памяти данных используется косвенная адресация через регистры R0 и R1:

**MOV** A, @R0 ; переслать в аккумулятор содержимое ячейки РПД с

адресом, хранящемся в R0;

**MOV** @R1, A ; переслать содержимое аккумулятора в ячейку РПД с

адресом, хранящемся в R1.

Для аккумулятора и регистров можно выполнить также команду обмена:

**ХСН** A, R0 ; обменять содержимое аккумулятора с содержимым регистра R0 текущего банка.

В памяти программ наряду с командами можно располагать таблицы функций  $sin\ x,\ cos\ x,\ sqrt\ x,\ a$  также константы  $\pi,\ e$  и др. Их можно скопировать в аккумулятор с помощью команд с косвенной адресацией:

**MOVP** A, @A ; переслать в аккумулятор байт из текущей страницы

памяти программ (адрес внутри страницы содержится

в аккумуляторе);

**MOVP3** A, @A ; переслать в аккумулятор байт из третьей страницы

памяти программ (адреса – 300h..3FFh).

Для обращения к внешней памяти данных также используется косвенная адресация через регистры R0 и R1:

**MOVX** A, @R0 ; переслать в аккумулятор содержимое ячейки ВПД с

адресом, хранящемся в R0;

**MOVX** @R1, A ; переслать содержимое аккумулятора в ячейку ВПД

с адресом, хранящемся в R1.

Для работы с параллельными портами используется команды ввода/вывода IN и OUTL (для 8-разрядных операндов) и команды MOVD (для 4-разрядных операндов):

**IN** A, P0 ; ввести байт из порта P0 в аккумулятор;

**OUTL** P1, A ; вывести байт из аккумулятора в порт P1;

**MOVD** A, P4 ; ввести данные из порта P4 в младшую тетраду

аккумулятора (старшая тетрада обнуляется);

**MOVD** P7, A ; вывести данные из младшей тетрады аккумулятора в

порт Р7.

При использовании команд пересылки данных следует учитывать, что большинство из них не изменяет флагов переноса С и полупереноса АС (за исключением команды MOV PSW, A). Кроме того, поскольку символы R0..R7 могут обозначать две различные области РПД, то необходимо корректно управлять выбором текущего банка регистров (команды SEL MB0 и SEL MB1, а также MOV PSW, A).

# 3.12. Арифметические команды

В системе команд микроконтроллера имеются следующие арифметические команды, позволяющие выполнять операции над 8-битными целыми числами:

- ADD сложение однобайтных чисел;

- ADDC сложение с учетом флага переноса;

- INC инкрементирование (увеличение на 1);

- DEC декрементирование (уменьшение на 1);

- DA двоично-десятичная коррекция.

Команды сложения ADD, ADDC и DA формируют два флага: С (перенос из старшего разряда) и AC (полуперенос, т.е. перенос из младшей тетрады в старшую). Эти флаги используются для выполнения условных переходов, двоично-десятичной коррекции, а также для сложения многобайтных чисел.

Заметим, что команда вычитания отсутствует, поэтому соответствующая операция выполняется программно (при помощи инверсии и сложения). При этом используются два способа, основанные на применении дополнительного кода

$$a-b=a+\mathcal{I}K(b)=a+(\overline{b}+1)$$

,

либо обратного кода:

$$a - b = \overline{(\overline{a} + b)}.$$

Например:

$$2E_{16} - 04_{16} = 2E_{16} + \mathcal{I}K(04_{16}) = 2E_{16} + (\overline{04_{16}} + 1) = 2E_{16} + (FB_{16} + 1) = 2A_{16},$$

$$2E_{16} - 04_{16} = (\overline{2E_{16}} + 04_{16}) = (\overline{D1_{16} + 04_{16}}) = \overline{D5_{16}} = 2A_{16}.$$

Более сложные операции, такие как умножение или деление, также могут быть реализованы программным способом.

Напомним, что команды сложения ADD и ADDC выполняют операции сложения над однобайтными двоичными числами, которые могут интерпретироваться двумя способами:

- 8-разрядное число без знака (unsigned) с диапазоном  $0..255_{10}$ ;

- 8-разрядное число со знаком (signed) с диапазоном  $-128_{10}..+127_{10}$ , в котором старший разряд является знаковым ("1"означает минус, "0" плюс).

Например, число  $FE_{16}$  может рассматриваться как  $254_{10}$  либо как  $-2_{10}$ . При этом операции выполняются по законам двоичной арифметики.

Для сложения по законам десятичной арифметики используется последовательность команд

ADD A, ... ; двоичное сложение операндов

DA A ; десятичная коррекция результата

При этом слагаемые представляются в двоично-десятичном коде, при котором каждой цифре десятичного числа выделяется отдельная тетрада, например  $25_{10} = 0010'0101_{2/10}$  (следует учитывать, что в традиционной двоичной кодировке это число соответствует  $37_{10}$ ). В команде DA A реализован следующий алгоритм:

- 1. если после сложения значение младшей тетрады больше 9 или установился флаг АС, то к содержимому аккумулятора прибавляется 6;

- 2. если после этого значение старшей тетрады больше 9 или установлен флаг С, то к старшей тетраде прибавляется 6.

Например:

$$25_{10} + 09_{10} \rightarrow (25_{16} + 09_{16}) +$$

коррекция ADD:  $25_{16} + 09_{16} = 2E_{16}$  DA A:  $2E_{16} + 06_{16} = 34_{16} \rightarrow 34_{10}$

При вычитании по законам двоично-десятичной арифметики используется сложение с дополнительным кодом (дополнение до  $100_{10}$ ), которое осуществляется следующим образом:

$$a-b = a + AK(b) = a + (100_{10} - b) \rightarrow a + (99_{16} - b) + 1$$

,

где двоичное вычитание осуществляется с помощью обратного кода:

$$99_{16} - b = \overline{99 + b} = \overline{66 + b}$$

.

При использовании арифметических операций следует учитывать, что команды INC и DEC не изменяют флаги C и AC.

#### 3.13. Логические команды

Система команд микроконтроллеров MCS-48 позволяет выполнять следующие логические операции над байтами:

- ANL логическое "И" аккумулятора с операндом;

- ORL логическое "ИЛИ" аккумулятора с операндом;

- XRL логическое "Исключающее ИЛИ" аккумулятора с операндом;

- CLR A очистка содержимого аккумулятора (обнуление);

- CPL A инвертирование содержимого аккумулятора.

Эти операции выполняются побитно, а результат помещается в аккумулятор. Команды ANL, ORL, XRL и CPL A не воздействуют на флаги. Команда CLR A очищает флаг C.

Существуют также логические команды (ANL, ORL), результат выполнения которых помещается в буфер порта ввода/вывода BUS, P1, P2. Аналогичные команды (ANLD, ORLD) имеются для четырёхразрядных портов P4..P7. Это позволяет эффективно управлять значениями отдельных бит при вводе/выводе информации.

ORL P1, #00001000b ; установить третий бит порта P1;

ANL P2, #10111111b ; сбросить шестой бит порта P2.

Кроме того, имеются команды, позволяющие выполнять операции над отдельными битами:

- CLR C; CLR F0; CLR F1 сброс флагов;

- CPL C; CPL F0; CPL F1 инвертирование флагов.

Для установки флагов в "1" используется последовательность команд CLR, CPL.

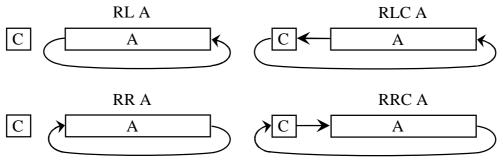

К группе логических команд относятся и команды циклического сдвига содержимого аккумулятора RL, RR, RLC, RRC (рис. 13). На основе команд RRC, RLC можно реализовать арифметический сдвиг, т.е. умножение и деление на 2 (при умножении перед сдвигом во флаг С необходимо занести 0, а при делении – скопировать в него знаковый разряд аккумулятора).

Рис. 13. Выполнение команд циклического сдвига

К этой группе команд относится и обмен местами старшей и младшей тетрад внутри аккумулятора (SWAP A), которая необходима при вводе/выводе тетрад в порты P4..P7.

### 3.14. Команды передачи управления

Команды передачи управления позволяют изменить естественный ход выполнения программы. Обычно при выполнении программы содержимое счётчика команд последовательно увеличивается на 1 или 2 (для однобайтных и двухбайтных команд соответственно). А команды передачи управления изменяют эту последовательность и приводят к записи в счётчик команд нового значения.

В микроконтроллерах семейства MCS-48 имеются две команды безусловного перехода:

- JMP ad11 безусловный переход (с 11-разрядным адресом);

- ЈМРР @ А безусловный переход в текущей странице ПП

и 20 команд условного перехода (с 8-разрядным адресом):

- JZ, JNZ переход по нулевому/ненулевому содержимому аккумулятора;

- JC, JNC переход по установленному/сброшенному флагу С;

- ЈВО...ЈВ7 переход по единичному значению бита аккумулятора;

- JF0, JF1 переход по единичному значению флагов F0 и F1;

- JTF переход по переполнению таймера (установке флага TF);

- JT0, JNT0 переход по высокому/низкому уровню на входе T0;

- JT1, JNT1 переход по высокому/низкому уровню на входе T1;

- JNI переход по низкому уровню на входе прерывания INT.

Команда безусловного перехода JMP задаёт 11-разрядный адрес ad11. Однако для полной адресации памяти программ объёмом 4 Кбайт требуется 12 разрядов. Поэтому она позволяют осуществить переход в пределах банка MB0 или MB1 объёмом по 2 Кбайт. Номер банка определяется флагом DBF, значение которого копируется в старший бит счётчика команд ( $PC_{11}$ ). А сам флаг DBF управляется командами SEL MB0 и SEL MB1. Такая логика формирования адреса

перехода приводит к тому, что для переключения банков памяти программ требуется выполнить две команды:

SEL MB1 ; изменить номер банка во флаге DBF; JMP ad11 ; перейти по адресу ad11 в банке MB1.

При этом собственно переключение банка ( $PC_{11} = 1$ ) происходит по команде JMP, а команда SEL используется для подготовки переключения.

Остальные команды ветвления содержат только 8-разрядный адрес, который копируется в младшие разряды счётчика команд  $PC_0..PC_7$ . При этом его старшие разряды  $PC_8..PC_{11}$  не изменяются. Поэтому переход осуществляется только в пределах одной страницы объёмом 256 байт. Это порождает проблему перехода с одной страницы на другую, которая решается путём комбинирования команд условного перехода и команды безусловного перехода JMP, например вместо команды JC ad8 выполняется последовательность команд:

| Переход в пределах<br>одной страницы | Переход на другую<br>страницу |

|--------------------------------------|-------------------------------|

| JC M1 $\supset$                      | JNC M0)                       |

| M1:                                  | JMP M1<br>M0:                 |

|                                      | <b>⁴</b> M1:                  |

Если команда перехода с 8-разрядным адресом расположена на границе двух страниц (т.е. первый байт команды на одной странице, а второй – на следующей), то переход будет выполнен в пределах той страницы, где располагается второй байт команды.

В отличие от классических процессоров микроконтроллеры семейства MCS-48 не имеют команд перехода по положительному и отрицательному результату. Однако имеются команды JB0...JB7, позволяющие выполнить анализ любого бита аккумулятора. Поэтому для условного перехода по отрицательному результату используется команда JB7, а для перехода по положительному результату предварительно инвертируется содержимое аккумулятора.

Команды JC и JNC совместно с командой сложения ADD позволяют реализовать переходы по условиям "больше/меньше" некоторой пороговой величины. Например, для перехода по условию  $A\!>\!05$  используются команды:

ADD A, #0FBh ; сложить аккумулятор с числом -6;

JC M0 ; если до сложения A > 05, то перейти на M1.

Но следует учитывать, что при этом изменяется содержимое аккумулятора.

Команда безусловного перехода с косвенной адресацией JMPP @A позволяет реализовать *множественные ветвления*, аналогично операторам SWITCH или CASE языков высокого уровня. При этом в памяти программ

располагается таблица команд JMP, а в аккумулятор помещается номер ячейки таблицы, содержащей команду JMP с требуемым адресом перехода. Эта таблица должна располагаться в той же странице памяти программ, что и команда JMPP, а ячейки таблицы нумеруются числами 0, 2, 4, ....

Для организации *циклов* удобно использовать команду DJNZ, сочетающую в себе декремент и переход по ненулевому результату. При этом счётчик циклов организуется в одном из регистров:

|            | MOV R4, #0Ah | ; инициализация счётчика цикла         |       |

|------------|--------------|----------------------------------------|-------|

| M0:        |              |                                        |       |

| $\uparrow$ |              | ; тело цикла                           |       |

|            |              |                                        |       |

|            | DJNZ R4. M0  | : лекремент R4 и повторение пикла. есл | и R4≠ |

Следует отметить, что тело цикла от метки M0 до команды DJNZ включительно должны находиться в пределах одной страницы памяти программ.

Сложные алгоритмы управления можно реализовать, применяя структурный стиль программирования, при котором задача разбивается на мелкие подзадачи, каждая из которых решается своей процедурой или функцией. Для этого используются следующие команды:

- CALL вызов подпрограммы (с 11-разрядным адресом);

- RET возврат из подпрограммы (без восстановления PSW);

- RETR возврат из прерывания (с восстановлением PSW).

При вызове подпрограммы выполняются следующие действия:

- содержимое счётчика команд (адрес возврата, 12 разрядов) и старшей тетрады слова состояния (флаги, 4 разряда) сохраняются в стеке;

- в счётчик команд записывается 12-разрядный адрес подпрограммы, старший бит которого копируется из флага DBF, а остальные 11 разрядов являются аргументом команды CALL.

Глубина вложений подпрограмм ограничена ёмкостью стека (16 байт) и не должна превышать восьми. Подпрограмма должна заканчиваться командой RET, по которой:

- восстанавливается из стека содержимое счётчика команд (адрес возврата);

- продолжается выполнение основной программы.

Заметим, что подпрограмма может заканчиваться командой возврата из прерывания RETR, которая кроме адреса возврата восстанавливает PSW.

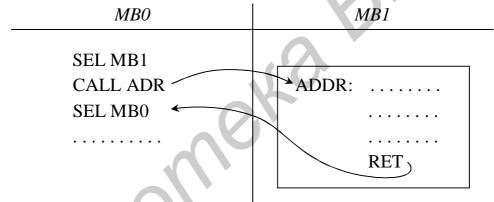

Подобно команде JMP, команда CALL позволяет обратиться в любое место текущего банка памяти программ. Кроме того, используя команды SEL MB0 и SEL MB1, можно вызвать подпрограммы из альтернативного (по отношению к текущему) банка. В этом случае перед вызовом подпрограммы необходимо

выбрать соответствующий банк памяти, а перед возвратом – восстановить старое значение DBF командой SEL:

Если в подпрограмме не восстановить значение номера банка во флаге DBF командой SEL MB0, то возврат все же будет выполнен правильно, в банк MB0 (так как в стеке сохранен полный 12-разрядный адрес возврата). Однако первая же команда JMP или CALL переключит банк на MB1.

Если к подпрограмме обращаться из разных банков памяти, то необходимо восстанавливать DBF в основной программе вслед за командой вызова:

Следует также учитывать, что подпрограммы обработки прерывания должны располагаться только в нулевом банке памяти МВО.

### 3.15. Команды управления режимами работы микроконтроллера

В эту группу входят команды управления таймером/счётчиком, прерываниями и флагами переключения банков регистров и банков памяти программ:

- STRT CNT запуск счётчика;

- STRT T запуск таймера;

- STOP TCNT останов таймера/счётчика;

- EN I, DIS I разрешение/запрещение внешних прерываний;

- EN TCNTI, DIS TCNTI разрешение/запрещение прерывания от таймера/счётчика;

- SEL RB0, SEL RB1 выбор текущего банка регистров;

- SEL MB0, SEL MB1 выбор текущего банка памяти программ;

- ENT0 CLC разрешение выдачи синхросигнала на выход Т0.

Последняя из этих команд ENT0 используется для выдачи на вывод T0 синхроимпульсов с частотой  $f_0/3$ , где  $f_0$  — частота кварцевого резонатора. Этот сигнал используется для синхронизации внешних устройств. Он может быть отключен только сбросом микроконтроллера.

Наличие команд переключения банков регистров позволяет при вызове подпрограмм и обработке прерываний эффективно использовать второй банк регистров в качестве рабочего, сохраняя параметры вычислительного процесса не в стеке, а в исходном банке регистров. При этом возврат к исходному банку регистров будет выполнен автоматически, если подпрограмма обработки прерывания оканчивается командой возврата RETR (с восстановлением PSW).

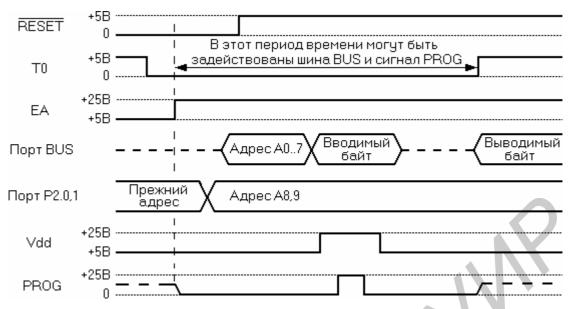

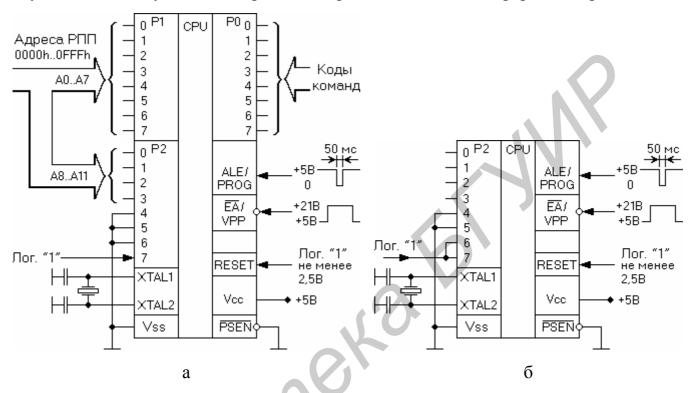

#### 3.16. Загрузка прикладных программ в резидентную память

Процесс прикладных программ в резидентную загрузки память микроконтроллера (часто называемый программированием), требует использования специального устройства – программатора, обеспечивающего формирование требуемых сигналов напряжением +5 и +25 В, подаваемых на выводы микроконтроллера (рис. 14). При загрузке программ в РПП участвует большая группа выводов микроконтроллера, сигналы на которых должны формироваться в строго определенной последовательности. Эта временная последовательность приводится на рис. 15.

Рис. 14. Схема загрузки РПП с контролем вводимой информации

Рис. 15. Временная диаграмма режима загрузки РПП

Верификация прикладной программы, содержащейся в резидентной памяти МК, может быть выполнена путем прочтения её содержимого в режиме внешнего доступа. В процессе загрузки программы выполняется следующая последовательность действий:

- 1) программатор устанавливается в начальное состояние ( $U_{dd}$  = +5 B, X1 синхросигнал с частотой 1..6 МГц, RESET = 0; T0 = +5 B, EA = +5 B);

- 2) микроконтроллер устанавливается в панельку программатора;

- 3) инициализируется режим загрузки (T0 = 0, EA = +25 B; PROG = 0);

- 4) выдаётся 10-разрядный адрес (8 разрядов на шину BUS и 2 разряда на линии P2.0, P2.1);

- 5) на вход RESET подаётся +5 В (защелка адреса);

- б) выдаётся загружаемый байт (на шину BUS);

- 7) подаётся напряжение программирования ( $U_{dd}$ = + 25 B);

- 8) подаётся программирующий импульс (PROG = 25 В длительностью 50 мс);

- 7) снимается напряжение программирования ( $U_{dd}$ = + 5 B);

- 10) инициализируется режим проверки (Т0 = + 5 В);

- 11) читается записанный байт (с шины BUS) и сравнивается с заданным;

- 12) производится переход к загрузке следующего байта (T0=0, RESET=0) и процедура повторяется с п.4;

- 13) программатор возвращается в начальное состояние (T0 = +5 B);

- 14) микроконтроллер извлекается из панельки программатора.

При выборе программатора следует учитывать, что существуют как универсальные, так и специализированные устройства. Программатор может подключаться к компьютеру через стандартный порт ввода/вывода (параллельный либо последовательный), а также через специальный адаптер компьютера.

# 4. Семейство микроконтроллеров MCS-51

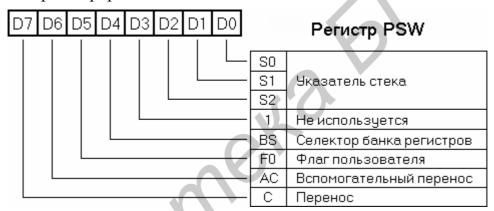

#### 4.1. Архитектура микроконтроллеров MCS-51

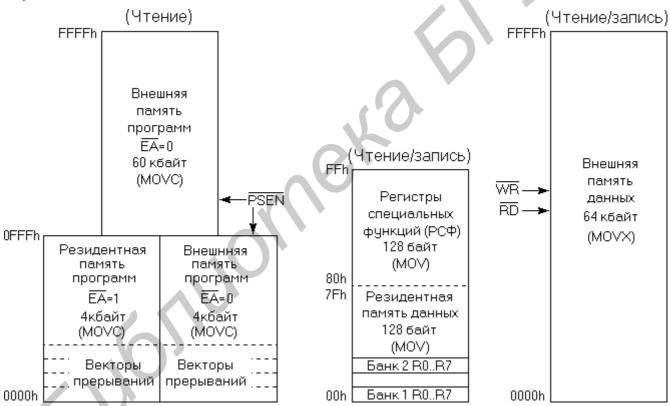

микроконтроллеров MCS-51 Семейство основано на 8-разрядном процессорном ядре. В его состав входит целый ряд микросхем, отличающихся производительностью. объёмом встроенной памяти, количеством ввода/вывода, характеристиками таймеров и интерфейсных модулей. микроконтроллеры этого семейства работают с одной и той же системой команд, большинство из них выполняется в одинаковых корпусах с совпадающей цоколевкой. Это позволяет использовать для разработанного устройства микросхемы разных производителей без изменения принципиальной схемы и программы.

Первым представителем этого семейства является микросхема 8051 фирмы Intel, выпущенная в 1980 году на базе n-MOS технологии. В более поздних модификациях 80С51 использовалась технология CMOS, отличающаяся пониженным энергопотреблением. Отечественными аналогами семейства MCS-51 являются микросхемы 1816ВЕ31/51, 1830ВЕ31/51, 1834ВЕ31 и 1850ВЕ31. Типичный микроконтроллер этого семейства имеет 1 Кбайт внутренней памяти программ и 128 байт внутренней памяти данных (16 байт из которых допускают побитовую адресацию).

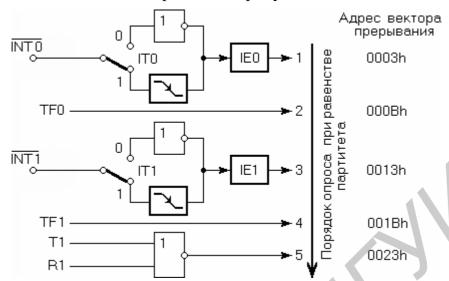

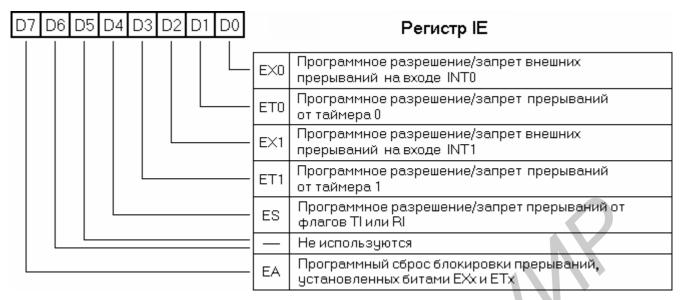

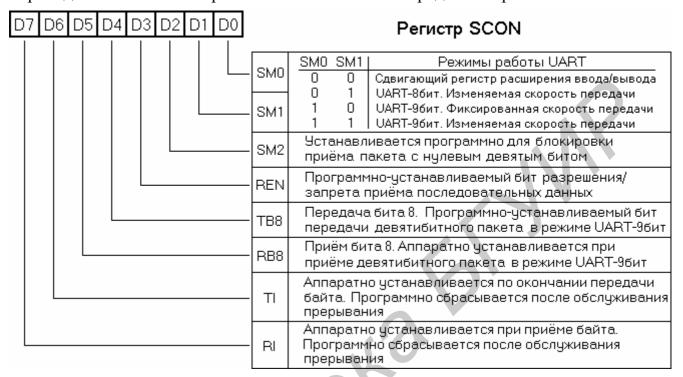

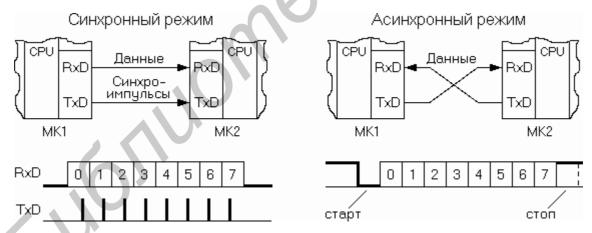

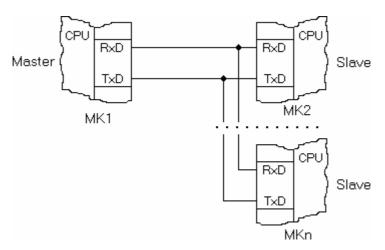

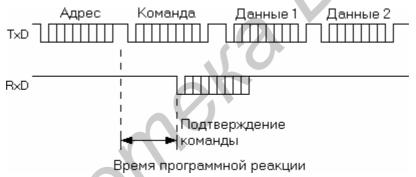

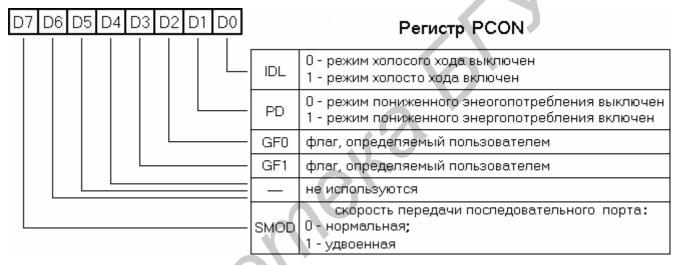

Первоначально при выполнении команд использовались простейшие методы синхронизации, при которых каждый машинный цикл состоял из 12 тактов. Поэтому при тактовой частоте 12 МГц команда выполнялась за 1..2 мкс. В дальнейшем число тактов на цикл удалось сократить до четырёх, двух, и даже одного, а тактовую частоту довести до 100 МГц.