# Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

Кафедра электронных вычислительных средств

# ПРОЕКТИРОВАНИЕ ЭВС С ДИНАМИЧЕСКИ РЕКОНФИГУРИРУЕМОЙ АРХИТЕКТУРОЙ

Лабораторный практикум для студентов специальности 1-40 02 02 «Электронные вычислительные средства» дневной формы обучения

УДК 681.3.06 (076) ББК 32.973.26-02 я7 П 79

### Рецензент канд. техн. наук В. Н. Левкович

#### Авторы:

А. А. Петровский, А. Е. Новиков, Д. А. Машеров, М. И. Вашкевич, М. З. Лившиц, Д. С. Лихачев

Проектирование ЭВС с динамически реконфигурируемой архи-П 76 тектурой : лаб. практикум для студ. спец. 1-40 02 02 «Электронные вычислительные средства» днев. формы обуч. / А. А. Петровский [и др.]. – Минск : БГУИР, 2008. – 64 с. : ил.

ISBN 978-985-488-318-2

Представлены краткие теоретические сведения о лабораторной установке на базе отладочного модуля Xilinx ML401.

Темы лабораторных работ отражают основные положения курса «Проектирование ЭВС с динамически реконфигурируемой архитектурой». Особое внимание уделяется синтезу устройств, реализующих базовые алгоритмы цифровой обработки сигналов с использованием распределенной арифметики. Лабораторный практикум содержит пять лабораторных работ, в каждой из которых приведены краткие теоретические сведения и рекомендации по выполнению.

УДК 681.3.06 (076) ББК 32.973.26-02 я7

# СОДЕРЖАНИЕ

| ВВЕДЕНИЕ                                                      | 4         |

|---------------------------------------------------------------|-----------|

| ЛАБОРАТОРНАЯ УСТАНОВКА                                        |           |

| 1. ЛАБОРАТОРНАЯ РАБОТА №1. КОНФИГУРИРОВАНИЕ ОТЛАДОЧНОЙ ПЛА    |           |

| ML401 ЧЕРЕЗ КОНТРОЛЛЕР SYSTEM ACE В СРЕДЕ XILINX ISE 8.1      |           |

| 1.1. Теоретические сведения                                   |           |

| 1.1.1. Основы работы в среде Xilinx ISE 8.1, создание проекта | 10        |

| 1.1.2. Конфигурирование отладочной платы ML401 с помощью      |           |

| карты памяти CompactFlash                                     | 25        |

| 1.2. Порядок выполнения работы                                |           |

| 1.3. Содержание отчета                                        | 32        |

| 2. ЛАБОРАТОРНАЯ РАБОТА №2. МАС-ПРОЦЕССОР                      | 33        |

| 2.1. Теоретические сведения                                   | 33        |

| 2.2. Порядок выполнения работы                                | 34        |

| 2.3. Содержание отчета                                        | 34        |

| 3. ЛАБОРАТОРНАЯ РАБОТА №3. ИССЛЕДОВАНИЕ БАЗОВЫХ АЛГОРИТМО     | B 25      |

| ЦОС НА MAC-APXИTEКТУРЕ                                        | 33<br>25  |

| 3.1. Теоретические сведения                                   | 33<br>20  |

| 3.2. Порядок выполнения расоты                                | 30<br>20  |

| 4. ЛАБОРАТОРНАЯ РАБОТА №4. ПРОЦЕССОР НА РАСПРЕДЕЛЕННОЙ        | 30        |

| АРИФМЕТИКЕ                                                    | 39        |

| 4.1. Теоретические сведения                                   | ,37<br>39 |

| 4.1.1. Прямой механизм распределенной арифметики              |           |

| 4.1.2. Уменьшение размера памяти                              |           |

| 4.1.3. Увеличение производительности распределенной арифметин |           |

| 4.2. Порядок выполнения работы                                |           |

| 4.3. Содержание отчета                                        |           |

| 5. ЛАБОРАТОРНАЯ РАБОТА №5. ИССЛЕДОВАНИЕ БАЗОВЫХ АЛГОРИТМОВ    | <br>В     |

| ЦОС НА РАСПРЕДЕЛЕННОЙ АРИФМЕТИКЕ                              |           |

| 5.1. Порядок выполнения работы                                |           |

| 5.2. Содержание отчета                                        | 48        |

| ПРИЛОЖЕНИЕ А                                                  | 49        |

| А.1. Описание отладочной платы ML401                          | 49        |

| А.1.1. Общий вид платы ML401                                  | 49        |

| А.1.2. Внешние запоминающие устройства                        | 49        |

| А.1.3. ПЛИС                                                   | 52        |

| А.1.4. Сопряжение с внешними устройствами                     | 53        |

| А.1.5. Переключатели и устройства отображения информации      |           |

| А.1.6. Синхронизация и питание                                |           |

| А.2. Конфигурирование отладочной платы ML401                  |           |

| ЛИТЕРАТУРА                                                    |           |

# **ВВЕДЕНИЕ**

*FPGA* (field programmable gate arrays), или ПЛИС, представляют собой цифровые интегральные схемы, состоящие из программируемых логических блоков и программируемых соединений между этими блоками. Возможность конфигурировать эти устройства позволяет инженерам-разработчикам решать множество различных задач.

Словосочетание «field programmable», содержащееся в расшифровке аббревиатуры FPGA, означает, что программирование FPGA-устройств выполняется на месте (в отличие от устройств, внутренняя функциональность которых жестко прописана производителем), т.е. возможность модификации функций устройства в лабораторных условиях.

ПЛИС занимают промежуточное положение между программируемыми логическими устройствами (ПЛУ) и заказными интегральными схемами. С одной стороны, их функциональность может быть задана непосредственно на месте в соответствии с требованиями заказчика-пользователя. С другой стороны, они могу содержать миллионы логических вентилей и, следовательно, реализовывать чрезвычайно большие и сложные функции, которые изначально могли быть реализованы только с помощью заказных интегральных микросхем.

Стоимость ПЛИС намного ниже стоимости заказных интегральных схем (хотя окончательная версия заказной микросхемы при массовом производстве оказывается более дешевой). В случае использования ПЛИС внесение изменений в устройство не вызывает особых затруднений и существенно сокращаются сроки выхода таких устройств. Все это делает ПЛИС привлекательными не только для крупных разработчиков, но и для небольших новаторских конструкторских бюро.

### ЛАБОРАТОРНАЯ УСТАНОВКА

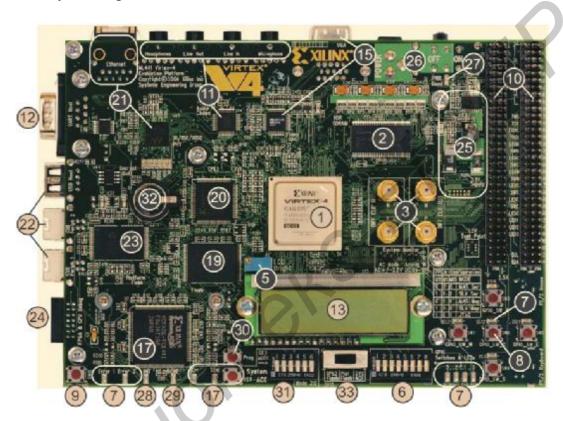

В качестве лабораторной установки используется отладочная плата Xilinx ML401 (рис В.1).

Отладочная плата характеризируется следующими параметрами:

- используемая ПЛИС Virtex-4: XC4VLX25-FF668-10;

- 64-Мб DDR SDRAM с 32-битным интерфейсом, работающим на частоте передачи данных до 266 МГц;

- одна входная дифференциальная пара синхронизации и выходная дифференциальная пара синхронизации с разъёмами SMA;

- один генератор синхроимпульсов с частотой 100 МГц (с панелью) и один дополнительный генератор синхроимпульсов на 3,3 В с открытой панелью;

- DIP-переключатели общего назначения, светодиоды и кнопки;

- разъёмы расширения с 32 несимметричными контактами вводавывода, 16 LVDS-совместимыми дифференциальными парами, 14 дополнительными контактами ввода—вывода, подключенными к кнопкам и светодиодам, разъёмом для подключения питания, средствами расширения JTAG-цепочки, а также расширителем IIC-шины;

- аудиокодек Stereo AC97 с линейным входом и выходом, 50 мВт наушниками и гнездами (моно) для микрофона;

- последовательный порт RS-232;

- ЖКИ на две строки по 16 символов в каждой;

- один 4-Кбитный IIC EEPROM;

- выход VGA: 50 МГц/24-битный видео ЦАП;

- 2 порта PS/2 для подключения мыши и клавиатуры;

- конфигурационный контроллер System ACE Compact Flash с разъёмом Туре I/II Compact Flash.

- синхронная ZBT SRAM: 9 Мбит SRAM на 32-битной шине данных с четырьмя битами четности;

- микросхемы Intel Strata Flash ёмкостью 8 Мб (или совместимые с ними);

- трёхрежимный (10/100/1000) приёмопередатчик Ethernet PHY;

- микросхема USB-интерфейса (Cypress CY7C67300) с основным (host) и периферийными портами;

- Xilinx CPLD XC95144XL, позволяющая использовать микросхемы флэш-памяти для конфигурирования FPGA Virtex-4;

- память для хранения конфигурации: Xilinx XCF32P Platform Flash;

- конфигурационный порт JTAG, позволяющий использовать кабели Parallel Cable III или Parallel Cable IV;

- встроенные источники питания для всех используемых значений напряжения;

- адаптер переменного тока напряжением 5 В и силой тока 3 А;

- светодиодный индикатор питания.

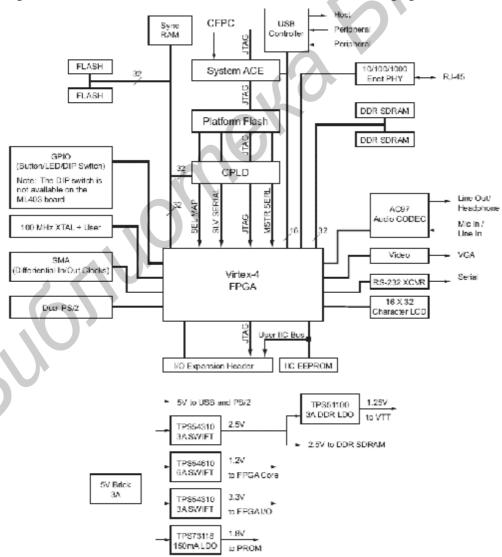

Рис. В.1. Отладочная плата Xilinx ML401 (лицевая сторона) На рис. В.2 показана блок-схема отладочной платформы ML401.

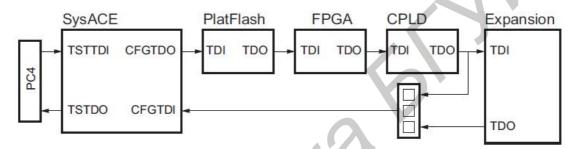

Рис. В.2. Блок-схема отладочной платформы Virtex-4 ML401

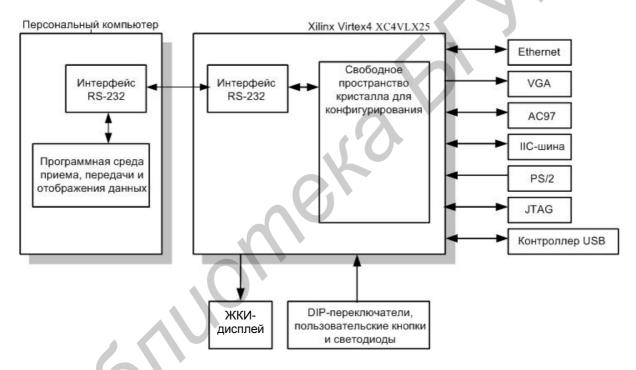

Наиболее простым способом обмена данными между персональным компьютером и отладочным модулем ML401 является использование последовательного интерфейса – COM-порта (COMmunication port). COM-порт обеспечивает асинхронный обмен по стандарту RS-232. Реализуются СОМ-порты на микросхемах универсальных асинхронных приемопередатчиков (UART – Universal Asynchronous Receiver Transmitter). UART обеспечивает полную дуплексную связь по последовательным линиям интерфейса RS-232 (рис. В.3).

Физически в контроллер интерфейса RS-232 входят две линии Rx и Tx – приемника и передатчика соответственно. В состоянии покоя на линиях выставляется уровень логической единицы. Данные передаются последовательно на заданной скорости обмена. О начале передачи сигнализирует старт-бит, во время которого линия переводится с состояние логического нуля, далее следуют 8 передаваемых бит (начиная с младшего), завершает передачу стоп-бит, гарантирующий паузу между посылками. Формат посылки приведен на рис. В.4.

Рис. В.3. Обмен данными между пользователем и отладочной платой посредством интерфейса RS-232

| старт | d0 | d1 | d2 | d3 | d4 | d5 | d6 | d7 | стоп старт |

|-------|----|----|----|----|----|----|----|----|------------|

Рис. В.4. Формат передачи в последовательном интерфейсе

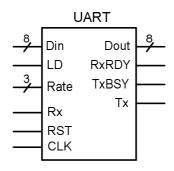

Контроллер интерфейса RS-232 позволяет производить обмен данными на заданной скорости между выполняющимся на FPGA пользовательским приложением и персональным компьютером. COM-порт имеет ряд стандартных скоростей обмена: 115 200, 57 600, 38 400, 19 200, 9 600, 4 800, 2 400, 1 200, 600, 300, 150 бит/с. Интерфейс контроллера приведен на рис. В.5.

Рис. В.5. Контроллер последовательного порта

Описание входных и выходных сигналов контроллера сведено в табл. В.1.

Таблица В.1

### Назначение сигналов контроллера UART

| Название  | Назначение сигнала                                          |

|-----------|-------------------------------------------------------------|

| Din[7:0]  | 8 бит данных для пересылки в ПК                             |

| LD        | Строб для записи данных со входа Din в контроллер. Дли-     |

|           | тельность сигнала равна одному периоду CLK                  |

| Rate[2:0] | 3 бита, управляющие скоростью обмена. Поддерживаются        |

|           | скорости обмена от 115 200 до 1 200 бит/с. Код 000 соответ- |

|           | ствует скорости 115 200, 001 – скорости 57 600 и т.д.       |

| Rx        | Вход приемника                                              |

| RST       | Асинхронный сброс, активный высокий уровень                 |

| CLK       | Тактовый сигнал (100 МГц)                                   |

| Dout      | 8 бит данных, переданных от ПК                              |

| RxRDY     | Сигнал длительностью один период CLK появляется, когда      |

|           | контроллер принял данные от ПК, находящиеся на выходе       |

|           | Dout                                                        |

| TxBSY     | Устанавливается в «1» на весь цикл передачи данных, если в  |

|           | это время приходит сигнал LD, то он будет проигнорирован    |

| Tx        | Выход передатчика                                           |

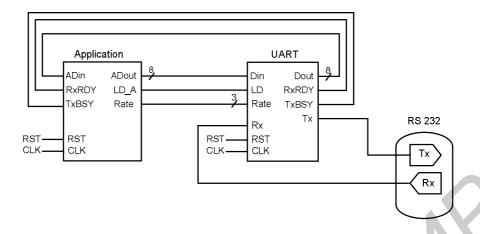

Типичная схема использования контроллера UART для связи отладочного модуля ML401 с ПК показана на рис. В.б.

Из рис. В.6 видно, что для передачи данных от приложения к ПК через контроллер UART необходимо выставить данные на выход ADout и стробировать их сигналом LD\_A. Полученные от ПК данные приходят на вход ADin и стробируются сигналом RxRDY.

Рис. В.б. Схема подключения контроллера UART

Для использования контроллера необходимо подключить VHDL-файлы с описанием контроллера к проекту. Затем в головном файле прописать контроллер как компонент схемы, как показано ниже:

```

component UART

Port ( Din : in STD_LOGIC_VECTOR (7 downto 0);

Rx : in STD_LOGIC;

LD : in STD_LOGIC;

Rate: in STD_LOGIC_VECTOR (2 downto 0);

clk : in STD_LOGIC;

rst : in STD_LOGIC;

Dout: out STD_LOGIC;

Dout: out STD_LOGIC_VECTOR (7 downto 0);

RxRDY: out STD_LOGIC;

TxBSY: out STD_LOGIC;

Tx : out STD_LOGIC;

end component;

```

Затем при помощи оператора *port map* назначить входам и выходам контроллера нужные сигналы. Далее при помощи утилиты *Assign Package Pins* назначить входу приемника Rx и выходу передатчика Tx выводы микросхемы FPGA - W2 и W1 соответственно.

Для приема и отправки данных по интерфейсу RS-232 со стороны ПК можно использовать программу HyperTerminal, входящую в состав Microsoft Windows. Также для этих целей подходит специально разработанная программа RS-232 tool, основные возможности которой включают прием и отправку данных через выбранный СОМ-порт (номера от 1 до 32), выбор скорости обмена, сохранение принятых данных в файл.

# 1. ЛАБОРАТОРНАЯ РАБОТА №1 КОНФИГУРИРОВАНИЕ ОТЛАДОЧНОЙ ПЛАТЫ ML401 ЧЕРЕЗ КОНТРОЛЛЕР SYSTEM ACE B CPEДE XILINX ISE 8.1

*Цель работы:* изучить основные этапы конфигурирования отладочной платы ML401 через контроллер System ACE в среде Xilinx ISE 8.1.

### 1.1. Теоретические сведения

### 1.1.1. Основы работы в среде Xilinx ISE 8.1, создание проекта

Integrated Software Environment (ISE) – основная САПР ПЛИС фирмы Xilinx, обеспечивающая весь процесс проектирования цифровых устройств на базе ПЛИС от ввода исходного описания до программирования микросхем.

Версия 8.1 ISE поддерживает следующие семейства ПЛИС:

- Virtex/Virtex-E/Virtex-ll/Virtex-ll Pro/Virtex-4;

- Spartan-1 I/Spartan-11E/Spartan-3/Spartan-3E;

- XC9500/XC9500XL/XC9500XV;

- CoolRunner/CoolRunner-ll.

САПР ISE работает под управлением ОС Windows 2000 + SP2 или Windows XP. Кроме того, возможна работа под управлением Solaris 2.8 и Linux (Red Hat Enterprise 3).

Все конфигурации ISE имеют интерфейсы к САПР Synplify и Leonardo Spectrum.

Пакет ISE WebPack представляет собой бесплатную версию САПР, доступную для загрузки с сайта Xilinx (<u>www.xilinx.com</u>). Он имеет ограничение по максимально поддерживаемому объему ПЛИС, но, начиная с версии 8.1, функциональные возможности WebPack полностью соответствуют ISE Foundation.

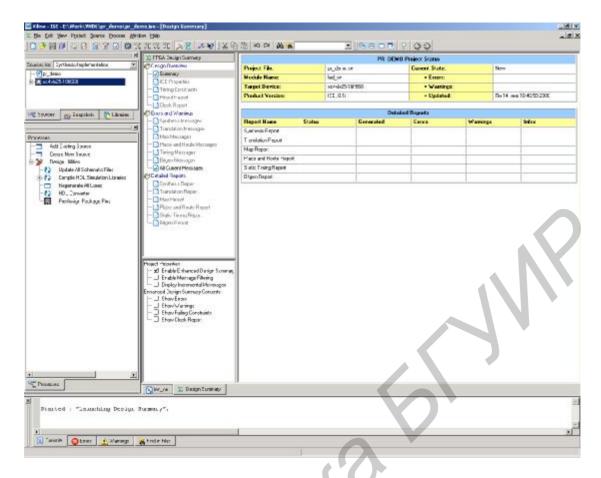

Внешний вид главного окна оболочки проектирования показан на рис. 1.1.

Главное окно ISE называется «Навигатор проектов» (*Project Navigator*). В этом окне расположены инструментальные панели и консоль сообщений. В отличие от предыдущих версий отчет о состоянии проекта, занятых ресурсах ПЛИС и результатах выполнения основных шагов трансляции хорошо структурирован и разбит на группы.

Панели, расположенные слева, представляют собой соответственно список файлов текущего проекта и список процессов (операций), доступных для текущего выбранного файла.

Рис. 1.1. Главное окно САПР ІСЕ

Для создания нового проекта необходимо выбрать соответствующий пункт главного меню ( $File \longrightarrow New\ Project$ ). После этого открывается мастер создания нового проекта, как показано на рис. 1.2–1.3.

| Project Name:                      | Project <u>L</u> ocation |      |

|------------------------------------|--------------------------|------|

| pr_demo                            | E:\Work\VHDL\pr_demo     |      |

| Select the Type of Top-Level Sourc | e for the Project        |      |

| <u>I</u> op-Level Source Type:     |                          |      |

| HDL                                |                          |      |

| •                                  |                          | - 10 |

|                                    |                          |      |

|                                    |                          |      |

|                                    |                          |      |

|                                    |                          |      |

|                                    |                          |      |

|                                    |                          |      |

|                                    |                          |      |

Рис. 1.2. Диалоговое окно создания нового проекта

| Property Name                  | Value                        |

|--------------------------------|------------------------------|

| Product Category               | All 💌                        |

| Family                         | Virtex4                      |

| Device                         | XC4VLX25                     |

| Package                        | FF668                        |

| Speed                          | -10                          |

| Top-Level Source Type          | HDL                          |

| Synthesis Tool                 | XST (VHDL/Verilog)           |

| Simulator                      | ISE Simulator (VHDL/Verilog) |

| Enable Enhanced Design Summary | V                            |

| Enable Message Filtering       |                              |

| Display Incremental Messages   |                              |

|                                |                              |

Рис. 1.3. Диалоговое окно выбора ПЛИС и маршрута проектирования

В первом окне открывшегося мастера необходимо задать имя проекта и размещение папки с материалами. Настоятельно рекомендуется выбрать для хранения проектов отдельную папку, не располагающуюся внутри папки, в которую был установлен пакет. В показанном на рис. 1.2 примере проекты размещены в  $E:\Work\VHDL$ .

Кроме этого, в предстваленном окне необходимо задать параметр *Top-Level Source Type*, т.е. тип представления модуля верхнего уровня. При этом типу HDL соответствует описание на одном из языков описания аппаратуры, Schematic задает графическое описание, а форматы EDIF и NGC/NGO предусматривают использование результатов работы внешних средств синтеза.

Описание на HDL существенно эффективнее графического ввода, поэтому выберем его.

В следующем окне мастера (рис. 1.4) можно создать новый модуль с последующим его добавлением в проект при помощи кнопки *New Source*. После создания проекта аналогичным способом можно будет создать модуль при помощи команды *Project->New Source*.

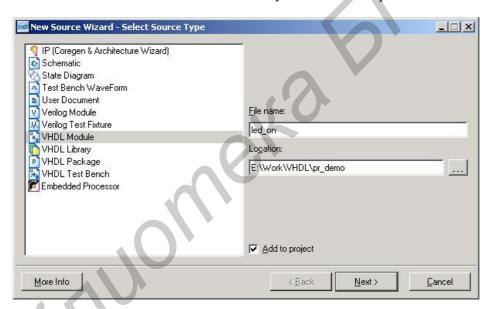

После нажатия на кнопку *New Source* будет вызвано диалоговое окно создания новых модулей (рис 1.5).

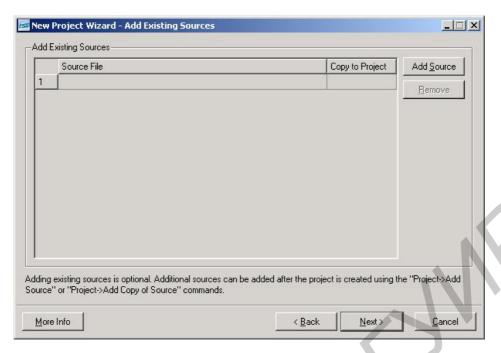

Следующее диалоговое окно (рис. 1.6) позволяет добавить к проекту уже существующие модули. Это действие можно выполнить и позже: *Project->Add Source* или *Project->Add Copy of Source*. Удобно также то, что в окне процессов размещены два пункта для быстрого добавления новых модулей или подключения к проекту существующих.

|                |                                                                  | 7970                                                                                                                                                  | New Source                                                  |

|----------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|                | Source File                                                      | Туре                                                                                                                                                  |                                                             |

| 1              |                                                                  |                                                                                                                                                       | <u>R</u> emove                                              |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

|                |                                                                  |                                                                                                                                                       |                                                             |

| eating (       | a new source to add to the pro                                   | oject is optional. Only one new source can be cr                                                                                                      | eated with the New Project Wiz                              |

| eating (       | a new source to add to the pro<br>ditional sources can be create | oject is optional. Only one new source can be cr<br>ed and added to the project by using the "Projec                                                  | eated with the New Project Wiz<br>ct->New Source'' command. |

| eating (<br>Ac | lditional sources can be create                                  | oject is optional. Only one new source can be cr<br>ed and added to the project by using the "Projec<br>isting sources can be added on the next page. | eated with the New Project Wiz<br>st->New Source'' command. |

Рис. 1.4. Создание нового модуля описания проекта

Рис. 1.5. Диалоговое окно создания новых модулей

После завершения работы мастера и создания шаблона в основном окне ISE будет показано содержимое только что созданного компонента (рис. 1.7).

Создадим простейший проект, по которому на отладочной платформе ML401 будет загораться светодиод *Центр*. Светодиод будет загораться при подаче на него '1', т.е. в текстовом редакторе необходимо следующее:

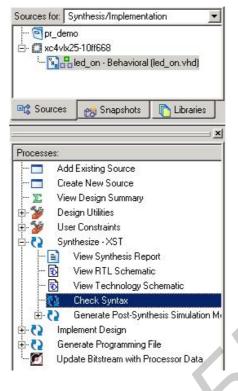

$$c < ='1';$$

Представленный текст вводится после ключевого слова begin в разделе architecture. После набора текста необходимо проверить описание компонента на наличие ошибок. Для этого компонент должен быть выбран в списке файлов проекта. После выбора в окне доступных процессов появится список операций, возможных для выбранного файла (рис. 1.8). После чего следует выполнить операцию Synthesize - XST -> Check Syntax.

Рис. 1.6. Добавление к проекту существующих модулей

```

Compage:

-- Ingineer:

-- Oreate Date:

10:04:31 [17/16/2000]

Hexign Mane:

Worlde Mane:

Test on Following at

010

Target Dovises:

- Tool versions:

11

-- Description:

10

10

17

15

Revision:

16

Revision C.Cl File Orgated

17

10

-- Additional Comments:

19

30

Tibesey TREF;

are 1993.8TE LOCID_TIST.AE(;

are 1993.STE LOCID_STER.AE(;

are 1993.STE LOCID_STER.AE(;

22

23

24

25

26

27

28

---- Incomment the following library declaration if instantiating

---- any Second primisives in this code,

--Tibers (TYTETY)

use TNTSTK.VS) moreovers...(1)

entity led on is

i : cut | 515 L5911[7

end led on:

andrived are Felavional of Leignoria

Ecqin

57

сюда пользователь дораклітат отмознив

19

end Jenaviocal:

```

Рис. 1.7. Вид текстового редактора после завершения работы мастера

Далее требуется ассоциировать выводы разрабатываемого модуля и выводов ПЛИС (рис. 1.9). Для этого следует запустить утилиту РАСЕ (выполнив следующие действия *User Constraints->Assign Package Pins*).

Перед открытием этого приложения *Навигатор проектов* предварительно создаст список выводов проекта и их типов. Для этого выполняются несколько шагов трансляции проекта.

Рис. 1.8. Проверка модуля на ошибки

Рис. 1.9. Окно редактора выводов

В основной части окна этого приложения показано схематическое изображение кристалла ПЛИС с отмеченными выводами. В левой части расположены собственно панели редактирования номеров выводов (рис. 1.10). Рассмотрим эту часть более подробно.

Рис. 1.10. Назначение выводов ПЛИС

В графе *Loc* (расположение) необходимо ввести номер вывода ПЛИС, к которому нужно подключить соответствующий сигнал. В соседней колонке размещается название банка ввода—вывода, к которому относится данное имя. Это сделано для того, чтобы избежать ситуации, когда в одном банке оказываются линии, требующие разного напряжения питания. Значения номеров контактов также можно взять из документации к плате, которая доступна на сайте *xilinx.com*.

Колонка I/O Std позволяет установить для вывода один из электрических интерфейсов, которые реализуются аппаратно путем активизации соответствующих буферов ввода—вывода. В соседних колонках можно задать опорное напряжение (требуется не для всех типов интерфейса), напряжение питания линий ввода—вывода Vcco, максимальный выходной ток, тип внутренней подтяжки, скорость нарастания и задержку.

После выполнения функционального модулирования можно приступать непосредственно к трансляции проекта. Для трансляции необходимо указать файл *led\_on.vhd* (попытка трансляции проекта без выбора главного файла не является ошибкой, но приведет к трансляции одного из библиотечных компонентов пользователя), после чего становится доступным список процессов для этого файла (рис. 1.11).

Трансляция проекта включает три основных этапа: Synthesize, Implement Design и Generate Programming File. На рис. 1.11 эти процессы показаны в «развернутом» виде. Пиктограммы около имен отдельных компонентов соответствуют типу приложений, которые будут запущены при их активизации. Значком документа показаны файлы отчета, которые при активизации будут выведены в основное окно. Однако для составления этих отчетов может потребоваться запуск каких-либо этапов синтеза или трассировки. Двойными стрелками отмечены процессы, исполняемые в основном окне ISE. Прочие пункты соответствуют внешним утилитам, открывающимся в своем окне, и значки представляют собой пиктограммы соответствующих приложений.

Для трансляции всего проекта достаточно запустить процесс *Generate Programming File*. Недостающие для его выполнения процессы будут запущены автоматически.

Ход трансляции будет показан в консоли, при появлении ошибки трансляция прекращается. При этом зеленые «галочки» напротив каждого процесса показывают его успешное завершение, желтые восклицательные знаки говорят о том, что один из вложенных процессов не был запущен (это является нормальной ситуацией), критические ошибки показываются красными крестиками. Знаки вопроса сигнализируют, что результаты выполнения этого процесса устарели и требуется его повторный запуск.

Рис. 1.11. Процессы, доступные для проекта

Настройки параметров трансляции производятся из контекстного меню для каждого процесса. Интерес представляют настройки процессов Synthesize, Implementaion и Generate Programming File. Общее количество настроек довольно велико, к тому же точный состав меняется от версии к версии САПР и от одной серии ПЛИС к другой. Поэтому здесь будут перечислены только некоторые особенности настройки параметров трансляции и синтеза, которые оказывают существенное влияние на процесс проектирования.

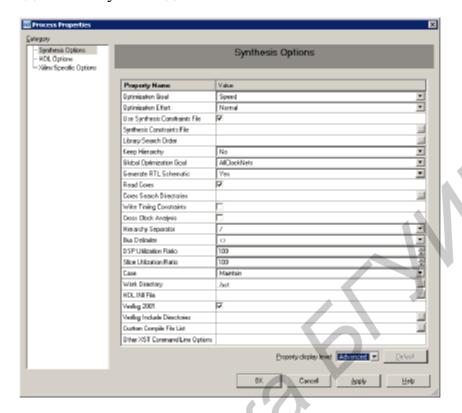

Рассмотрим настройку свойств синтеза проекта. Все окна настройки свойств процесса (рис. 1.12) имеют два уровня отображения: *Standard* и *Advanced*. На уровне *Standard* показаны наиболее часто используемые свойства, но ряд довольно важных настроек становится доступным только в режиме *Ad*-

vanced. Поэтому комментарии к настройкам будут сделаны именно для данного режима, но не для всех пунктов диалоговых окон.

Рис. 1.12. Диалоговое окно настройки свойств трансляции

Итак, в представленном на рис. 1.12 окне нас интересуют следующие пункты.

Optimization Goal имеет два варианта: Speed и Area. Эти варианты соответствуют общей направленности алгоритмов на оптимизацию с целью достижения максимальной производительности или минимальной занимаемой площади на кристалле.

*Optimization Effort* регулирует «интенсивность» алгоритмов оптимизации (effort дословно означает «усилие»). Значение normal соответствует меньшему времени работы, значение high — более высокому качеству получаемых результатов.

Напротив параметра *Use Synthesis Constraints File* необходимо оставить флажок, поскольку только в этом случае ограничения по взаимному размещению компонентов на кристалле и подключения к выводам ПЛИС будут использоваться ISE.

Параметр *Keep Hierarchy* (варианты *Yes/No/Soft*) регулирует уровень соответствия структуры ПЛИС тому описанию, которое было введено пользователем. После эквивалентных преобразований логических выражений, упрощений и оптимизации получаемая структура логических блоков может существенно отличаться от той схемы, которая была введена разработчиком. Разумеется, функционирование при этом полностью соответствует описанию проекта. Если параметр имеет значение *No*, САПР имеет возможность провести глубо-

кую оптимизацию проекта, не сохраняя в точности ту иерархию цифровых блоков, которая задается в описании.

Параметр Global Optimization Goal имеет множество вариантов:

- AIICIockNets проект оптимизируется таким образом, чтобы обеспечить максимальную частоту тактовых сетей. Вариант может использоваться в случаях, когда обработка сигнала сосредоточена в ПЛИС и выполняется большим количеством цифровых блоков, тактируемых внешним сигналом высокой частоты;

- InPad to OutPad минимизируется время распространения сигналов от входных линий микросхемы к выходным. Вариант удобен в случаях, когда ПЛИС выступает в качестве контролера в системе, включающей несколько микросхем;

- Offset In Before минимизируется время установления сигнала на входах цифровых блоков относительно последующего фронта тактового сигнала;

- Offset Out After минимизируется время установления сигнала на выходах цифровых блоков относительно предыдущего фронта тактового сигнала;

- Maximum Delay минимизируется максимальная задержка распространения. Может быть использован в проектах с большим удельным весом комбинаторной логики и сложной трассировкой.

В ряде случаев изменение параметра *Global Optimization Goal* может существенно улучшить временные характеристики проекта, поэтому рекомендуется использовать данную возможность в случаях, когда не удается удовлетворить требованиям по производительности.

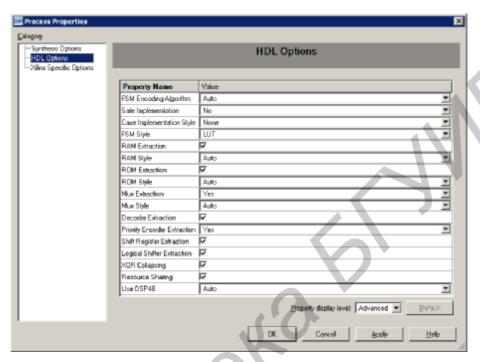

На рис. 1.13 показан вид диалогового окна настройки свойств синтеза HDL. В данном окне рекомендуется оставлять показанные настройки, за исключением случаев, когда требуется воспользоваться определенными типом физических ресурсов ПЛИС для реализации той или иной функции. Например, умножение может быть реализовано как с помощью аппаратных умножителей (если они присутствуют в данной ПЛИС), так и на базе логических ячеек, что может быть явно указано в настройках. Аналогично ПЛИС Xilinx допускают использование как блочной, так и распределенной памяти. Особенно много вариантов существует для выбора способа кодирования состояний конечных автоматов. В автоматическом режиме для каждого их этих случаев выбирается вариант, соответствующий оптимальному использованию ресурсов ПЛИС (для памяти — в зависимости от объема требуемого блока, для конечных автоматов — в зависимости от числа состояний).

На рис. 1.14 показана последняя вкладка: Xilinx Specific Options. На ней представляют интерес следующие параметры.

*Мах Fanout* — задает максимальный «коэффициент разветвления» для сигналов. Если один выход внутреннего блока должен быть подключен к множеству входов, трассировка программируемых соединений может существенно усложниться. Речь в данном случае не идет о превышении максимальной нагрузочной способности по протекающему току, поскольку внутри ПЛИС существуют многочисленные устройства буферизации. Дело в том, что при необхо-

димости распространения важного для проекта сигнала по множеству ячеек может оказаться полезным создать его копию, с тем чтобы каждый из блоков, распространяющих свою копию сигнала, делал это для ограниченной площади кристалла ПЛИС. Таким способом можно добиться уменьшенной задержки распространения за счет использования небольшого количества дополнительных ресурсов.

Рис. 1.13. Диалоговое окно настройки свойств синтеза HDL

Той же цели способствует параметр *Register Duplication*. При разрешении дублирования регистров САПР будет создавать их копии для тех областей ПЛИС, которые находятся на большом расстоянии от тех ячеек, которые формируют важный для проекта сигнал.

Следует убедиться, что установлены флажки *Add I/O Buffers* (автоматически размещает соответствующие буферы ввода-вывода) и *Pack I/O Registers into IOBs* (позволяет использовать регистры, имеющиеся в блоках ввода-вывода, что положительно влияет как на производительность проекта, так и на объем ресурсов).

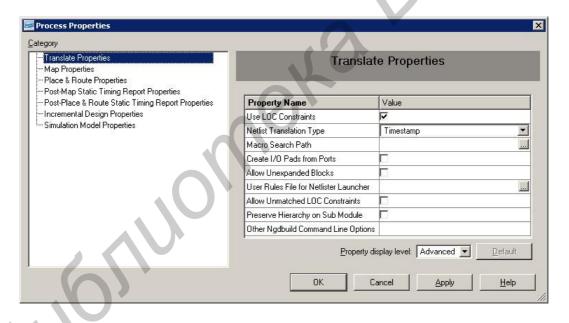

Далее рассмотрим свойства процесса Implement Design (рис. 1.15). Доступ к диалоговому окну настройки этих свойств осуществляется также по контекстному меню, вызываемому правой кнопкой мыши.

В данном окне необходимо обратить внимание на флажок *Use LOC Constraints*, который подтверждает необходимость следовать ограничениям, наложенным разработчиком на размещение компонентов проекта. Также важным может оказаться сохранение иерархии субмодулей (*Preserve Hierarchy on Sub Module*), если данные модули были разработаны ранее и относительное размещение компонентов для них уже оптимизировано. В подобных случаях повторная трансляция для проекта «в целом» может ухудшить производительность.

|                                  | Xilinx Specific Options                                         |

|----------------------------------|-----------------------------------------------------------------|

| Property Name                    | Value :                                                         |

| Add I/O Buffers                  | □ □                                                             |

| Max Fanout                       | 500                                                             |

| Number of Global Clock Buffers   | 32                                                              |

| Number of Regional Clock Buffers | 24                                                              |

| Register Duplication             | C                                                               |

| Equivalent Register Removal      | □ □                                                             |

| Register Balancing               | No                                                              |

| Move First Flip-Flop Stage       | ₽ P                                                             |

| Move Last Flip-Flop Stage        | <b>▽</b>                                                        |

| Pack I/O Registers into IOBs     | Auto                                                            |

| Slice Packing                    | □                                                               |

| Use Clock Enable                 | Auto                                                            |

| Use Synchronous Set              | Auto                                                            |

| Use Synchronous Reset            | Auto                                                            |

| Optimize Instantiated Primitives |                                                                 |

|                                  | Property display level: Advanced ▼ Defaul  OK Cancel Apply Help |

Рис. 1.14. Диалоговое окно настройки специальных параметров

Рис. 1.15. Диалоговое окно настройки параметров трансляции

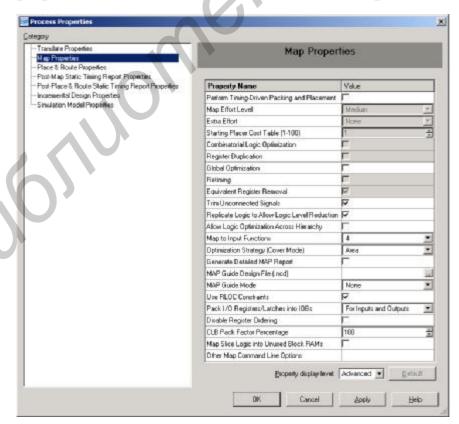

На вкладке *Map Properties* (рис. 1.16) устанавливаются свойства процесса отображения описания проекта на ресурсы ПЛИС. Свойство *Trim Unconnected Signals* позволяет исключить из проекта неиспользуемые цепи. Установленный флажок напротив *Replicate Logic To Allow Logic Level Reduction* в ряде случаев позволяет достаточно эффективно управлять процессом синтеза. Смысл этого флажка – разрешить средствам САПР «копировать» фрагменты логических блоков с целью уменьшения количества последовательно соеди-

ненных логических ячеек. Это приводит к некоторому повышению быстродействия за счет использования дополнительных ресурсов.

Установленное свойство Allow Logic Optimization Across Hierarchy разрешает, как это видно из названия, оптимизировать логические функции, скомбинированные из выражений, содержащихся в разных модулях проекта. Установка этого флажка может как улучшить, так и ухудшить общую производительность, поскольку в ряде случаев используется раздельная оптимизация субмодулей с последующим их объединением в ПЛИС большого объема. При этом разрешение на «перемешивание» отдельных компонентов с последующей оптимизацией может свести на нет усилия по оптимизации отдельных компонентов проекта.

Свойство *Map To Input Functions* позволяет выбрать максимально используемое число входов логических генераторов. Это значение желательно оставить выбранным по умолчанию.

Параметр *Optimization Strategy* довольно часто подвергается изменениям. Возможные значения стратегии размещения – оптимизация по используемым ресурсам (*Area*) и оптимизация по быстродействию (*Speed*). Вариант *Balanced* представляет собой промежуточное решение.

Интересен также последний из параметров, представленных на вкладке, — *Map Slice Logic into Unused Block RAMs*. Поскольку блочная память может выполнять функции мощного логического генератора, часть многовходовых логических функций может быть реализована с помощью этих ресурсов. Установка флажка явно разрешает подобное использование этого дефицитного ресурса.

Рис. 1.16. Диалоговое окно настройки параметров отображения

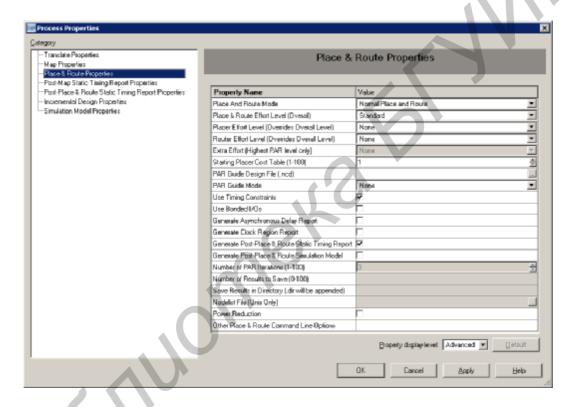

Настройки процесса *Place &, Route* (рис. 1.17) позволяют установить параметры процесса взаимного размещения ресурсов ПЛИС и трассировки связей между ними. «Строгость» проверки различных условий размещения задается свойством *Place & Route Effort Level*, имеющем две отдельные настройки для этапов *Place* (размещение) и *Route* (трассировка).

Существует режим *Guide Mode*. Понятие *guide* в данном случае означает, что трассировщик берет за основу ранее разведенный вариант создаваемого проекта. Этот режим полезен, если в проект были внесены незначительные изменения, но в целом его трассировка является вполне удачной. В таком случае включение *Guide Mode* (с указанием соответствующего файла в строке *PAR Guide Design File*) позволяет сохранить удачное размещение основной части проекта.

Рис. 1.17. Диалоговое окно настройки параметров размещения и трассировки

Следующие вкладки (рисунки для них не приведены) задают свойства генерации отчетов о моделировании временных характеристик проекта. Эти характеристики определяются отдельно после трансляции (*Post-Map*) трассировки (*Post-Place & Route*). Характеристики, определенные после трассировки, соответствуют реальному размещению проекта с учетом дополнительных задержек, появившихся из-за неудачного размещения и/или трассировки.

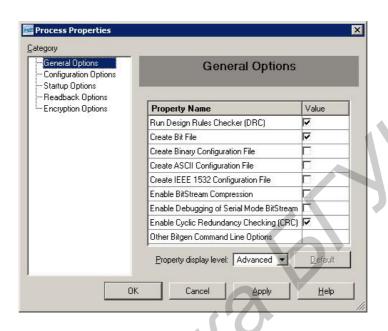

Наконец, процесс *Generate Programming File* (генерация файла программирования ПЛИС) содержит относительно небольшое количество настраиваемых параметров.

В окне на рис. 1.18 может оказаться важной установка флажков «Create Binary Configuration File» и «Create ASCII Configuration File». Все эти файлы

являются разновидностями форматов одной и той же конфигурационной последовательности. Однако конфигурация ПЛИС может быть загружена не только с помощью САПР ISE, но и процессором или микроконтроллером. Для этого может оказаться удобным двоичный формат (binary file) или даже текстовый формат, в котором загружаемые биты записаны обычными символами в кодах ASCII.

Рис. 1.18. Диалоговое окно настроек процесса формирования файла конфигурации ПЛИС

Следующая вкладка, *Configuration Options*, позволяет задать настройки процесса загрузки конфигурации ПЛИС в части установки притягивающих резисторов на выводах ПЛИС. Изменение этих настроек не представляется важным для нормальной работы.

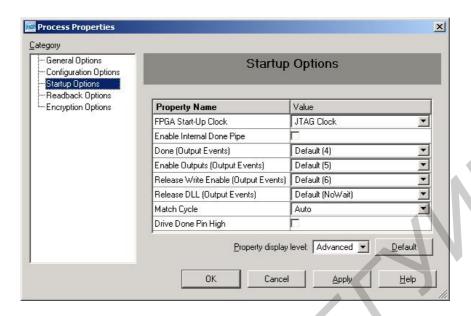

На вкладке *Startup Options* (рис. 1.19) можно задать порядок выполнения ПЛИС внутренних операций в процессе инициализации. Последние такты загрузки конфигурационной последовательности отводятся на выполнение подготовительных к нормальной работе действий. На данной вкладке можно назначить каждому из этих действий конкретный такт из завершающего цикла. На рисунке видно, что ПЛИС выполняет:

- установку вывода Done;

- разрешение выходов (перевод их из высокоимпедансного состояния в рабочее, заданное конфигурационным файлом);

- перевод внутренней схемы сброса/установки в неактивное состояние;

- разрешения записи в регистры;

- разрешение работы устройств DLL.

Установленные по умолчанию параметры полностью соответствуют нормальной работе ПЛИС. В данном проекте не используются сигналы синхронизации, поэтому следует установить значение параметра *FPGA Start-Up*

Clock в JTEG Clock. Их изменение желательно производить в случае, когда цель таких изменений и ожидаемый результат понятны разработчику.

Рис. 1.19. Диалоговое окно настроек создания файла конфигурации (порядок загрузки и инициализации)

На последней вкладке можно установить очень важный параметр *Security*, отвечающий за возможность обратного считывания конфигурации ПЛИС. Запрещение обратного считывания (*Readback*) полностью защищает проект от несанкционированного копирования.

Приведенная информация о продукте ISE не является исчерпывающей, хотя и дает примерное представление о порядке работы с этой довольно эффективной версией САПР.

# 1.1.2. Конфигурирование отладочной платы ML401 с помощью карты памяти CompactFlash

Для трансляции всего проекта запустим процесс Generate Programming File. Недостающие для его выполнения процессы будут запущены автоматически.

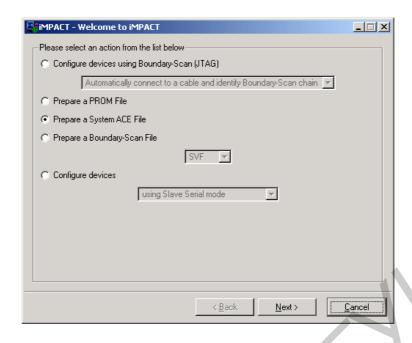

Далее следует запустить программу iMPACT для создания конфигурационных файлов. Для этого следует выполнить следующую последовательность действий *Generate Programming File-> Generate PROM, ACE, or JTEG File*. После этих действий запустится программа конфигурирования кристалла iMPACT и откроется окно мастера определения параметров конфигурирования кристалла (рис. 1.20).

Конфигурирование платы будет производиться через контроллер *System ACE*, поэтому выбираем пункт *Prepare System ACE File* и нажимаем *Next*.

Рис. 1.20. Выбор типа создаваемых конфигурационных файлов

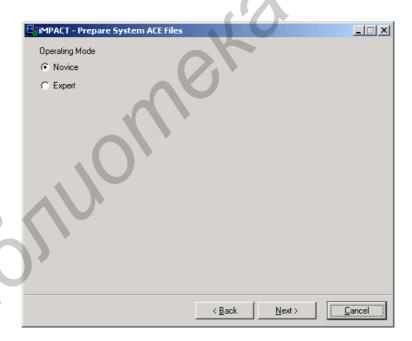

Подготовку файлов к конфигурированию будем осуществлять в режиме для «новичка» (Novice). Выберем данный пункт в диалоговом окне (рис. 1.21) и перейдем к следующему пункту.

Рис. 1.21. Выбор режима создания конфигурационных файлов

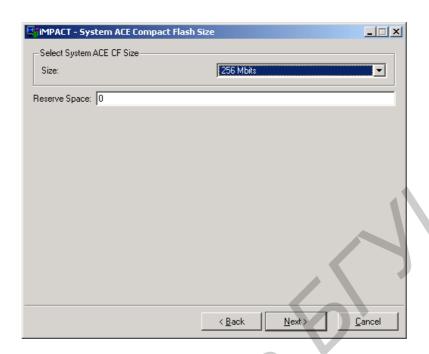

В следующем окне «помощника» требуется выбрать размер карты памяти, используемой для конфигурирования платы (рис. 1.22). В комплекте с поставляемой идет карта памяти объемом 32 Мб, что соответствует 256 Мбит. Резервирование пространства не требуется. Выберем данные параметры и перейдем дальше.

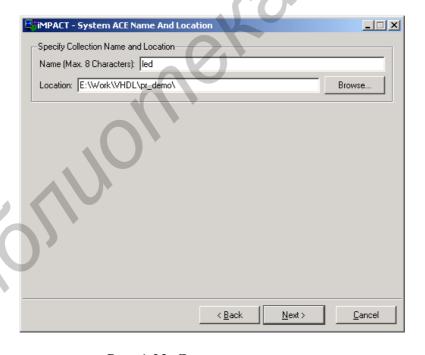

В следующем окне надо задать имя создаваемой коллекции конфигураций и выбрать её расположение на диске (рис. 1.23). Имя коллекции не может быть больше 8 символов.

Рис. 1.22. Задание размера карты памяти СF

Рис. 1.23. Создание коллекции

Следующим этапом будет задание адресов и имен для конфигураций, которые будут входить в коллекцию. Так как в коллекцию у нас будет входить только одна конфигурация, то зададим конфигурирование только нулевого адреса (рис. 1.24).

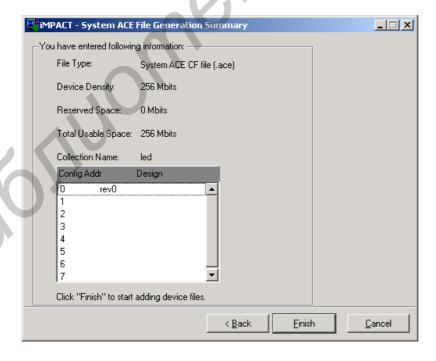

В следующем окне «помощника» отобразится суммарная информация (рис. 1.25). Если вся отображаемая информация верна, то следует нажать *Finish*.

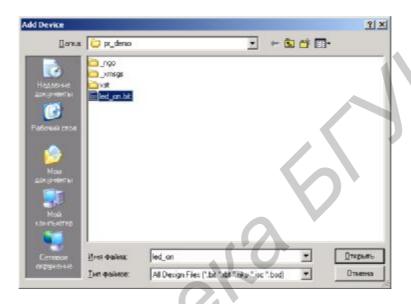

После завершения работы мастера появится сообщение о начале ассоциирования конфигурации к нулевому адресу, затем диалоговое окно выбора файлов дизайна (рис. 1.26). В данном окне надо выбрать файл led\_on.bit.

| iMPACT - Systerm ACE Co      | onfiguration Address And Design            | □× |

|------------------------------|--------------------------------------------|----|

| Assign Configuration Address | and Design Name (Max. 8 Characters):       |    |

| Configuration Address 0      | rev0                                       |    |

| Configuration Address 1      | rev1                                       |    |

| Configuration Address 2      | rev2                                       |    |

| Configuration Address 3      | rev3                                       |    |

| Configuration Address 4      | rev4                                       |    |

| Configuration Address 5      | rev5                                       |    |

| Configuration Address 6      | rev6                                       |    |

| Configuration Address 7      | rev7                                       |    |

|                              |                                            |    |

|                              |                                            |    |

|                              |                                            |    |

|                              |                                            |    |

|                              |                                            |    |

|                              | < <u>B</u> ack <u>N</u> ext > <u>C</u> anc | el |

Рис. 1.24. Задание адресов конфигураций, входящих в коллекцию

Рис. 1.25. Суммарная информация по созданной коллекции

После выбора конфигурационного файла появится сообщение с предложением перевыбрать конфигурационный файл. Если файл выбран правильно, то надо нажать на кнопку No.

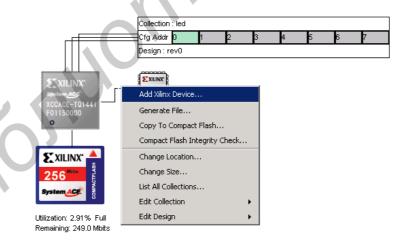

Так как в JTEG-цепочке находятся ещё устройства, то их надо добавить для правильной работы отладочной платы. Для этого надо кликнуть в свободной области слева от нашей конфигурации правой кнопкой мыши и добавить файл описания (в появившемся контекстном меню пункт  $Add\ Xilinx\ Device$ )  $xcf32p\_vo48.bsd$ , находящийся в папке <каталог  $Xilinx\ Ise>$ xcpfata (рис. 1.27–1.28).

Рис. 1.26. Выбор файлов дизайна

Рис. 1.27. Добавление файла описания

Аналогичным способом, только уже справой стороны от нашей конфигурации, добавляем файл описания  $xc95144xl_tq100.bsd$ , расположенный в папке  $<\kappa amanoz\ Xilinx\ Ise>\xspace \lambda c9500xl \lambda data$  (рис. 1.28).

Рис. 1.28. Готовый проект для конфигурирования ПЛИС

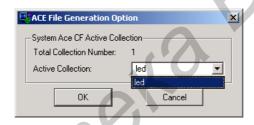

После выполнения всех рассмотренных выше действий надо сгенерировать файлы для записывания их на CompactFlash. Для этого в любом месте рабочей области надо кликнуть правой кнопкой мыши и из контекстного меню выбрать пункт  $Generate\ File$ . После чего появится диалоговое окно выбора коллекции, для которой будут генерироваться файлы. Выбираем текущую коллекцию и нажимаем OK (рис. 1.29).

Рис. 1.29. Выбор текущей коллекции

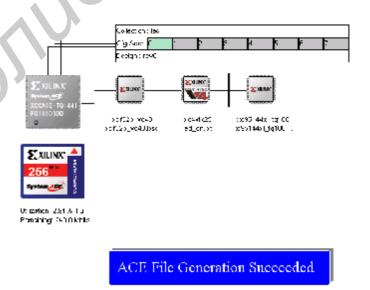

После успешной генерации файлов на экране появится сообщение *ACE File Generation Succeeded* (рис. 1.30).

Рис. 1.30. Успешное завершение создания АСЕ-файлов

Далее подключим через card reader карту памяти CompactFlash к компьютеру.

Перед записью файлов конфигураций на карту памяти CompactFlash при необходимости нужно сохранить хранящиеся на ней конфигурационные данные, а затем удалить все находящиеся на ней файлы. Это следует сделать для предотвращения скапливания на ней ненужных данных и сохранения рабочих конфигураций.

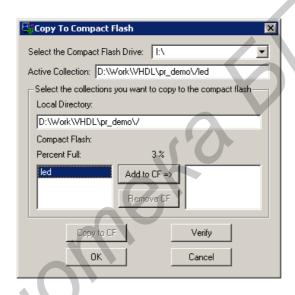

Для копирования коллекции на CompactFlash надо кликнуть правой кнопкой мыши в рабочем пространстве проекта и выбрать пункт Copy to Compact Flash. После чего появится диалоговое окно, изображенное на рис. 1.31. Выбираем коллекцию led, затем нажимаем на кнопку Add to Flash. После этого нажимаем на активированную кнопку Copy to CF, что приведет к копированию коллекции на карту памяти. После выполнения этих действий должно появиться сообщение «Copy to compact flash completed».

Рис. 1.31. Копирование проекта на СF-карту памяти

Теперь произведем подготовку платы к её программированию. Для этого требуется произвести ряд действий:

- 1) перевести переключатель включения питания на плате в положение OFF;

- 2) вставить СF-карту памяти в слот;

- 3) подключить источник питание к плате;

- 4) установить DIP-переключатели в положение 000111 (загрузка с нулевого адреса, режим конфигурирования подчиненный последовательный);

- 5) переключатель выбора источника конфигурации должен быть установлен в положение *SYS ACE*.

После выполнения рассмотренных выше действий можно переводить переключатель включения питания в положение *ON*. При правильных установках контроллер System ACE начинает программировать ПЛИС в момент вклю-

чения питания. Нажатие кнопки сброса System ACE также вызывает программирование ПЛИС от контроллера System ACE.

После программирования ПЛИС светодиод *Центр* должен загореться зеленым цветом.

Варианты заданий

Таблица 1.1

| Вариант | Задание                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------|

| 1       | Мигание светодиодов Север и Юг в противофазе                                                               |

| 2       | Поочередное мигание светодиодов Север, Юг, Запад, Восток                                                   |

| 3       | Управление загоранием светодиодов <i>Север</i> и <i>Юг</i> при помощи DIP-переключателей общего назначения |

| 4       | Мигание светодиода Центр с периодом 1 с                                                                    |

### 1.2. Порядок выполнения работы

- 1. Изучить теоретические сведения по теме лабораторной работы.

- 2. Получить у преподавателя задание для выполнения практической части работы (табл. 1.1).

- 3. На языке VHDL составить описание требуемого устройства в соответствии с вариантом.

- 4. Синтезировать устройство, проверить его работу. Оценить количество занимаемых в ПЛИС ресурсов.

- 5. Показать результат работы устройства преподавателю.

- 6. Оформить и защитить отчет по лабораторной работе.

# 1.3. Содержание отчета

- 1. Цель работы.

- 2. Краткие теоретические сведения.

- 4. Описание устройства на VHDL с комментариями.

- 5. Временные диаграммы симуляции работы устройства.

- 6. Листинг отчета синтезатора о количестве занятых ресурсов.

- 7. Выводы по работе.

# 2. ЛАБОРАТОРНАЯ РАБОТА №2 МАС-ПРОЦЕССОР

*Цель работы:* составить VHDL-описание MAC-процессора, получить временные диаграммы его работы, оценить объем занимаемых ресурсов и быстродействие.

### 2.1. Теоретические сведения

Одна из основных операций, выполняемых цифровыми процессорами обработки сигналов (ЦПОС), – цифровая фильтрация:

$$y(k) = \sum_{i=0}^{N-1} h(i) \cdot x(k-i).$$

(2.1)

Анализ данного выражения показывает, что базовой операцией цифровой фильтрации является умножение с аккумулированием результата:

$$S = S + A \cdot B \,. \tag{2.2}$$

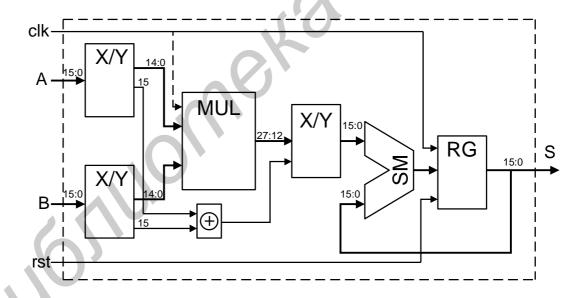

Функциональная схема одного из вариантов реализации устройства показана на рис. 2.1.

Рис. 2.1. Функциональная схема устройства умножения-накопления

На вход устройства умножения—накопления (МАС-ядра) поступают 16-разрядные числа со знаком. Знаковые разряды складываются по модулю 2, формируя знак результата. Далее результат умножения складывается с содержимым регистра-накопителя, сумма сохраняется в регистре-накопителе RG. Управляющий сигнал rst сообщает регистру RG о необходимости выдачи результата, после чего регистр обнуляется.

Основным функциональным блоком этого устройства является умножитель двоичных чисел. От вида умножителя зависят такие параметры устройства, как быстродействие, требования к площади кристалла и энергопотребление. Лабораторная работа включает реализацию устройства умножения—накопления, содержащего умножитель в соответствии с вариантом (табл. 2.1).

Таблица 2.1

### Варианты заданий

| Вариант | Умножитель                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------|

| 1       | Матричный умножитель                                                                                                     |

| 2       | Умножение, начиная с младших разрядов множителя, со сдвигом суммы частичных произведений вправо при неподвижном множимом |

| 3       | Умножение, начиная со старших разрядов множителя, со сдвигом суммы частичных произведений влево при неподвижном множимом |

| 4       | Умножитель по модифицированному алгоритму Бута (сразу на 2 разряда)                                                      |

### 2.2. Порядок выполнения работы

- 1. Изучить теоретические сведения по теме лабораторной работы.

- 2. Получить у преподавателя задание для выполнения практической части работы.

- 3. На языке VHDL составить структурное описание устройства умножения—накопления в соответствии с вариантом.

- 4. Синтезировать устройство, проверить его работу. Оценить быстродействие, количество занимаемых в ПЛИС ресурсов и энергопотребление.

- 5. Показать результат работы устройства преподавателю.

- 6. Оформить и защитить отчет по лабораторной работе.

# 2.3. Содержание отчета

- 1. Цель работы.

- 2. Краткие теоретические сведения.

- 3. Схема синтезируемого устройства.

- 4. Описание устройства на VHDL с комментариями, листинг файла теста.

- 5. Временные диаграммы симуляции работы устройства.

- б. Листинг отчета синтезатора о быстродействии, количестве занятых ресурсов.

- 7. Выводы по работе.

# 3. ЛАБОРАТОРНАЯ РАБОТА №3 ИССЛЕДОВАНИЕ БАЗОВЫХ АЛГОРИТМОВ ЦОС НА МАС-АРХИТЕКТУРЕ

*Цель работы:* составить VHDL-описание устройства в соответствии с вариантом на базе MAC-ядра, получить временные диаграммы его работы, оценить объем занимаемых ресурсов и быстродействие.

### 3.1. Теоретические сведения

МАС-ядро является основной составной частью многих устройств ЦОС. Например, для реализации КИХ-фильтра к МАС-ядру необходимо добавить буфер входных отсчетов, буфер для хранения коэффициентов, счетчик и другие элементы. Аналогичным образом реализуется БИХ-фильтр.

МАС-ядро может применяться в генераторах сигналов синусоидальной формы. Существует несколько аналитических (вычислительных) методов формирования синусоидальных сигналов. Остановимся на двух из них. Первый из таких методов основан на формулах суммы двух углов:

$$sin(\alpha+\beta)=sin(\alpha)\cdot cos(\beta)+cos(\alpha)sin(\beta),

cos(\alpha+\beta)=cos(\alpha)\cdot cos(\beta)+sin(\alpha)sin(\beta).$$

(3.1)

Этот метод применим для последовательной генерации отсчетов одной синусоиды и позволяет вычислить очередной отсчет функции, например  $sin(a\cdot n) = sin(a\cdot (n-1)+a)$ , через предыдущий  $sin(a\cdot (n-1))$ . Использовав  $a\cdot (n-1)$  в качестве  $\alpha$  и a в качестве  $\beta$  и обозначив S1 = sin(a), C1 = cos(a),  $Sn(n) = sin(a\cdot n)$ ,  $Cn(n) = cos(a\cdot n)$ , получим следующие выражения для вычисления очередных значений синуса и косинуса:

$$Sn(n) = C1 \cdot Sn(n-1) + S1 \cdot Cn(n-1),$$

$$Cn(n) = C1 \cdot Cn(n-1) - S1 \cdot Sn(n-1).$$

(3.2)

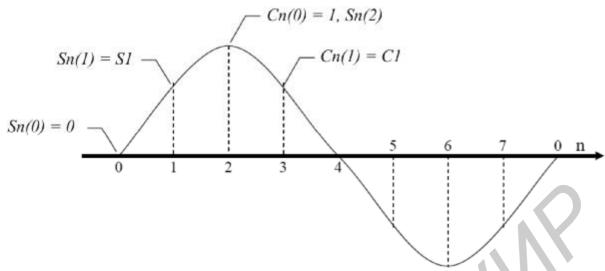

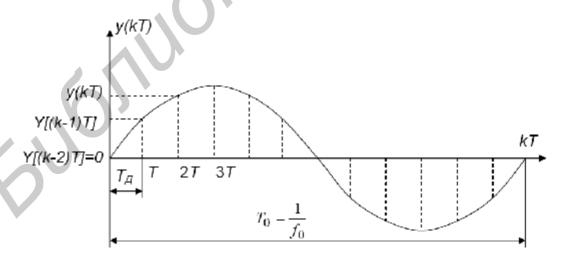

Исходными данными для вычисления первой гармоники (с минимальной возможной частотой) являются следующие значения: Sn(0) = 0, Cn(0) = 1 – значения синуса и косинуса для нулевого аргумента; N – длина выборки (число отсчетов в первой гармонике);  $a = 2\pi/N$ , – минимальное приращение аргумента и  $S1 = \sin(2\pi/N)$ ,  $C1 = \cos(2\pi/N)$  – значения синуса и косинуса для минимального аргумента. На рис. 3.1 показан пример синусоиды с периодом 8 отсчетов (N = 8).

Учитывая, что исходными значениями для k-й гармоники являются начальный угол  $\beta = a \cdot k$ ,  $Sk = \sin(a \cdot k)$  и  $Ck = \cos(a \cdot k)$ , для их вычисления можно использовать те же самые формулы:

$$Sk(k) = CI \cdot Sk(k-1) + SI \cdot Ck(k-1),$$

$$Ck(k) = CI \cdot Ck(k-1) - SI \cdot Sk(k-1).$$

(3.3)

Исходными данными для вычисления, как и в выражении (3.2), являются значения: Sk(0) = 0 и Ck(0) = 1.

Рис. 3.1. Синусоида с начальными значениями SIN и COS

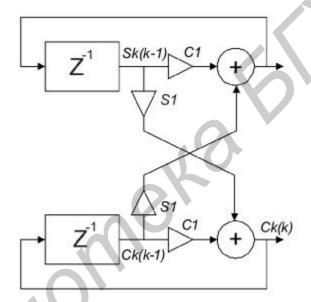

Рис. 3.2. Генератор сигналов SIN и COS

Второй способ заключается в использовании неустойчивого звена второго порядка. За основу построения генератора синусоидальных колебаний (рис. 3.2) взято простейшее рекурсивное звено 2-го порядка — цифровой резонатор, передаточная функция которого имеет вид

$$T_{II}(z) = \frac{1}{1 - b_{1z}^{-1} - b_{2z}^{-1}}. (3.4)$$

Условиями устойчивости такого звена является выполнение соотношений  $|b_1|<2$ ;  $b_2<0$ ;  $|b_2|<1$ . Резонансные свойства цифрового резонатора характеризуются полосой пропускания (по уровню 0,707 от максимального):

$$2\Delta w = 2 \times 2p\Delta f = \frac{1}{T_{\pi}} 2 \arcsin \frac{1 + b_2}{2\sqrt{-b_2}},$$

(3.5)

и добротностью

$$Q = \omega_0 / 2\Delta\omega$$

, (3.6)

где  $\omega_0$  – резонансная частота.

$$w_0 = 2pf_0 = \frac{1}{T_{\pi}} 2\arcsin\frac{b_1}{2\sqrt{|b_2|}}.$$

(3.7)

Видно, что при  $b_2 = -1$  звено становится неустойчивым:

$$2\Delta w = \frac{1}{T_{\pi}} 2 \arcsin \frac{1-1}{2\sqrt{1}} = 0, Q = \frac{w_0}{0} \to \infty,$$

(3.8)

и начинают генерироваться колебания при получении начального возбуждения.

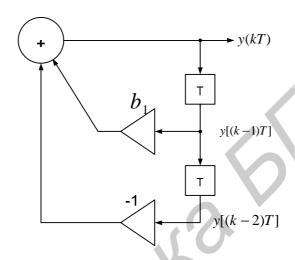

Разностное уравнение  $y(kT)=y_T(k)=x_T(k)+b_1y_T(k-1)+b_2y_T(k-2)$  при  $x_T(k)=0$ ,  $b_2=-1$  получает вид  $y(kT)=y_T(k)=b_1y_T(k-1)-y_T(k-2)$ . Схема генератора показана на рис. 3.3.

Рис. 3.3. Структурная схема генератора синусоидальных колебаний

Для работы генератора необходимо сформировать начальное возбуждение, т.е. ввести начальные значения  $y_T(k-2)$  и  $y_T(k-1)$  (рис. 3.4).

Рис. 3.4. Пояснение к формированию начальных условий

Из рис. 3.4 видно, что можно ввести любые два соседних отсчета. Для удобства примем  $y_T(k-2)=0$ , тогда

$$y_T(k-1) = \sin 2p \frac{T_A}{T_0} = \sin 2p \frac{f_0}{f_A}.$$

(3.9)

Таблица 4.1

# Варианты заданий

| Вариант | Устройство                                           |

|---------|------------------------------------------------------|

| 1       | КИХ-фильтр, порядок 8                                |

| 2       | БИХ-фильтр, порядок 4                                |

| 3       | Генератор синусоиды на основе рекурсивных вычислений |

| 4       | Генератор синусоиды на основе звена второго порядка  |

# 3.2. Порядок выполнения работы

- 1. Изучить теоретические сведения по теме лабораторной работы.

- 2. Получить у преподавателя задание для выполнения практической части работы (табл. 3.1).

- 3. На языке VHDL составить структурное описание устройства в соответствии с вариантом.

- 4. Синтезировать устройство, проверить его работу. Оценить быстродействие, количество занимаемых в ПЛИС ресурсов и энергопотребление.

- 5. Показать результат работы устройства преподавателю.

- 6. Оформить и защитить отчет по лабораторной работе.

# 3.3. Содержание отчета

- 1. Цель работы.

- 2. Краткие теоретические сведения.

- 3. Схема синтезируемого устройства.

- 4. Описание устройства на VHDL с комментариями, листинг файла теста.

- 5. Временные диаграммы симуляции работы устройства.

- 6. Листинг отчета синтезатора о быстродействии, количестве занятых ресурсов.

- 7. Выводы по работе.

# 4. ЛАБОРАТОРНАЯ РАБОТА №4 ПРОЦЕССОР НА РАСПРЕДЕЛЕННОЙ АРИФМЕТИКЕ

*Цель работы*: составить VHDL-описание КИХ-фильтра на базе распределенной арифметики, получить временные диаграммы его работы, оценить объем занимаемых ресурсов и быстродействие.

#### 4.1. Теоретические сведения

#### 4.1.1. Прямой механизм распределенной арифметики

В основе распределенной арифметики (DA – distributed arithmetic) лежат последовательные побитовые вычислительные операции, осуществление которых позволяет получать выходной результат из пары входных векторов на каждом отдельном этапе вычисления. Преимуществом распределенной арифметики является исключительная эффективность реализации. Недостатком может быть названа невысокая скорость получения результата, из-за изначально присущего этому механизму последовательного способа поступления входных данных.

Прямой механизм распределенной арифметики предполагает вычисление выражения следующего вида:

$$y = \sum_{k=1}^{K} A_k x_k \,, \tag{4.1}$$

где К – количество частичных произведений;

$A_{\kappa}$  – постоянные коэффициенты;

$x_k$  — входные слова данных.

Если каждое входное слово данных  $x_k$  является нормированным двоичным числом в дополнительном коде, т.е. выполняется условие, что  $|x_k| \le 1$ , то данное слово можно записать в следующем виде:

$$x_k = -b_{k0} + \sum_{n=1}^{N-1} b_{kn} 2^{-n} , \qquad (4.2)$$

где  $b_{k0}$  – знаковый разряд;

$b_{kn}$  – значения бит;

N – разрядность входных чисел.

Подставив выражение (4.2) в (4.1), можно получить:

$$y = \sum_{k=1}^{K} A_k \left[ -b_{k0} + \sum_{n=1}^{N-1} b_{kn} 2^{-n} \right] = \sum_{k=1}^{K} A_k \left( -b_{k0} \right) + \sum_{n=1}^{N-1} \left[ \sum_{k=1}^{K} A_k b_{kn} \right] 2^{-n} . \tag{4.3}$$

Так как каждый бит  $b_{kn}$  может принимать только 2 значения (0 или 1), то сумма  $\sum A_k b_{kn}$  может принимать  $2^K$  возможных значений. Аналогично и сумма  $\sum A_k (-b_{k0})$  имеет  $2^K$  возможных значений. Подсчитав все значения, можно сохранить их в памяти размером  $2\times 2^K$  слов. Разрядность слов памяти при этом будет

определяться разрядностью постоянных коэффициентов  $A_{\kappa}$  (в большинстве случаев также равна N).

Для вычисления выражения (4.3) достаточно сложить вместе N соответствующих значений, хранимых в памяти, которые сдвигаются влево на необходимое число разрядов (что соответствует присутствующему в рассматриваемом выражении умножению на  $2^{-n}$ ). При этом используется только одно значение из части памяти, хранящей суммы вида  $\sum A_k(-b_{k0})$ , и N-1 значений из части памяти, хранящей суммы вида  $\sum A_k b_{kn}$ . Для выполнения данного сложения достаточно одного сумматора.

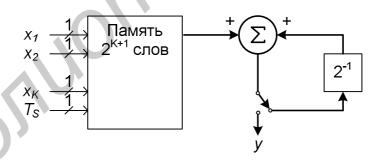

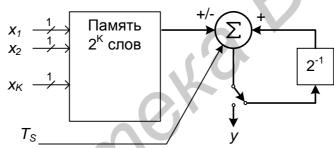

Если сопровождать появление знаковых разрядов специальным сигналом  $T_{\rm S}$ , то его можно использовать для выбора требуемой части памяти. В этом случае входные данные, вводимые последовательно (начиная с младших битов), можно использовать для прямой адресации памяти. Тогда в каждом такте выхода памяти может сниматься требуемая сумма  $\sum A_k(-b_{k0})$ , которая должна суммироваться с предыдущим значением, сдвинутым на 1 разряд влево (умноженным на  $2^{-1}$ ). После N таких циклов на выходе сумматора будет содержаться требуемый результат. Таким образом, сумматор необходимо охватить петлей обратной связи, содержащей элемент сдвига влево на 1 разряд, а также переключателем, который будет коммутировать выход сумматора либо на цепь обратной связи (в процессе вычисления), либо на выход схемы (при готовности результата).

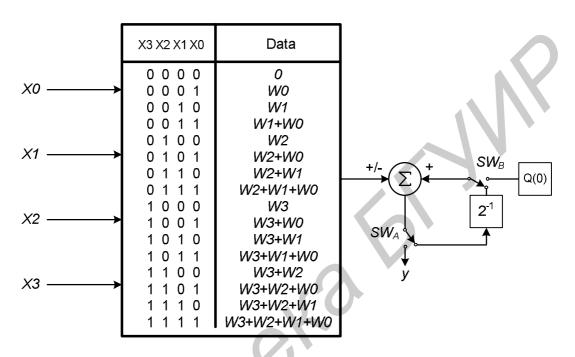

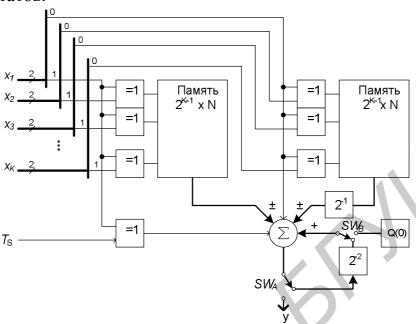

Структура схемы, реализующей выражение (4.1) на распределенной арифметике в соответствии с вышерассмотренной методикой, приведена на рис. 4.1. Содержимое блока памяти, определенное в соответствии с выражением (4.3) сведено в табл. 4.1.

Рис. 4.1. Реализация вычисления на распределенной арифметике (память  $2^{K+1}$  слов)

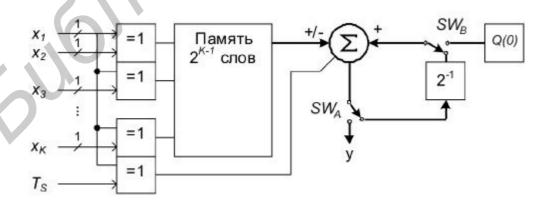

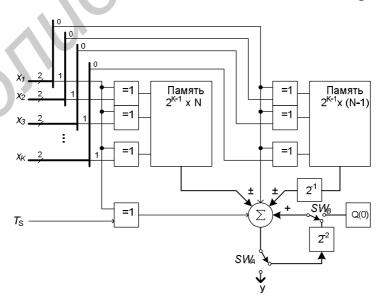

#### 4.1.2. Уменьшение размера памяти

Уменьшение размера используемой памяти в два раза (до  $2^K$  слов) можно достичь путем замены сумматора на рис. 4.1 сумматором/вычитателем. В данном случае сигнал  $T_S$  можно использовать в качестве управляющего сигнала для переключения режимов сложения/вычитания, как показано на рис. 4.2.

| В     | Входной код |          |     |          | Содержимое па  | - B   | Входной код |          |       | Содержимое | па-               |                  |

|-------|-------------|----------|-----|----------|----------------|-------|-------------|----------|-------|------------|-------------------|------------------|

| $T_s$ | $b_{In}$    | $b_{2n}$ | • • | $b_{Kn}$ | МЯТИ           | $T_s$ | $b_{1n}$    | $b_{2n}$ | • • • | $b_{Kn}$   | МЯТИ              |                  |

|       | 0           | 0        | 0   | 0        | 0              |       | 0           | 0        | 0     | 0          | 0                 |                  |

|       | 1           | 0        | 0   | 0        | $A_{I}$        |       | 1           | 0        | 0     | 0          | $-A_1$            |                  |

|       | 0           | 1        | 0   | 0        | $A_2$          |       | 0           | 1        | 0     | 0          | $-A_2$            |                  |

|       | 1           | 1        | 0   | 0        | $A_1+A_2$      |       | 1           | 1        | 0     | 0          | $-(A_1+A_2)$      |                  |

|       |             |          |     |          |                |       |             |          |       |            |                   |                  |

| 0     | 0           | 0        | 0   | 1        | $A_K$          | 1     | 0           | 0        | 0     | 1          | $-A_K$            |                  |

|       | 1           | 0        | 0   | 1        | $A_1 + A_K$    |       | 1           | 0        | 0     | 1          | $-(A_I+A_K)$      |                  |

|       | 0           | 1        | 0   | 1        | $A_2+A_K$      |       | 0           | 1        | 0     | 1          | $-(A_2+A_K)$      |                  |

|       | 1           | 1        | 0   | 1        | $A_1+A_2+A_K$  |       | 1           | 1        | 0     | 1          | $-(A_1+A_2+A_K)$  |                  |

|       | •••         |          |     |          | •••            |       | •••         |          |       |            |                   |                  |

|       | 1           | 1        | 1   | 1        | $A_1+A_2++A_K$ |       | 1           | 1        | 1     | 1          | $-(A_1+A_2++A_n)$ | . <sub>K</sub> ) |

T<sub>S</sub> - контроль знака:

$T_S = 0$  - сложение;

$T_S = 1$  - вычитание

Рис. 4.2. Реализация вычисления на распределенной арифметике (память  $2^K$  слов)

Размер таблицы памяти можно уменьшить до  $2^{K-1}$  слов с помощью использования смещенного двоичного кода. Для этого входное слово данных  $x_k$  представляется в следующем виде:

$$x_k = \frac{1}{2} [x_k - (-x_k)], \tag{4.4}$$

где  $-x_k$  – отрицательное значение слова данных  $x_k$  (в дополнительном коде):

$$-x_k = -\overline{b}_{k0} + \sum_{n=1}^{N-1} \overline{b}_{kn} 2^{-n} + 2^{-(N-1)}.$$

(4.5)

Здесь  $\overline{b}_{kn}$ ,  $\overline{b}_{k0}$  — инверсные значения бит  $b_{kn}$ ,  $b_{k0}$ .

С учетом выражений (4.2) и (4.5) выражение (4.4) примет следующий вид:

$$x_{k} = \frac{1}{2} \left[ -b_{k0} + \sum_{n=1}^{N-1} b_{kn} 2^{-n} - \left( -\overline{b}_{k0} + \sum_{n=1}^{N-1} \overline{b}_{kn} 2^{-n} + 2^{-(N-1)} \right) \right] =$$

$$= \frac{1}{2} \left[ -(b_{k0} - \overline{b}_{k0}) + \sum_{n=1}^{N-1} (b_{kn} - \overline{b}_{kn}) 2^{-n} - 2^{-(N-1)} \right].$$

(4.6)

Для упрощения обозначений целесообразно ввести новые переменные, значения которых лежат в пределах  $\pm 1$ :

$$c_{kn} = b_{kn} - \overline{b}_{kn}, \ c_{k0} = -(b_{k0} - \overline{b}_{k0}).$$

(4.7)

С учетом выражения (4.7) можно записать

$$x_k = \frac{1}{2} \left[ \sum_{n=1}^{N-1} c_{kn} 2^{-n} - 2^{-(N-1)} \right]. \tag{4.8}$$

Подставив данное выражение в (4.1), можно получить уравнение для вычисления требуемой суммы произведений:

$$y = \frac{1}{2} \sum_{k=1}^{K} A_k \left[ \sum_{n=0}^{N-1} c_{kn} 2^{-n} - 2^{-(N-1)} \right] = \sum_{n=0}^{N-1} Q(b_n) 2^{-n} + 2^{-(N-1)} Q(0),$$

(4.9)

где функции  $Q(b_n)$  и Q(0) задаются следующим образом:

$$Q(b_n) = \sum_{k=1}^{K} \frac{A_k}{2} c_{kn}, \ Q(0) = -\sum_{k=1}^{K} \frac{A_k}{2}.$$

(4.10)

Функция  $Q(b_n)$  имеет  $2^K$  возможных значений, которые могут быть размещены в памяти в соответствии с содержимым табл. 4.2.

Значения Q в нижней части таблицы являются зеркальным отражением верхней части, но с противоположным знаком. Из приведенной таблицы можно увидеть, что, выполняя сложение по модулю два бит  $b_{In}$  с оставшимся набором  $b_{2n}, b_{3n}, \dots b_{Kn}$ , можно получить адрес для чтения из памяти соответствующего значения Q (без учета знака). Используя сигнал  $b_{In}$  в качестве сигнала управления сложением/вычитанием, можно получить требуемый знак считываемого из памяти значения. Во время появления на входах знаковых разрядов сигнал управления сложением/вычитанием должен быть проинвертирован, что может быть реализовано путем сложения по модулю сигналов  $b_{In}$  и  $T_S$ . Соответствующая структурная схема приведена на рис. 4.3. Благодаря такой реализации размер таблицы памяти уменьшается до  $2^{K-I}$  слов.

Когда младшие биты слов  $x_k$  осуществляют адресацию, значение, считываемое из памяти, в соответствии с выражением (4.9) должно быть скорректировано на величину Q(0). Это осуществляется путем коммутации выхода регистра, содержащего значение Q(0), с помощью переключателя  $SW_B$  на вход аккумулятора. Последующие значения, считываемые из памяти, суммируются со сдвинутой вправо на 1 разряд суммой.

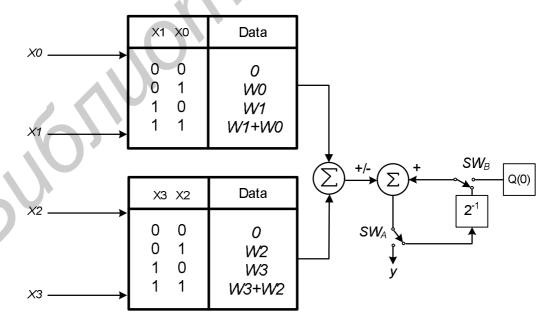

Объем требуемой памяти можно уменьшить и другим способом. На рис. 4.4 показан КИХ-фильтр в обычной реализации. Для такой реализации фильтра 4 порядка требуется 16 ячеек памяти.

Таблица 4.2 Содержимое блока памяти ( $2^{K}$  слов)

| В        | ходной ко | ОД       | Сопорудимое немати. О |                   |                                              |

|----------|-----------|----------|-----------------------|-------------------|----------------------------------------------|

| $b_{In}$ | $b_{2n}$  | $b_{3n}$ | •••                   | $b_{\mathit{Kn}}$ | Содержимое памяти, Q                         |

| 0        | 0         | 0        | 0                     | 0                 | $-1/2 \cdot (A_1 + A_2 + A_3 + \dots + A_K)$ |

| 0        | 0         | 0        | 0                     | 1                 | $-1/2 \cdot (A_1 + A_2 + A_3 + \dots - A_K)$ |

| 0        | 0         | 1        | 0                     | 0                 | $-1/2 \cdot (A_1 + A_2 - A_3 + \dots + A_K)$ |

| 0        | 0         | 1        | 0                     | 1                 | $-1/2 \cdot (A_1 + A_2 - A_3 + \dots - A_K)$ |

| 0        | 1         | 0        | 0                     | 0                 | $-1/2 \cdot (A_1 - A_2 + A_3 + \dots + A_K)$ |

| 0        | 1         | 0        | 0                     | 1                 | $-1/2 \cdot (A_1 - A_2 + A_3 + \dots - A_K)$ |

| 0        | 1         | 1        | 0                     | 0                 | $-1/2 \cdot (A_1 - A_2 - A_3 + \dots + A_K)$ |

| 0        | 1         | 1        | 0                     | 1                 | $-1/2 \cdot (A_1 - A_2 - A_3 + \dots - A_K)$ |

| 0        | 1         | 1        |                       | 1                 |                                              |

| 0        | 1         | 1        | 1                     | 1                 | $-1/2 \cdot (A_1 - A_2 - A_3 - \dots - A_4)$ |

| 1        | 0         | 0        | 0                     | 0                 | $1/2 \cdot (A_1 - A_2 - A_3 - \dots - A_K)$  |

| 1        | 0         | 0        | 0                     | 1                 | $1/2 \cdot (A_1 - A_2 - A_3 + A_K)$          |

| 1        | 0         | 1        | 0                     | 0                 | $1/2 \cdot (A_1 - A_2 + A_3 - \dots - A_K)$  |

| 1        | 0         | 1        | 0                     |                   | $1/2 \cdot (A_1 - A_2 + A_3 - \dots + A_K)$  |

| 1        | 1         | 0        | 0                     | 0                 | $1/2 \cdot (A_1 + A_2 - A_3 - \dots - A_K)$  |

| 1        | 1         | 0        | 0                     | 1                 | $1/2 \cdot (A_1 + A_2 - A_3 + A_K)$          |

| 1        | 1         | 1        | 0                     | 0                 | $1/2 \cdot (A_1 + A_2 + A_3 - \dots - A_K)$  |

| 1        | 1         | 1        | 0                     | 1                 | $1/2 \cdot (A_1 + A_2 + A_3 - \dots + A_K)$  |

| 1        | 1         | 1        |                       | 1                 |                                              |

| 1        | 1         | 1        | 1                     | 1                 | $1/2 \cdot (A_1 + A_2 + A_3 + \dots + A_K)$  |

Рис. 4.3. Реализация вычисления на распределенной арифметике (память  $2^{K-1}$  слов)

С увеличением порядка фильтра экспоненциально возрастает и объем требуемой памяти. Например, для КИХ-фильтра 128 порядка потребуется память на  $2^{128}$  ячеек. Эта проблема может быть решена путем разбиения фильтра на меньшие подфильтры и суммирования их выходов. Фильтр порядка K может быть разделен на K меньших фильтров (рис. 4.5), порядок каждого равен K ( $K = m \times k$ ). Теперь общий порядок фильтра K не имеет решающего значения для латентности фильтра.

Рис. 4.4. Обычная реализация КИХ-фильтра 4-го порядка на распределенной арифметике

Рис. 4.5. КИХ-фильтр 4 порядка с 2 таблицами

Например, если K = 128, то в обычной реализации понадобится  $2^{128}$  ячеек, а выбрав m = 32 и k = 4, можно снизить требования к памяти до 512 элементов.

#### 4.1.3. Увеличение производительности распределенной арифметики

Увеличение скорости вычисления выражения (4.1) с помощью распределенной арифметики может быть достигнуто двумя способами, которые базируются на разделении входных слов на L частей (причем N должно быть кратно L):

- с использованием большего количества блоков памяти;

- путем экспоненциального увеличения размера памяти.

Следовательно, в первом случае необходимо использовать L блоков памяти одинакового размера ( $2^{K-1}$  слов). Во втором случае блок памяти один, но емкость его возрастает до значения  $\frac{1}{2} \cdot 2^{KL}$  и длина входных переменных увеличивается пропорционально значению  $log_2L$ .

Поскольку во втором случае резкое увеличение занимаемой памяти для ускорения алгоритма приводит к потере выигрыша в занимаемой площади, то дальнейшее внимание будет уделено первому случаю. Использование первого метода для увеличения частоты работы приблизительно в 2 раза (L=2) потребует двукратного увеличения емкости памяти. Данный подход, по сути, является типичным распараллеливанием процесса вычисления.

Поскольку в схемах, приведенных на рис. 4.1–4.3, поступление данных происходит по 1 биту за 1 такт, то такие схемы называются 1-BAAT (one-bit-at-a-time). Аналогично при одновременном поступлении подаче L бит схему можно обозначить как L-BAAT.

Выражения (4.9) и (4.10) для произвольного варианта L-ВААТ примут следующий вид:

$$y = \sum_{n=0}^{(N/L)-1} Q(b_n) 2^{-nL} + 2^{-(B-L)} Q(0),$$

(4.11)

где функции  $Q(b_n)$  и Q(0) задаются следующим образом: