УДК 621.397.46

# РЕАЛИЗАЦИЯ ДЕСЕРИЛАЙЗЕРА TMDS-СИГНАЛОВ ВСТРОЕНЫМИ СРЕДСТВАМИ ПЛИС ФИРМЫ XILINX SPARTAN-6

### Д.В. ЧИСТОБАЕВ

ОАО «Конструкторское бюро «Дисплей» П. Бровки, 13а, Витебск, 210605, Беларусь

Поступила в редакцию 11 декабря 2017

Проведен анализ десералайзеров интерфейсов DVI и HDMI. Составлены рекомендации по применению десерилайзера на ПЛИС Xilinx Spartan-6.

Ключевые слова: проекционная система индикации, десерилайзер, TMDS, ПЛИС.

#### Введение

В настоящее время в видеотехнике остаются популярными видеоинтерфейсы DVI и HDMI, использующие дифференциальные линии TMDS. Такие видеоинтерфейсы также используются в окологлазных дисплеях и микропроекторах. Для преобразования интерфейсов DVI и HDMI в формат микродисплейных модулей и ЖК-матриц используются десерилайзеры. Десерилайзер может быть реализован в виде отдельного корпуса микросхемы, что часто используется в видеоконтроллерах. В ПЛИС семейства Spartan-6 имеются встроенные модули для работы с дифференциальными сигналами TMDS, что существенно упрощает проектирование видеоконтроллера микродисплейного модуля, снижает энергопотребление и габариты печатной платы. TMDS (Transition Minimized Differential Signaling) — дифференциальный сигнал с минимизированными переходами. Такой сигнал лежит в основе интерфейсов DVI — цифровой видеоинтерфейс и HDMI — мультимедийный интерфейс высокой четкости.

# Решения для преобразования видеоинтерфейсов DVI и HDMI

При проектировании видеоконтроллеров дисплейных устройств возникает необходимость преобразовывать стандартные видеоинтерфейсы DVI и HDMI в специализированные интерфейсы микродисплейных модулей или ЖК-матриц. Эту функцию возможно реализовать с помощью специализированных микросхем серилайзеров и десерилайзеров [1, 2].

Примером микросхемы десерилайзера является TFP401 фирмы Texas Instruments. Эта микросхема позволяет декодировать изображение формата Full HD 1080p.

Основные технические характеристики TFP401:

- разрешение входного сигнала  $1920 \times 1080$  (60 Гц);

- пиксельная частота 165 МГц;

- потребляемая мощность 1,2 Вт.

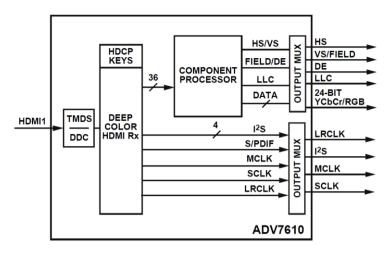

Более компактным решением является микросхема ADV7610 фирмы Analog Devices. Структурная схема данной микросхемы приведена на рис. 1. Она реализована в CSP\_BGA корпусе размером  $6\times6$  мм.

Основные технические характеристики ADV7610:

- разрешение входного сигнала  $1920 \times 1080 (60 \Gamma \text{ц})$ ;

- пиксельная частота 165 МГц;

- потребляемая мощность 1 Вт.

Рис. 1. Структурная схема ADV7610

Для микродисплейных модулей и ЖК-матриц с разрешением не более  $1280 \times 1024$  (60 Гц) можно реализовать распаковку сигнала TMDS с помощью встроенных модулей ПЛИС Spartan-6 фирмы Xilinx [3].

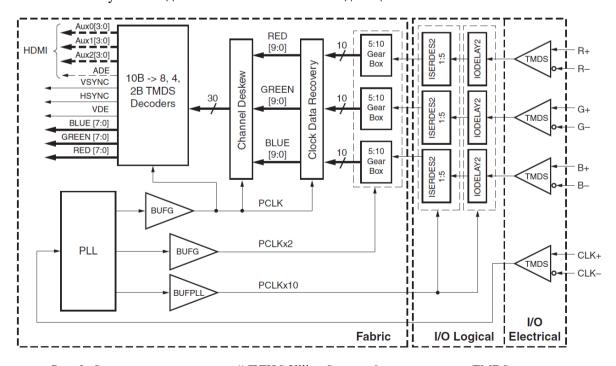

Принцип конфигурации модулей для декодирования TMDS-сигналов представлен на рис. 2.

На схеме видно, что после преобразования получается декодированный видеосигнал RGB 24bit с синхронизирующими импульсами VSYNC, HSYNC, VDE. Далее его можно использовать для подключения большинства ЖК-матриц или для обработки и преобразования в интерфейс микродисплейного модуля или других устройств отображения в пользовательской программе ПЛИС. Встроенная программа ПЛИС позволяет более тонко настроить задержки синхроимпульсов, реализовать при необходимости запоминание строки кадра входного изображения, организовать шину управления подключенной ЖК-матрицы или микродисплейного модуля.

Недостатком данного решения является ограниченная частота входного сигнала, что не позволяет декодировать TMDS сигналы частотой более 1080 МГц. Преимуществами являются уменьшение энергопотребления, количества корпусов микросхем и массы видеоконтроллера, что является актуальным для окологлазных систем индикации.

Рис. 2. Схема включения модулей ПЛИС Xilinx Spartan-6 для распаковки TMDS-сигналов

#### Заключение

В работе дан анализ решений для преобразований интерфейсов DVI и HDMI в специализированные интерфейсы микродисплейных модулей или ЖК-матриц. Наиболее дешевым решением является применение специализированных микросхем. При необходимости преобразования в нестандартные интерфейсы возможным решением может быть использование встроенных модулей ПЛИС Spartan-6, которое обеспечит работу интерфейса с разрешением не более  $1280 \times 1024$  (60  $\Gamma$ ц). Используя решение на ПЛИС, можно более гибко настроить выходной интерфейс уменьшить габариты печатной платы и массу устройства.

# DESERIALIZATION OF TMDS SIGNALS USING EMBEDDED DEVICES IN FPGA XILINX SPARTAN-6

#### D.V. CHISTOBAEV

#### **Abstract**

The analysys of descrilizer of DVI and HDMI interfaces is conducted. Recommendations on the use of descrilizer on FPGA Xilinx Spartan-6 are given.

Keywords: projection display system, deserilizer, TMDS, FPGA.

# Список литературы

- 1. Supreetha Rao, Kiran Kumar V.G, Kanhu Charan Padhy // VHDL Implementation of TMDS encoder for the transmission of video signals in serial communication [Электронный ресурс]. Режим доступа: http://ijarcet.org/wp-content/uploads/IJARCET-VOL-4-ISSUE-4-1576-1579.pdf.

- 2. High-Definition Multimedia Interface Specification Version 1.3a. [Электронный ресурс]. Режим доступа: http://www.fpga4fun.com/files/HDMISpecification13a.pdf.

- 3. Bob Feng // XILINX, Implementing a TMDS Video Interface in the Spartan-6 FPGA. [Электронный ресурс]. Режим доступа: https://www.xilinx.com/support/documentation/application\_notes/xapp495\_S6TMDS\_ Video\_Interface.pdf.