# Министерство образования Республики Беларусь Учреждение образования «Белорусский государственный университет информатики и радиоэлектроники»

Факультет радиотехники и электроники

Кафедра микро- и наноэлектроники

А. Г. Черных, Д. Б. Мигас, А. А. Лешок

# ТЕХНОЛОГИЯ ИЗГОТОВЛЕНИЯ КМОП-ТРАНЗИСТОРОВ

Рекомендовано УМО по образованию в области информатики и радиоэлектроники в качестве учебно-методического пособия для специальностей 1-41 01 02 «Микро- и наноэлектронные технологии и системы», 1-41 01 04 «Нанотехнологии и наноматериалы в электронике»

#### Рецензенты:

кафедра физики твердого тела Белорусского государственного университета (протокол №5 от 07.12.2017);

профессор кафедры микро- и нанотехники Белорусского национального технического университета доктор технических наук, профессор В. А. Сычик

#### Черных, А. Г.

Ч-49 Технология изготовления КМОП-транзисторов : учеб.-метод. пособие / А. Г. Черных, Д. Б. Мигас, А. А. Лешок. – Минск : БГУИР, 2018.-71 с. : ил.

ISBN 978-985-543-430-7.

Рассмотрены конструктивно-технологические особенности изготовления КМОП-транзисторов для ИМС. Определены физические ограничения и ключевые технологические процессы КМОП-элементов с проектными нормами менее 90 нм. Рассмотрены методы формирования КМОП-структур с high-k-диэлектриком и металлическим затвором, а также различные типы многозатворных МОП-транзисторов.

УДК 621.382.3(076) ББК 32.852.3я73

ISBN 978-985-543-430-7

<sup>©</sup> Черных А. Г., Мигас Д. Б., Лешок А. А., 2018

<sup>©</sup> УО «Белорусский государственный университет информатики и радиоэлектроники», 2018

# СОДЕРЖАНИЕ

| ВВЕДЕНИЕ                                                  | 4  |

|-----------------------------------------------------------|----|

| 1 КМОП-СТРУКТУРА И БАЗОВЫЕ ТЕХНОЛОГИЧЕСКИЕ ОПЕРАЦИИ       | 5  |

| 2 НАЧАЛЬНЫЙЭТАП ФОРМИРОВАНИЯ КМОП-ТРАНЗИСТОРОВ            | 8  |

| 2.1 Формирование карманов                                 | 8  |

| 2.2 Изоляция                                              | 12 |

| 2.3 Легирование канала                                    | 16 |

| 2.4 Подзатворный диэлектрик                               | 18 |

| 2.5 Электрод затвора                                      | 20 |

| 2.6 Формирование истока, стока                            | 22 |

| 3 ЗАКЛЮЧИТЕЛЬНЫЙ ЭТАП ФОРМИРОВАНИЯ                        |    |

| КМОП-ТРАНЗИСТОРОВ                                         | 26 |

| 3.1 Металлизация на основе пленок алюминия                | 26 |

| 3.2 Металлизация на основе пленок мели                    | 30 |

| 3.3 Планаризация рельефа                                  | 36 |

| 4 КОНСТРУКТИВНО-ТЕХНОЛОГИЧЕСКИЕ ОСОБЕННОСТИ               |    |

| ИЗГОТОВЛЕНИЯ КМОП-ТРАНЗИСТОРОВ                            | 41 |

| 4.1 Аномальные эффекты и методы улучшения характеристик   |    |

| КМОП-транзисторов                                         | 41 |

| 4.2 Структура «кремний на изоляторе»                      | 46 |

| 4.3 Подзатворный high-k-диэлектрик и металлический затвор | 52 |

| 4.4 Напряженный кремний в КМОП-транзисторах               | 61 |

| 4.5 Многозатворные МОП-структуры                          | 65 |

| ЛИТЕРАТУРА                                                | 70 |

## **ВВЕДЕНИЕ**

Технология комплементарных МОП-транзисторов (КМОП) играет большую роль в развитии ИМС. С уменьшением размеров полевых МОП-транзисторов число транзисторов на кристалле увеличивается и улучшаются функциональные возможности ИМС. В то же время скорость переключения полевых МОП-транзисторов и схем увеличивается и быстродействие ИМС улучшается.

Как известно, еще в 1965 году Гордон Мур зафиксировал эмпирическое наблюдение, получившее впоследствии название закона Мура. Представив в виде графика рост производительности микросхем памяти, он обнаружил любопытную закономерность: новые модели микросхем разрабатывались спустя равные промежутки времени — примерно 18–24 месяца после появления их предшественников, а емкость микросхем при этом возрастала каждый раз примерно вдвое. Если бы такая тенденция продолжилась, заключил Мур, то мощность вычислительных устройств экспоненциально возрастала бы на протяжении относительно короткого промежутка времени, что делало полупроводниковую индустрию весьма перспективной отраслью с точки зрения не только технологических инноваций, но и экономической привлекательности. Наблюдение Гордона Мура впоследствии подтвердилось, при этом с каждым годом гиганты полупроводниковой индустрии в точности подтверждали ставший сакраментальным закон Мура.

Однако серьезным барьером на пути миниатюризации транзисторов является появление аномальных эффектов и, следовательно, токов утечки при работе КМОП-транзистора. Постоянное стремление к миниатюризации КМОП-транзисторов напоминает подъем на все более крутую гору. «Вершины» впереди едва различимы, а невероятные сложности в процессе интеграции новых материалов и структур заставляют «восходителей» тратить невероятные усилия или терять уверенность в себе. Поэтому важным является своевременное внедрение новых материалов и технологических приемов при формировании КМОП-транзисторов. В первом, втором и третьем разделах данного учебнометодического пособия рассмотрены базовые технологические процессы формировании КМОП-транзисторов. В четвертом разделе определены физические ограничения и ключевые технологические процессы КМОП-элементов с проектными нормами менее 90 нм.

# 1 КМОП-СТРУКТУРА И БАЗОВЫЕ ТЕХНОЛОГИЧЕСКИЕ ОПЕРАЦИИ

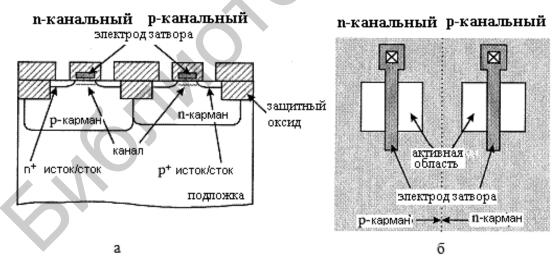

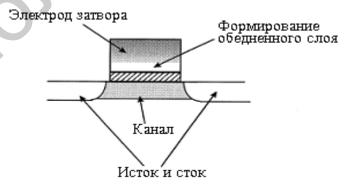

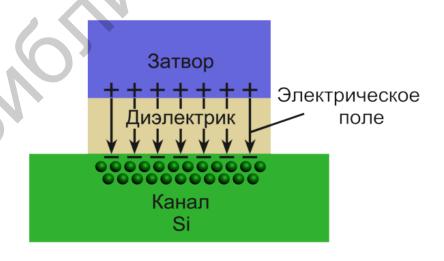

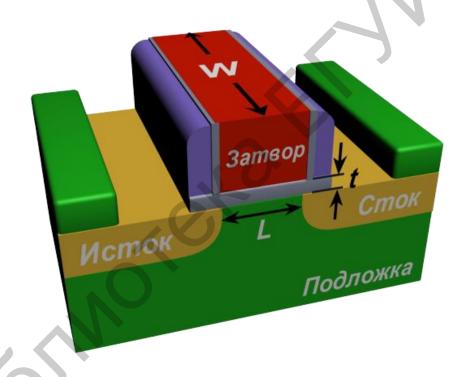

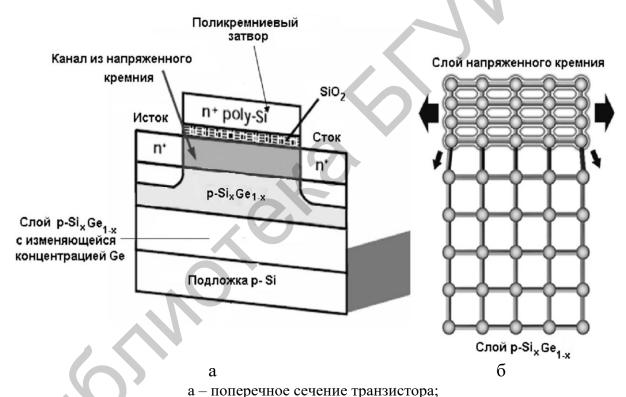

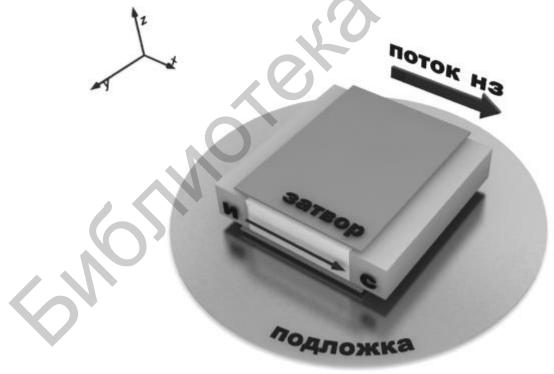

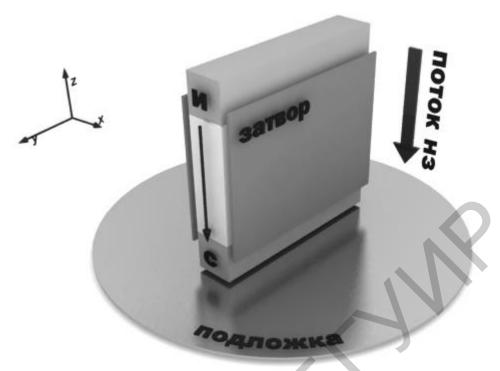

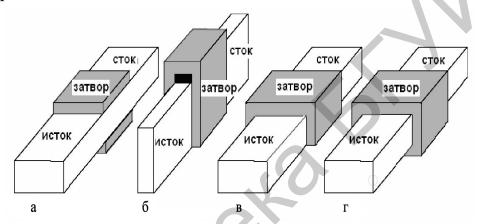

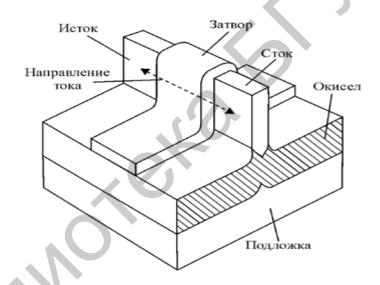

КМОП-структура предусматривает расположение n- и p-канальных МОПтранзисторов на одном кристалле. По сравнению с п-канальными КМОП-схемы потребляют меньшую мощность, однако первоначально разработанная технология формирования КМОП-структур была довольно сложной, а для реализации конструктивных решений требовалась значительная площадь кристалла, как каждый п-канальный МОП-транзистор использовался транзистором. По мере возрастания р-канальным плотности упаковки п-канальных МОП-схем с целью уменьшения потребления энергии технологический процесс формирования этих схем был усложнен. Стали использоваться дополнительные фотошаблоны, что позволило создавать транзисторы с разными величинами порогового напряжения. Одновременно новые схемотехнические решения позволили упростить технологический процесс формирования КМОП-схем, поэтому В настоящее время технологии формирования п-канальных МОП и КМОП ИМС почти одинаковы по сложности. В настоящее время КМОП-технология, которая вобрала в себя все преимущества и достижения микроэлектроники, стала одной из наиболее важных технологических схем формирования ИМС. На рисунке 1 показана структура КМОП-транзистора. Каждый полевой транзистор состоит из управляющего электрода (электрода затвора), истока, стока и канала. Смещение затвора контролирует ток носителей от истока к стоку через слой канала.

а – КМОП-структура в разрезе; б – топология КМОП-структуры Рисунок 1 – Структура КМОП-транзистора

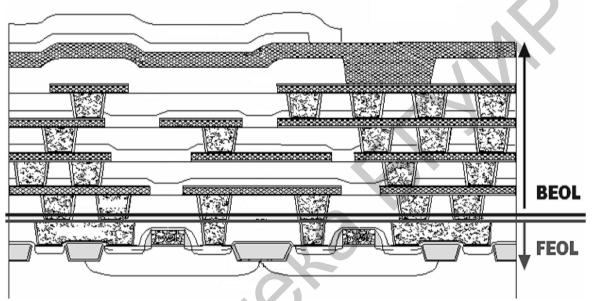

Технологический маршрут изготовления кремниевых ИМС обычно делится на две части. Первая часть маршрута называется front end processing или front end of line (FEOL) и включает процессы изготовления активных приборов (транзисторов). Вторая часть носит название back end processing или back end of

line (BEOL) и включает в себя процессы формирования межэлементных соединений и межуровневой разводки. Визуальное представление деления маршрута на процессы FEOL и BEOL показано на рисунке 2.

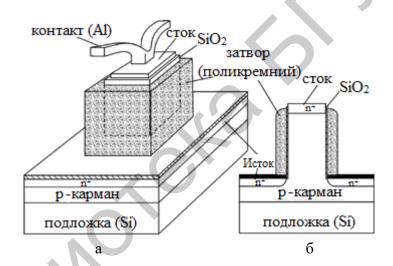

Рисунок 3, а показывает маршрут формирования КМОП-структуры, и базовый технологический процесс изготовления КМОП-транзисторов — показывает рисунок 3, б. Первая технологическая операция — формирование р-кармана и n-кармана (двойной карман) в кремниевой подложке. Поскольку КМОП-структура имеет два типа полевых транзисторов, n-МОП сформирован в p-кармане и p-МОП — в n-кармане.

Рисунок 2 — Визуальное представление деления маршрута изготовления ИМС на процессы FEOL и BEOL

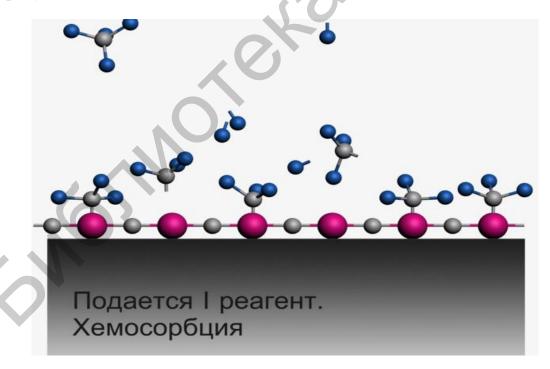

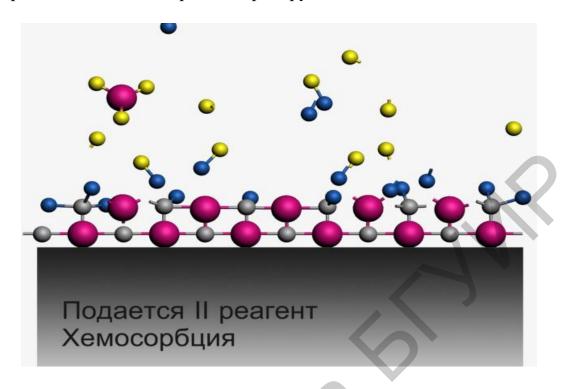

Процесс изоляции — формирование защитного слоя оксида, чтобы отделить активную область каждого МОП-транзистора в карманах одного типа. После этого в область канала вводят примесь, чтобы отрегулировать пороговое напряжение для каждого типа полевого транзистора. Пленка подзатворного диэлектрика, обычно диоксид кремния ( $SiO_2$ ), выращена термическим оксидированием, поскольку межфазная плотность между  $SiO_2$  и кремниевой подложкой мала. Поликристаллический кремний осажден как материал электрода затвора, и электрод затвора получен с помощью фотолитографии и реактивного ионного травления.

Длина канала ( $L_g$ ) является критическим размером, поскольку  $L_g$  определяет рабочие характеристики МОП-транзисторов, и должна быть небольшой, чтобы улучшить рабочие характеристики прибора. В области истока и стока МОП-транзисторов примесь легируется ионной имплантацией. В этой технологической операции электроды затвора выступают в роли самосовмещенной маски, покрывающей область канала. После этого выполняется термический отжиг для активации примеси диффузионных слоев. Технология самосовмещенного затвора применяется для получения электрода затвора и областей истока и стока, чтобы уменьшить паразитную емкость «затвор — исток/сток». Обычно при изготовлении МОП-

транзисторов используется двухслойная конструктивно-технологическая структура затвора: нижний слой — поликристаллический кремний, верхний — низкоомный слой силицида.

а – технологический маршрут; б – базовые технологические процессы Рисунок 3 – Базовый технологический процесс изготовления КМОП-транзисторов

В заключение выполняется процесс металлизации, чтобы сформировать межсоединения слоев. В развитии технологических процессов формирования металлизации можно выделить три этапа. На первом этапе металлизация ИМС была однослойной и основу ее составлял один материал — алюминий. На втором этапе металлизация стала многослойной, содержащей различные материалы. Появилось деление ее слоев по функциональному назначению, однако алюминий по-прежнему оставался основой коммутирующей разводки. На третьем этапе произошла замена алюминия на медь, что привело к усложнению структуры металлизации и существенным изменениям в технологическом процессе формирования. Последние два этапа характеризуются также постепенным ростом числа уровней разводки.

# 2 НАЧАЛЬНЫЙ ЭТАП ФОРМИРОВАНИЯ КМОП-ТРАНЗИСТОРОВ

## 2.1 Формирование карманов

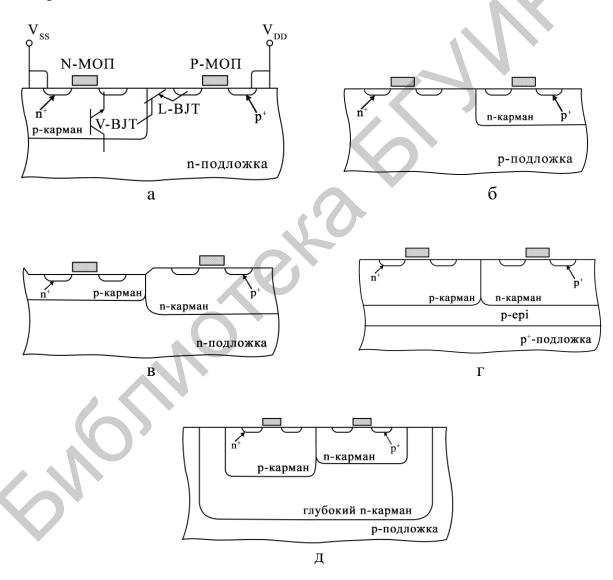

На рисунке 4 показаны структуры кармана, которые классифицированы по шести типам: р-карман, п-карман, сдвоенный карман с использованием одного фотошаблона, строенный карман, сдвоенный карман со скрытыми р<sup>+</sup>- и п<sup>+</sup>-слоями и сдвоенный карман на р-ері/р<sup>+</sup>-подложке. Первый технологический вариант (рисунок 4, а, б) предполагает изготовление одной МОП-структуры на подложке, а другой – в кармане.

а – p-карман; б – n-карман; в – самосовмещенные, сдвоенные карманы; г – сдвоенные карманы на p-ері/p+-подложке; д – сдвоенные и глубокие карманы Рисунок 4 – Структуры карманов КМОП-транзистора

Так, р-карман создается ионной имплантацией в подложку n-типа (см. рисунок 4, а). При этом концентрация легирующей примеси должна быть достаточно высокой, чтобы перекомпенсировать примесь n-типа и обеспечить необходимый уровень легирования в р-кармане. Для создания легко управляемого уровня легирования в р-кармане его уровень легирования должен в 5–10 раз превышать уровень легирования подложки n-типа. Однако такое излишнее легирование приводит к возникновению нежелательных эффектов в n-канальных транзисторах, которые выражаются в увеличении обратного смещения на затворе и увеличении емкости между областями истока — стока и p-карманом.

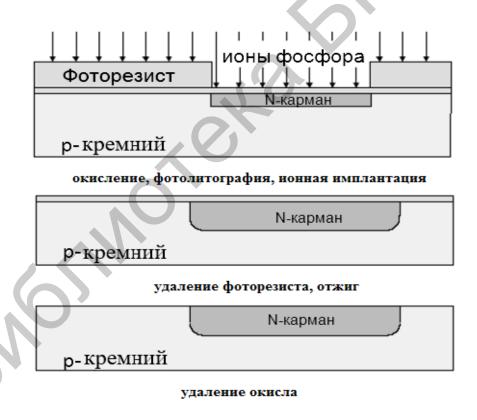

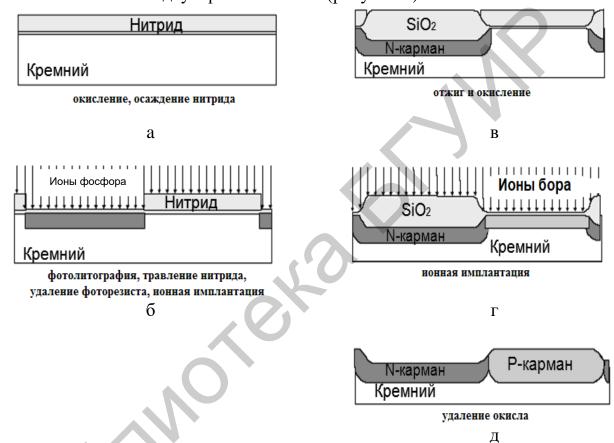

Второй технологический вариант заключается в создании п-карманов для формирования р-канальных транзисторов. Как показано на рисунке 4, б, п-канальные приборы формируют в подложке с проводимостью р-типа. В таком варианте примесь п-типа в п-кармане перекомпенсирует уровень легирования подложки р-типа проводимости и излишнее легирование приводит к ухудшению характеристик р-канальных приборов. Последовательность технологического процесса формирования кармана п-типа для однокарманной технологии показана на рисунке 5.

Рисунок 5 – Последовательность формирования кармана п-типа

На рисунке 4, в представлен вариант, когда в очень слаболегированном кремнии п-типа формируют два отдельных кармана. Такой «двухкарманный» вариант создания КМОП-структур позволяет получать профили легирования в каждом кармане независимо, и поэтому ни один из типов приборов не должен

испытывать действия эффектов, связанных с излишним легированием. Формирование ИМС по такому варианту предполагает использование слаболегированных подложек с проводимостью п-типа или р-типа. Последовательность технологического процесса формирования карманов с использованием одного фотошаблона (самосовмещенные карманы) показана на рисунке 6.

Однако этот технологический вариант обладает недостатками: подложка имеет неплоскостную поверхность, сложно проконтролировать уровень легирования. Поэтому чаще используют технологию двойного раздельного легирования с использованием двух фотошаблонов (рисунок 7).

Рисунок 6 – Последовательность формирования самосовмещенных карманов

В некоторых случаях, таких как в ИМС смешанных сигналов, иногда произвольно формируется глубокий слой п-кармана, как показано на рисунке 4, д, чтобы предотвратить перекрестные помехи между цифровыми и аналоговыми схемами. В этой структуре и n-, и p-карманы электрически изолированы от подложки или других карманов на подложке.

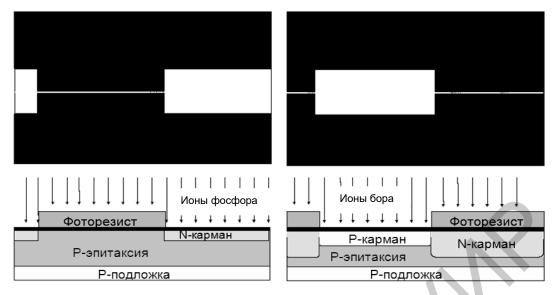

Чтобы реализовать высокую плотность упаковки, топологическая проектная норма кармана должна быть уменьшена; однако в этом случае может возникнуть нежелательный механизм, хорошо известный как эффект защелкивания. Защелкивание (то есть протекание высокого тока между  $V_{DD}$  и  $V_{SS}$ ) вызвано действием паразитных горизонтального p-n-p- и вертикального n-p-n-биполярных транзисторов как показано на рисунке 8, и это иногда нарушает функционирование ИМС.

Рисунок 7 — Последовательность формирования карманов с применением двух фотолитографий

Коллекторы каждого из этих биполярных транзисторов питают базы один одного и вместе составляют p-n-p-n-тиристорную структуру. Чтобы предотвратить защелкивание, важно уменьшить усиление по току  $(h_{FE})$  этих паразитных биполярных транзисторов и концентрация легирующей примеси в области кармана должна быть более высокой. В результате рабочие характеристики прибора могут быть сдержаны из-за больших емкостей перехода.

Рисунок 8 – Поперечное сечение КМОП-инвертора и эквивалентная схема тиристора

Чтобы решить эту проблему, было предложено несколько способов, таких как p<sup>+</sup>- или n<sup>+</sup>-скрытые слои под карманами, использование имплантации в карманы бора с высокой дозой и высокой энергией и шунтирующее сопротивление для переходов эмиттер — база паразитных биполярных транзисторов. Также будет эффективно обеспечить много контактов к карману, чтобы стабилизировать потенциал кармана и, следовательно, подавить защелкивание. Также может использоваться подложка с p-эпитаксиальным кремнием на p<sup>+</sup>-подложке, чтобы стабилизировать потенциал для быстродействующих логических ИМС.

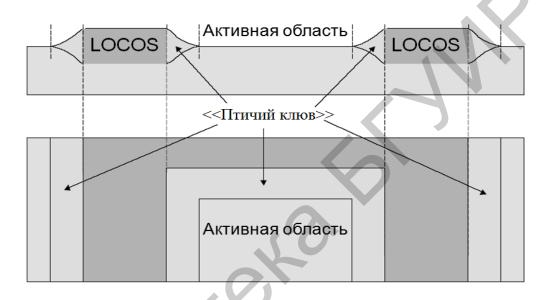

#### 2.2 Изоляция

Локальное окисление кремния (LOCOS) — широко используемая технология изоляции, поскольку она может позволить формирование охранных колец, самосовмещенных с активной областью транзистора. Она также имеет преимущество в виде углубления защитного слоя оксида приблизительно наполовину ниже поверхности кремния, что делает поверхность более планарной.

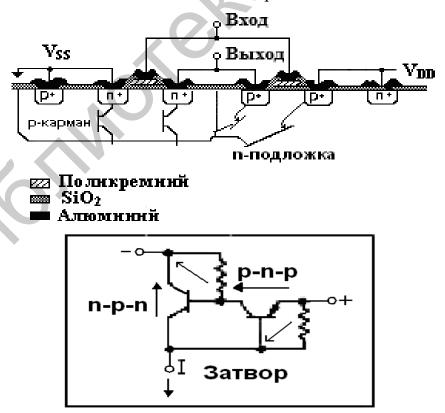

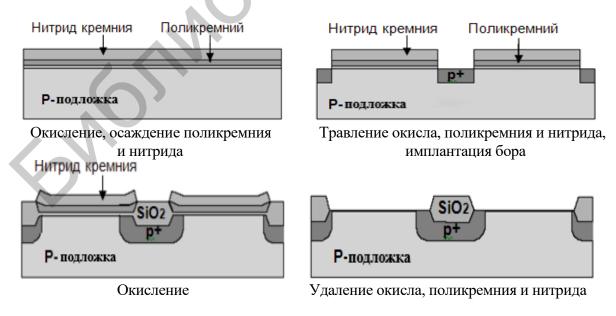

На рисунке 9 показан процесс изоляции LOCOS. Вначале нитрид кремния и промежуточный окисел вытравливаются для определения активной области транзистора. После имплантации для создания канала, как показано на рисунке 9, в, селективно наращивается защитный слой окисла типично до толщины нескольких сотен нанометров.

Недостатком LOCOS является то, что участие азота в маскировании слоя нитрида кремния иногда вызывает формирование очень тонкого слоя нитрида в активной области, и это часто препятствует дальнейшему выращиванию подзатворного оксида, таким образом вызывая низкое пробивное напряжение оксида. Чтобы решить эту проблему, после снятия маскирующего нитрида кремния выращивается оксид, который затем удаляется перед процессом оксидирования затвора.

Рисунок 9 – Процесс локального окисления кремния

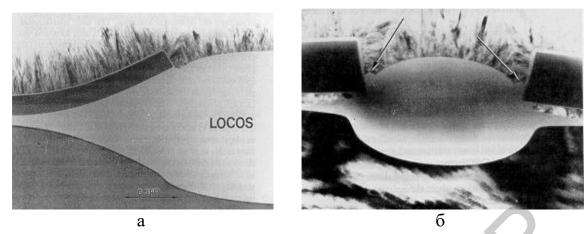

Кроме того, боковое распространение защитного слоя оксида «птичий клюв» ставит проблему уменьшения расстояния между активными транзисторными областями, чтобы реализовать высокую плотность упаковки (рисунок 10). Это боковое распространение подавляется увеличением толщины нитрида кремния или уменьшением толщины промежуточного оксида. Однако это компромисс с генерацией дислокаций в кремнии. Лучшее решение этой проблемы — использование многослойного маскирующего покрытия: оксид — поликремний — нитрид кремния (рисунок 11). Как показано на рисунке 12, поликремний уменьшает механические напряжения, возникающие на границе оксид — кремний, и не дает распространяться «птичьему клюву».

Рисунок 10 – Боковое распространение защитного слоя окисла

Рисунок 11 – Процесс локального окисления кремния многослойным маскирующим покрытием

а — маскирующее покрытие: оксид — нитрид кремния; б — маскирующее покрытие: оксид — поликремний — нитрид кремния Рисунок 12 — Структура с защитным локальным слоем окисла

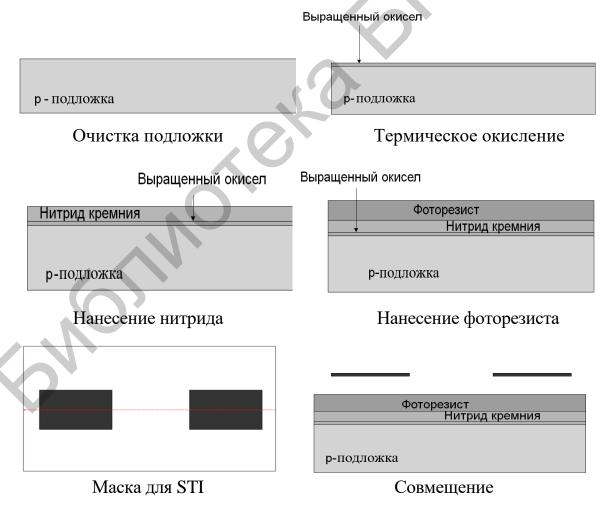

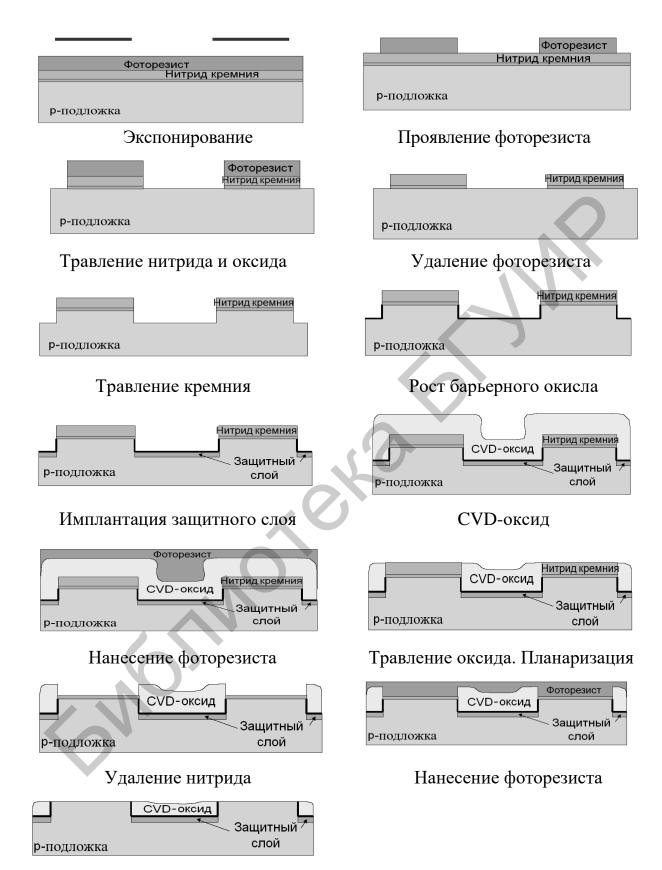

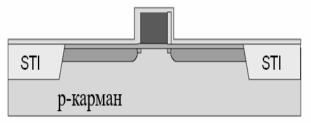

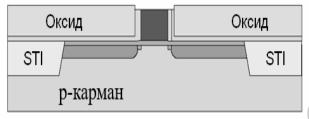

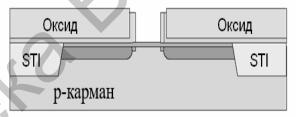

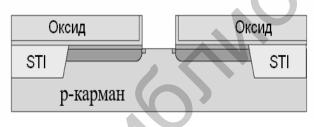

В последнее время изоляция неглубокими канавками (shallow-trench isolation, STI) стала основной технологией изоляции для КМОП-транзисторов. На рисунке 13 показан технологический маршрут STI.

Рисунок 13 – Технологический маршрут STI (продолжение см. на с. 15)

Травление оксида

Рисунок 13 – Окончание (начало см. на с. 14)

После создания канавки в подложке методом реактивного ионного травления (RIE) канавка заполняется изолятором, например диоксидом кремния. В заключение с помощью химико-механической полировки (СМР), обеспечивающей планаризацию, наполнитель с активной области транзистора удаляется. Метод изоляции неглубокими канавками не только сокращает расстояния между активными областями, но также уменьшает площадь активных областей. Тем не менее при создании изоляции остается проблема с механическими напряжениями, поэтому продолжаются работы по совершенствованию метода.

### 2.3 Легирование канала

Чтобы пороговое напряжение обоих типов транзисторов находилось примерно на одном и том же уровне (ниже 1 В), выполняют регулировку порогового напряжения путем подлегирования области каналов (рисунок 14). Это требование обеспечивает функционирование КМОП-схем при низких уровнях напряжений ( $V_{DD}>V_{Tn}+|V_{Tp}|$ ) и более высокий уровень тока стока при больших значениях  $V_{DD}$ . Однако для выполнения отмеченных условий необходимо провести соответствующую регулировку параметров схемы.

Рисунок 14 – КМОП-структура с подлегированием области каналов

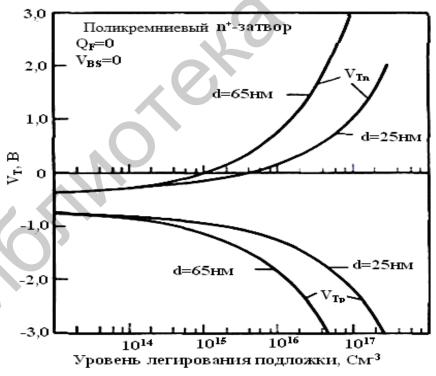

Если в разных типах приборов для затвора используется один и тот же материал (например,  $n^+$ -поликремний), то разность работ выхода электронов  $\phi_{MS}$  будет отличаться для n- и p-канальных транзисторов. Такая разница приводит к асимметрии пороговых напряжений обоих типов транзисторов. На рисунке 15 показаны расчетные значения величин пороговых напряжений n- и p-канальных приборов в зависимости от уровня легирования подложки, на которой они сформированы. Отметим, что невозможно получить  $|V_{Tp}| \le 0,7$  В только за счет уменьшения уровня легирования канала для p-канальных транзисторов, в то время как для n-канальных приборов можно достичь выполнения соотношения  $V_{Tn} \le 0,7$  В путем подбора уровня легирования подложки в области канала.

Для того чтобы обеспечить необходимую величину порогового напряжения p-канальных транзисторов с поликремниевым  $n^+$ -затвором, осуществляют неглубокую ионную имплантацию бора в область канала p-канальных прибо-

ров. В случае имплантации бора нижние кривые на рисунке 15 сдвигаются к более положительным значениям. Эта же доза ионов бора может быть также имплантирована в область канала n-канальных приборов для того, чтобы увеличить значение  $V_{Tn}$ .

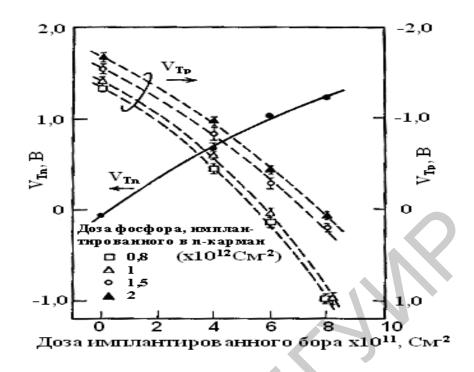

При соответствующем выборе уровня легирования p- и n-областей, в которых происходит формирование приборов, можно использовать только один неселективный процесс ионной имплантации бора для управления величиной порогового напряжения каждого из типов приборов. Этот метод проиллюстрирован на рисунке 16, где приведен график зависимости пороговых напряжений  $V_{Tp}$  и  $V_{Tn}$  от дозы имплантированных ионов бора для приборов с толщиной подзатворного окисла 65 нм и поликремниевыми  $n^+$ -затворами. Эта КМОПструктура сформирована с использованием n-карманов в подложке с проводимостью p-типа. По мере увеличения дозы имплантированного бора  $V_{Tn}$  также возрастает, поскольку при этом увеличивается поверхностная концентрация примеси в подложке p-типа. Величина  $|V_{Tp}|$  уменьшается главным образом из-за присутствия в области канала отрицательного заряда (ионизированные атомы бора). При более низком уровне имплантированной примеси в n-кармане уменьшение  $|V_{Tp}|$  происходит быстрее с увеличением дозы примеси, имплантируемой для регулирования порогового напряжения.

Рисунок 15 — Расчетные величины пороговых напряжений n-канального  $(V_{Tn})$  и p-канального  $(V_{Tp})$  транзисторов в зависимости от уровня легирования подложки

Рисунок 16 – Зависимость порогового напряжения n- и p-канального транзисторов от дозы имплантированного в область канала бора

Указанная выше процедура подлегирования области канала применима в случае n<sup>+</sup>-поликремниевых затворов. Использование разных материалов для затворов предполагает применение различных методов подлегирования областей каналов двух типов приборов.

# 2.4 Подзатворный диэлектрик

Подзатворный диэлектрик оказывает существенное влияние на параметры КМОП-транзисторов. Обычно в качестве подзатворного диэлектрика используется диоксид кремния (SiO<sub>2</sub>). Формируется он несколькими методами, например сухого окисления  $O_2$  и влажного или парового окисления ( $O_2$ ). Пар образован реакцией  $O_2$  окружающей среды. До последнего времени паровое окисление широко использовалось для формирования подзатворного оксида из-за хорошей управляемости толщины оксида и высокой надежности. Однако с уменьшением размеров МОП-транзисторов возникает ряд проблем. Это — неравномерность пленок по толщине, высокая плотность дефектов пленки, статический заряд и плотность поверхностных состояний на границе раздела диэлектрика и кремния, низкое удельное сопротивление к проникновению бора.

Тонкие (<10 нм) слои  $SiO_2$  можно изготавливать при пониженной температуре, пониженном давлении и в различной газовой среде (разбавленном  $O_2$ ;  $O_2 + H_2$ ; озоне или парах  $H_2O$ ). Оксинитридные диэлектрические слои получают в азотосодержащей газовой среде (например, в среде  $N_2O$  или NO). Метод пирогенного окисления со сбалансированной концентрацией водорода и кислоро-

да позволяет выращивать окисные слои толщиной до 5 нм, которые характеризуются высокой предельной напряженностью электрического поля и высоким значением плотности инжектированного в  $SiO_2$  заряда до пробоя. Использование пониженного давления представляет дополнительную возможность управления скоростью окисления, а оптимизация параметров этого процесса окисления в печи позволяет получать достаточно тонкие подзатворные окисные слои высокого качества.

Особого внимания заслуживает метод быстрой термообработки, который является альтернативным направлением в технологии выращивания тонких диэлектрических слоев. Системы быстрого термического окисления (RTO), использующие галогенные лампы в качестве источника тепла, обеспечивают высокие скорости изменения температуры. С помощью RTO-оборудования можно выращивать достаточно тонкие окисные слои (в диапазоне от 2 до 8 нм) за время, не превышающее 60 с. Кроме того, добавление в реакционную среду  $N_2O$  или NO позволяет выращивать оксинитридные слои. Для того чтобы улучшить воспроизводимость процесса окисления в диапазоне толщин менее  $3,5\,$  нм, необходимо уменьшать концентрацию кислорода и снижать общее давление газовой среды.

Следующим направлением развития технологии выращивания подзатворных диэлектрических слоев является техника быстрого разогрева в печах. Эти системы напоминают обычные печи, но с меньшими размерами загрузочной камеры, что позволяет достигать скорости разогрева 30–50 °С/мин. Это улучшает контроль за составом среды в реакторе и сводит к минимуму продолжительность циклов разогрева и охлаждения. Следовательно, минимизируется рост окисла во время подъема температуры, что благоприятно сказывается на формировании ультратонких окисных слоев.

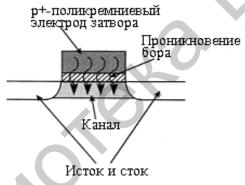

В случае КМОП-структуры со сдвоенным затвором возникает проблема возможного проникновения бора от  $p^+$ -электрода затвора в область канала через диоксид кремния затвора. Чтобы предотвратить эту проблему, в качестве материала диэлектрика затвора используется оксинитрид. Оксинитридный диэлектрик затвора формируется процессом отжига в  $NH_3$ , NO (или  $N_2O$ ) после окисления кремния или прямым оксинитридированием кремния в окружающей среде.

Оксинитридные диэлектрические слои являются основными кандидатами для использования их в качестве подзатворных слоев КМОП ИМС. Оксинитридные слои обеспечивают снижение захвата заряда на ловушки, увеличивают стойкость к воздействию горячих носителей и подавляют диффузию бора из затвора в окисел. Они могут формироваться путем термообработки тонких окисных слоев в атмосфере NH<sub>3</sub>, N<sub>2</sub>O или NO. Термообработка в NH<sub>3</sub> приводит к большой концентрации атомов водорода в образующихся оксинитридных слоях, что в свою очередь вызывает значительное увеличение скорости захвата электронов на ловушки в окисле. Однако это обстоятельство успешно преодолевается путем использования трехступенчатой процедуры, когда сначала RTОметодом выращивается окисный слой, затем с помощью RTN-метода (быстрая термическая обработка в среде, содержащей атомы азота) в среде NH<sub>3</sub> осу-

ществляется нитрирование и в заключение проводится RTO-процесс с целью уменьшения содержания атомов водорода и достижения высокого качества полученного диэлектрика. Термообработка в  $N_2O$  или в NO обеспечивает формирование оксинитридных слоев без введения избыточной концентрации атомов водорода. При этом используется двухступенчатая процедура, когда на первом этапе выращивается тонкий окисный слой, и затем уже осуществляется операция нитрирования путем термообработки в  $N_2O$  или в NO. Кинетика роста оксинитридных слоев в среде  $N_2O$  при RTN-процессе характеризуется наличием сублинейного участка, участка выхода на насыщение и участка насыщения достаточно большой продолжительности.

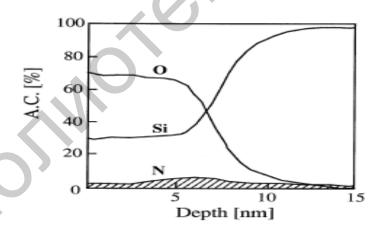

На рисунке 17 показан типичный профиль азота оксинитридного диэлектрика затвора. В последнее время дистанционное плазменное нитридирование было хорошо изучено и сообщается, что оксинитридный диэлектрик затвора, выращенный дистанционным плазменным методом, имеет лучшее качество и надежность, чем выращенный кремниевым методом нитридирования.

В режиме субмикронных КМОП-транзисторов толщина подзатворного оксида приближается к ограничениям по туннельному току приблизительно 3 нм толщиной. Чтобы предотвратить туннельный ток, вместо диоксида кремния предложены материалы с высоким коэффициентом диэлектрической проницаемости (К), например  $Si_3N_4$  и  $Ta_2O_5$ . В этих случаях толщина подзатворного диэлектрика может быть сохранена относительно большой, потому что изолятор с высоким коэффициентом К реализует высокую емкость затвора и, таким образом, лучшую передаточную способность.

Рисунок 17 — Профили распределения концентраций кислорода, азота и кремния оксинитридных диэлектриков затвора, полученные электронной оже-спектроскопией

## 2.5 Электрод затвора

В качестве электродов затвора КМОП-транзисторов широко используется сильнолегированный поликремний. Основное его преимущество – устойчивость при высоких температурах в процессе производства ИМС. Чтобы уменьшить со-

противление электрода затвора, которое вносит значительный вклад в RC-время задержки, на поликремниевый электрод наносят силициды тугоплавких металлов. Технология комбинирования силицида тугоплавкого металла на поверхности легированного поликремния, так называемая полицидная технология, имеет преимущество: сохранение хороших электрических и физических свойств на границе раздела между поликремнием и подзатворным оксидом при значительном уменьшении поверхностного сопротивления слоя электрода затвора.

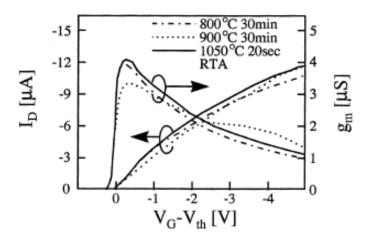

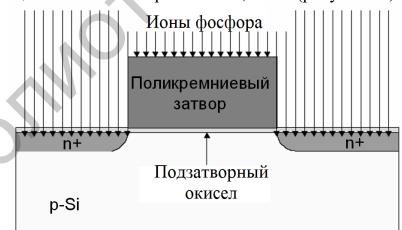

Чтобы легировать поликремний затвора обычно используется ионная имплантация. В случае сильного легирования в процессе высокотемпературной обработки производства ИМС происходит проникновение примеси от легированного бором поликремния к области канала кремниевой подложки через подзатворный оксид, как показано на рисунке 18. С другой стороны, обычно проникновение примеси п-типа (например, фосфора или мышьяка) не происходит. Когда легирование примесей в поликремнии недостаточно, происходит обеднение электрода затвора, как показано на рисунке 19. Это приводит к существенному ухудшению характеристик КМОП-транзистора, связанных с подвижностью (рисунок 20). Чтобы ограничить проникновение бора и обеднение электрода затвора, требуется оптимизация процесса термической обработки.

Рисунок 18 – Проникновение легирующей примеси от легированного бором поликремния к области канала кремниевой подложки

Рисунок 19 — Обеднение электрода затвора при ограниченном легировании поликремния

Рисунок 20 – Характеристики КМОП-транзистора для различных тепловых режимов

Длина затвора — один из самых важных размеров, определяющих рабочие характеристики КМОП-транзисторов; таким образом, процесс литографии для формирования рисунка электрода затвора требует технологии с высокой разрешающей способностью, а для того чтобы разделять поликремний и  $SiO_2$ , требуются высокоселективные процессы реактивного ионного травления (RIE).

## 2.6 Формирование истока, стока

Истоковые и стоковые области формируются с помощью процесса ионной имплантации после получения электрода затвора. Такая последовательность самосовмещает границы областей затвора и истока, стока (рисунок 21).

Рисунок 21 — Формирование областей истока и стока самосовмещением с электродом затвора

Как следствие уменьшения размеров транзисторов, на краю стока (граница раздела области канала и стока), где существует обратно смещенный р-n-переход, наблюдается более высокое электрическое поле. В результате чего носители, проходящие поперек этих переходов, ускоряются, становятся горячими носителями и образуют паразитные токи затвора. Это создает серьезную проблему надежности

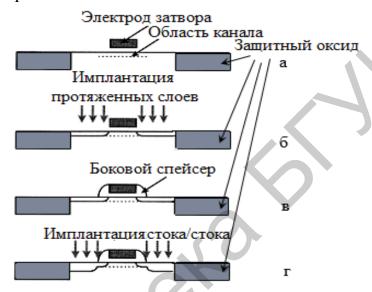

для КМОП-транзисторов. Чтобы предотвратить проблему горячих носителей, предложена структура со слаболегированным стоком (Lightly Doped Drain (LDD)). Технологический маршрут формирования LDD-структуры показан на рисунке 22. После формирования электрода затвора выполняется ионная имплантация, чтобы сделать протяженные слои, и электрод затвора играет роль самосовмещенного шаблона, который покрывает слой канала, как показано на рисунке 22, б. В основном мышьяк легируется для протяженного слоя n-типа n-МОП и  $BF_2$  — для протяженного слоя p-типа МОП-транзистора. Чтобы предотвратить эффект короткого канала, профиль распределения примеси протяженных слоев должен быть очень поверхностным.

а — после формирования электрода затвора; б — имплантация протяженных слоев; в — формирование боковых спейсеров; г — имплантация областей истока и стока

Рисунок 22 – Технологический маршрут LDD-структуры

Хотя протяженные слои могут быть реализованы ионной имплантацией с низкой дозой, удельное сопротивление протяженных слоев становится более высоким и, таким образом, характеристики МОП-транзистора ухудшаются. Следовательно, очень трудно удовлетворить этим двум техническим условиям. Кроме того, диффузия примесей в этих протяженных слоях оказывает значительное влияние на эффект короткого канала. Таким образом, необходимо минимизировать термический процесс после формирования протяженных слоев.

Изоляционная пленка, например  $Si_3N_4$  или  $SiO_2$  осаждается методом CVD. Затем RIE-обработка выполняется на всей подложке. В результате пленка остается только на стороне электрода затвора, как показано на рисунке 22, в. Эту остающуюся пленку называют боковыми спейсерами. Эти спейсеры работают как самосовмещенный шаблон для легирования глубоких областей истока и стока, как показано на рисунке 22, г. Чтобы предотвратить обеднение электрода затвора, области истока, стока n-МОП- и p-МОП-транзисторов легируют мышьяком и  $BF_2$  соответственно. После этого для активации легирующих примесей выполняют

процесс отжига. Наиболее результативным является — быстрый термический отжиг (RTA).

Согласно правилу масштабирования КМОП-транзисторов, когда длина затвора и другие размеры сокращены с коэффициентом k, глубина диффузии также должна быть сокращена как 1/k. Следовательно, глубина диффузии протяженных частей обязана быть особенно малой. Чтобы сформировать мелкозалегающий переход, применяют различные методы: имплантацию с очень низким ускоряющим напряжением, плазменный метод легирования, имплантацию тяжелых молекул (типа  $B_{10}H_{14}$ ). Поскольку вертикальный размер транзисторов уменьшается с уменьшением размеров приборов, наблюдается увеличение поверхностного сопротивления областей истока и стока, поликремниевых пленок, электрода затвора. Это становится серьезной проблемой в быстродействующем режиме работы интегральных схем.

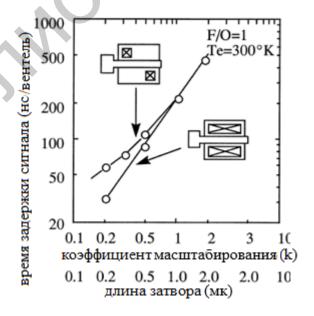

На рисунке 23 показана зависимость времени задержки распространения (t<sub>pd</sub>) КМОП-инверторов от коэффициента масштабирования (k) и длины затвора. Эти результаты были получены моделированием, в котором рассматривались два случая. В первом случае контакты истока и стока с металлической токопроводящей дорожкой были сделаны на краю диффузионных слоев, как проиллюстрировано на рисунке. В реальной топологии ИМС часто случается, что металлический контакт к истоку или стоку может быть сделан только к части диффузионных слоев, так как много других сигналов или шин питания пересекают диффузионные слои. Во втором случае контакты истока и стока покрывают все пространство областей истока и стока, таким образом, уменьшая сопротивление диффузионной линии. Ясно, что без технологии уменьшения сопротивления диффузионной линии значения t<sub>pd</sub> не могут продолжать падать, так как уменьшается размер транзистора; они достигают насыщения при длине затвора приблизительно 0,25 мк.

Рисунок 23 — Зависимость времени задержки распространения сигнала КМОП-инверторов от коэффициента масштабирования и длины затвора

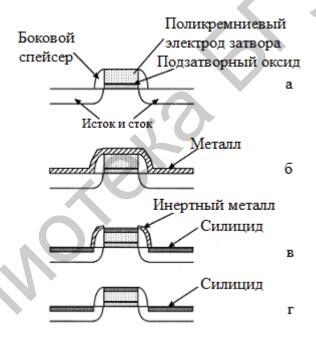

Чтобы решить проблему высокого сопротивления поверхностных диффузионных слоев и тонких поликремниевых пленок, были предложены самосовмещенные силицидные структуры (силицид) для истока, стока и затвора, как показано на рисунке 24. Сначала, после формирования поликремниевого электрода затвора, боковой стенки затвора и диффузионных слоев истока и стока на поверхность МОП-транзистора осаждается металлическая пленка типа Ті или Со, как показано на рисунке 24, б. Затем пленка отжигается быстрым термическим отжигом (RTA) в инертной среде. Во время процесса отжига участки металлической пленки, находящиеся в прямом контакте с кремниевым слоем, то есть истоком, стоком и электродом затвора, селективно преобразуются в силицид, а другие участки остаются металлическими, как показано на рисунке 24, в. Остающийся металл может быть вытравлен с помощью раствора кислоты, например  $H_2O_2 + H_2SO_4$ , оставляя силицид, самосовмещенный с истоком, стоком и электродом затвора, как показано на рисунке 24, г.

а – формирование МОП-транзистора; б – металлизация; в – силицидация термическим отжигом; г – удаление инертного металла Рисунок 24 – Последовательность изготовления МОП-структуры по силицидной технологии

# 3 ЗАКЛЮЧИТЕЛЬНЫЙ ЭТАП ФОРМИРОВАНИЯ КМОП-ТРАНЗИСТОРОВ

### 3.1 Металлизация на основе пленок алюминия

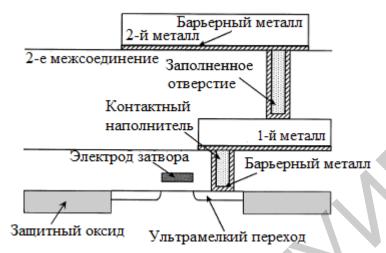

При формировании межсоединений ИМС используют многослойные и многоуровневые системы металлизации. По функциональному признаку к основным слоям многоуровневой металлизации можно отнести: контактные, диффузионно-барьерные и проводящие слои. В многоуровневой металлизации проводящие слои должны быть разделены диэлектриком.

Контактный слой — первый по отношению к полупроводнику (кремнию) слой, являющийся наиболее ответственным в системе металлизации в плане создания приборов с заданными электрическими и надежностными характеристиками. К материалам контактных слоев предъявляется комплекс требований по обеспечению номинальных электрических и физико-технологических параметров, в том числе низкое удельное сопротивление, высокая термическая стабильность, простота формирования заданного рисунка, минимальное проникновение в зону р-п-перехода. С точки зрения возможности одновременного удовлетворения всем указанным требованиям в качестве материала контактных слоев наиболее приемлемы силициды переходных металлов (PtSi, TiSi2, CoSi2 и NiSi).

Проводящий слой — последний по отношению к активной области полупроводникового прибора и очередности нанесения слой, призванный обеспечить высокую электропроводность, устойчивость к электромиграционным процессам при плотностях электрического тока  $10^5 - 10^6$  А/см² и допускающий подсоединение внешних проволочных или объемных выводов к контактным площадкам известными методами. В условиях постоянного уменьшения размеров элементов ИМС выбор материала проводящего слоя ограничивается очень небольшим кругом прежде всего по электропроводности: алюминий (2,65 мкОм·см), золото (2,25 мкОм·см), медь (1,68 мкОм·см) и серебро (1,5 мкОм·см).

Диффузионно-барьерный слой — промежуточный слой между контактным и проводящим слоями, предназначенный для предотвращения нежелательного вза-имодействия между материалами этих слоев. Известными материалами диффузионно-барьерных слоев являются тугоплавкие металлы (Ti, W), сплавы тугоплавких металлов (Ti–W, Ti–W–N, Ta–Si–N, Ti–Si–N), химические соединения тугоплавких металлов (нитриды, карбиды).

Алюминий широко используется в качестве проводящего металла для межсоединений ИМС. Алюминий имеет низкую величину удельного сопротивления при комнатной температуре, а значение этого параметра для его сплавов удовлетворяет требованию низкого сопротивления контакта. Алюминий и его сплавы обладают хорошей адгезией к термическому SiO<sub>2</sub> и осажденным силикатным стеклам. Несмотря на эти преимущества, использование алюминия при изготовлении ИС, обладающих мелкими переходами, часто сталкивается с трудностями, связанными с электромиграцией и коррозией.

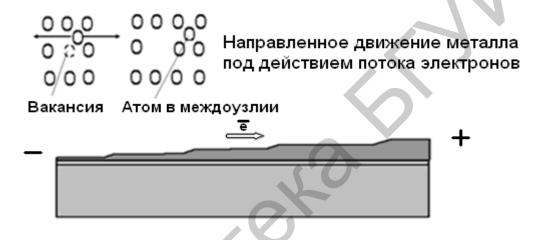

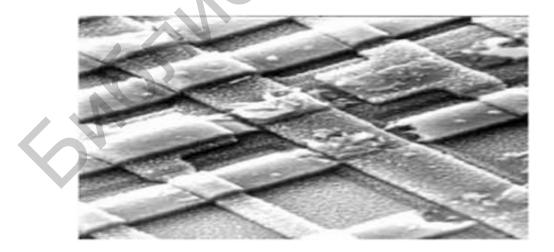

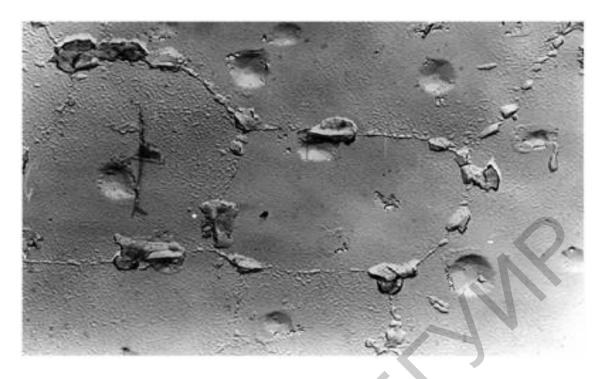

Электромиграция — это явление перемещения ионов металла по направлению электронного потока проводимости, то есть в сторону положительного потенциала, наблюдаемое при больших плотностях электрического тока (рисунок 25). Ионы алюминия увлекаются электронным потоком и образуют у положительного конца полупроводника «усы» и холмики. Около отрицательного конца проводника образуются пустоты, что может приводить к разрыву металлической дорожки и отказу микросхемы в целом. На рисунке 26 показаны обрывы межсоединений на кристалле. Электромиграция наиболее вероятна по границе зерен, то есть чем больше размер зерна, тем меньше электромиграция.

Чтобы уменьшить электромиграцию, в пленки алюминия вводят примесь Cu, Si в количествах, не превышающих 1-2 %. Примесь, располагаясь преимущественно по границам зерен, является стопором при их перемещении (рисунок 27).

Рисунок 25 – Процесс электромиграции

Рисунок 26 — Разрушение межсоединений в результате электромиграции

Рисунок 27 – Микрорельеф поверхности Si на границе раздела Si–Al (1 % Cu)

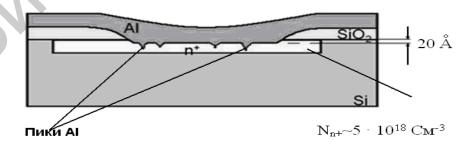

Для получения стабильного низкоомного контакта и улучшения адгезии алюминия к подложке проводят термообработку алюминия в атмосфере инертного газа в течение нескольких минут при  $T = 500-550\,^{\circ}\mathrm{C}$ . Эта температура ниже температуры затвердевания системы Si–Al, поэтому жидкой фазы не образуется. Термообработка в процессе или после нанесения металла имеет целью растворить приповерхностный загрязненный слой кремния в контактном окне, что на практике всегда обеспечивает улучшение характеристик контакта. Другая причина, по которой нельзя избежать термообработки, заключается в том, что термообработка, в результате которой вероятно возникновение проплавлений, требуется также на последующих операциях технологического процесса, уже не связанных с формированием металлизации. При термообработке происходит растворение кремния в алюминии, и в результате этого приповерхностный слой кремния оказывается легирован алюминием, концентрация последнего составляет около  $5\cdot10^{18}\,\mathrm{cm}^{-3}$  (рисунок 28).

Рисунок 28 – Дефекты омического контакта после термообработки пленок алюминия

Поскольку алюминий является акцептором по отношению к кремнию, то при создании омических контактов к кремнию n-типа может возникнуть p-n-переход, и тогда контакт окажется не омическим, а выпрямляющим. Действительно, если концентрация доноров в n-слое меньше  $5\cdot10^{18}$  см<sup>-3</sup>, то атомы алюминия создадут в нем приповерхностный p-слой. Чтобы это исключить, область n-слоя вблизи контакта сильно легируют, превращая ее в n<sup>+</sup>-слой с концентрацией доноров  $10^{20}$  см<sup>-3</sup> и более. Тогда концентрация алюминия оказывается недостаточной для образования p-слоя, и p-n-переход не образовывается.

Если п-слой с самого начала сильно легирован (например, эмиттерный слой транзистора), то дополнительное легирование не требуется. Не возникает проблем и при контакте алюминия с р-слоями, так как растворение в них алюминия приводит к образованию приповерхностных р<sup>+</sup>-слоев, что способствует повреждению качества омического контакта.

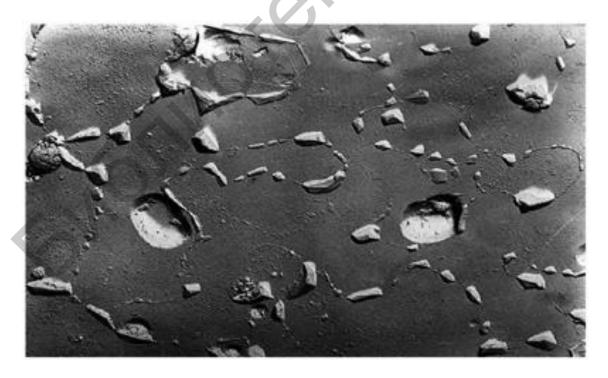

Часто при термообработке алюминия отдельные участки кремния с повышенной поверхностной энергией растворяются в алюминии быстрее, что приводит к образованию локальных ямок, заполняемых впоследствии алюминием (рисунок 29). Глубина и плотность образующихся ямок зависят от режимов термообработки. Наличие таких ямок может приводить к закорачиванию п-р-эмиттерных переходов, когда глубина их залегания небольшая. Для получения малопроникающих контактов в алюминий вводят около 2 % кремния. Присутствие кремния в пленках алюминия сдерживает процесс растворения кремния при термообработке и уменьшает вероятность образования глубоких локальных ямок.

Рисунок 29 – Ямки травления алюминия на границе раздела Si–Al в области омического контакта

На рисунке 30 показан разрез структуры многоуровневой металлизации с применением барьерного слоя и контактным наполнителем.

Рисунок 30 – Вид в разрезе многоуровневой металлизации

Алюминий и его сплавы используются как основной межсоединительный материал для формирования металлизации КМОП ИМС, который отвечает большинству технических требований, предъявляемых к материалу металлизации ИМС с размерами элементов более 0,25 мкм. Однако для металлизации ИМС с проектными нормами менее 0,25 мкм применение алюминия становится проблематичным из-за больших ограничений, связанных со свойствами металла и технологией его осаждения. Одной из наиболее важных проблем при использовании алюминиевой металлизации, как было уже сказано, становятся деградационные процессы, обусловленные электромиграцией и вызывающие катастрофические отказы в межсоединениях. В случае ЭТОМ перспективным альтернативным решением является использование меди в качестве материала межсоединений КМОП ИМС.

#### 3.2 Металлизация на основе пленок меди

Медь – ключевой материал в следующем поколении металлизации ИМС. Основным преимуществом меди по сравнению с алюминием является более низкое электрическое сопротивление, стойкость к электромиграции, увеличение скорости переключения элементов ИМС. С уменьшением элементов ИМС до субмикронных размеров скорость переключения становится все более и более ограниченной задержкой времени RC-межсоединений. В этом смысле медь является материалом с большими возможностями для многоуровневой металлизации ИМС, так как та же самая скорость может быть сохранена при использовании медной линии более узкой или тонкой, чем алюминиевая.

Медная металлизация уже признана ведущими фирмами-изготовителями ИМС как процесс, способный обеспечить изготовление ИМС с многоуровневой

системой межсоединений с шириной линии менее 0,5 мкм. Однако существует ряд проблем широкого применения медной металлизации.

Одним из препятствий для использования меди в линиях межсоединений ИМС является процесс формирования топологического рисунка. При комнатной температуре медь не образует летучих соединений с плазмой на основе СІ и F. Таким образом, сухое плазменное травление медных пленок затруднено. А химическое травление меди может сопровождаться ее коррозией, так как отсутствие самопассивации делает тонкие медные пленки склонными к окислению во время обработки.

Другая проблема состоит в том, что медь является хорошим диффузантом в Si и  $SiO_2$  и легко реагирует с силицидами. Медь быстро диффундирует в кремний и может формировать центры с высокоэнергетическими уровнями в запрещенной зоне кремния. Эти высокоэнергетические уровни обеспечивают механизм избыточных неосновных носителей, рекомбинирующих с основными носителями. Следовательно, медь будет вызывать генерационнорекомбинационные токи утечки в p-n-переходах и подвергать опасности надежность МОП-транзисторов.

Это препятствие может быть преодолено путем использования диффузионных барьеров и пассивирующих слоев при создании медной металлизации. Для выполнения данной задачи наиболее подходящими материалами являются тугоплавкие металлы и твердые растворы на их основе. Это связано с тем, что температура плавления этой группы металлов превосходит температуру плавления меди, и тугоплавкие металлы обычно неспособны образовывать твердые растворы с медью. С другой стороны, высокая проводимость данных материалов ограничивает влияние диффузионного барьера на процесс распространения электрического сигнала. Снижение влияния барьерного слоя на работу проводящих линий достигается, как правило, за счет уменьшения его сопротивления, что обычно сопровождается ухудшением свойств барьерного слоя. В связи с этим оптимизация состава диффузионного барьера является комплексной задачей, требующей учета ряда факторов, к которым следует также отнести зависимость барьерных свойств от толщины слоя. Это особенно актуально в связи с возрастающей степенью интеграции и уменьшением поперечного сечения контактных окон и токоведущих дорожек, так как в этом случае требуется учитывать возможности методов осаждения барьерных слоев.

Относительно низкие температуры реакций поверхностей раздела медь — металл стимулируют исследования проблемы эффективности диффузионных барьеров и термической стабильности медной металлизации.

Формирование медных межсоединений методом двойной гравировки. Препятствия формирования медных межсоединений, о которых сказано выше сдерживали применение данного металла в массовом производстве. Положение изменилось тогда, когда корпорация IBM и компания Motorola объявили о том, что каждая из них, независимо друг от друга, разработали технологию производства кристаллов ИМС с шестью уровнями разводки. Препятствия были пре-

одолены с помощью двухстадийного, так называемого процесса двойной гравировки (dual-damascene process).

Носящий название «гравировки» метод включает формирование шин межсоединений путем первоначального травления канавок или каналов в планарном диэлектрическом слое и последующее заполнение этих канавок металлом.

В методе «двойной гравировки» задействован второй уровень, в котором помимо формирования канавок травится и заполняется ряд отверстий (то есть контактов к активным областям или к металлу). После заполнения металл и диэлектрик планаризируются с помощью химико-механической полировки (ХМП).

Основным достоинством процесса гравировки является исключение необходимости травления металла. Оно приобретает все большее значение по мере перехода полупроводниковой промышленности от алюминия к меди, поскольку травление меди связано с чрезмерно большими трудностями. Второе достоинство процесса гравировки заключается в исключении необходимости заполнения зазоров в диэлектрике между шинами разводки. Травление металла и заполнение канавок в диэлектрике представляют собой две самые большие проблемы для полупроводниковой отрасли в ее движении в сторону меньших размеров. Третье достоинство процесса гравировки состоит в том, что он позволяет обойти некоторые проблемы, связанные с неточностью совмещения фотолитографических слоев, позволяя получать более высокую плотность межсоединений.

Медь, обладающая меньшим удельным сопротивлением, чем алюминий, не является единственным материалом среди тех, на которые предстоит перейти в будущем полупроводниковой промышленности. Чтобы дополнительно уменьшить временные задержки и увеличить скорость работы кристаллов ИМС, также переходят на диэлектрики с низкой диэлектрической постоянной (k).

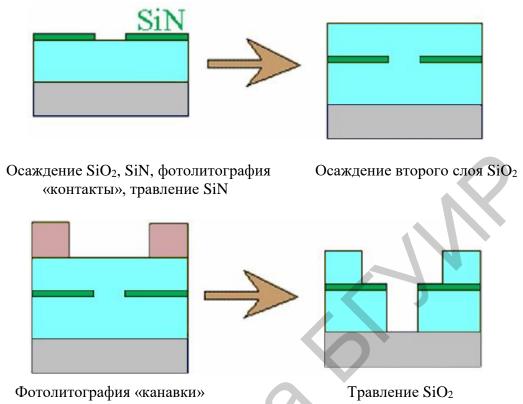

На рисунке 31 показана последовательность технологических операций двойной гравировки с использованием стоп-слоя. Отличительной чертой данного технологического варианта является применение очень тонкого слоя нитрида кремния, который действует в качестве жесткой маски. Здесь слой нитрида кремния, толщина которого может достигать 25 нм, осаждается сверху на диэлектрик, и затем в нем формируется топологический рисунок для создания отверстий межуровневых контактов. Затем осаждается второй уровень диэлектрика сверху нитрида кремния. После этого формируется топологический рисунок канавок и травится в верхнем уровне диэлектрика до стоп-слоя нитрида кремния. Однако травление продолжается далее через отверстие в нитриде, формируя тем самым межуровневые отверстия. На последней стадии канавки и межуровневые контакты заполняются металлом. Заметим, что на рисунке показана канавка намного шире межуровневого отверстия, но в действительности они имеют практически одинаковый размер. Основным преимуществом данного технологического маршрута формирования межсоединений является то, что

в нем присутствует всего одна операция травления и одна операция заполнения углублений металлом.

Рисунок 31 — Последовательность процесса двойной гравировки с использованием стоп-слоя

Медь, обладающая меньшим удельным сопротивлением, чем алюминий, не является единственным материалом среди тех, на которые предстоит перейти в будущем полупроводниковой промышленности. Чтобы дополнительно уменьшить временные задержки и увеличить скорость работы кристаллов ИМС, также переходят на диэлектрики с низкой диэлектрической постоянной.

Методы осаждения пленок меди. Медь может быть осаждена PVD, CVD, электролизным осаждением и электроосаждением. Такие методы осаждения, как электролизное осаждение и электроосаждение, имеют преимущества — низкую стоимость оборудования и низкую температуру процесса, а также высокое качество осадков и хорошую способность заполнения отверстий между слоями-канавками. Однако для электроосаждения требуется внешний источник тока, однородный сплошной толстый слой-затравка и низкорезистивный контакт к слою-затравке. Более того, электрическая однородность электроосажденных пленок и способность заполнения отверстий между слоями и канавок зависит от распределения тока. Электроосаждение имеет также более низкую производительность по сравнению с процессом кассетного электролизного осаждения. Метод электролизного осаждения особенно привлекателен из-за низкой стоимости, присущей селективности, высокого качества электролизных Си-пленок, осажденных на очень тонкие слои-затравки (< 10 нм), и хорошей способности

заполнения отверстий между слоями. Очень узкие дорожки — до 100 нм шириной — также изготавливали селективным электролизным осаждением. Применение литографических процессов для медных пленок затруднено из-за сложности их травления. Анизотропное сухое травление для получения мелких элементов в меди не является тривиальным. Так как хлориды и флуориды меди не очень летучи при комнатной температуре, температура подложки должна быть поднята до довольно высоких температур (> 150–250 °C) во время травления. Это усложняет формирование маскирующего слоя. Также химия сухого травления может быть причиной коррозии меди. Как альтернатива сухому травлению селективное осаждение может быть использовано для формирования дорожек. Есть несколько критических требований, которые должны быть решены, чтобы электролизное осаждение меди могло стать общей технологией металлизации ИМС.

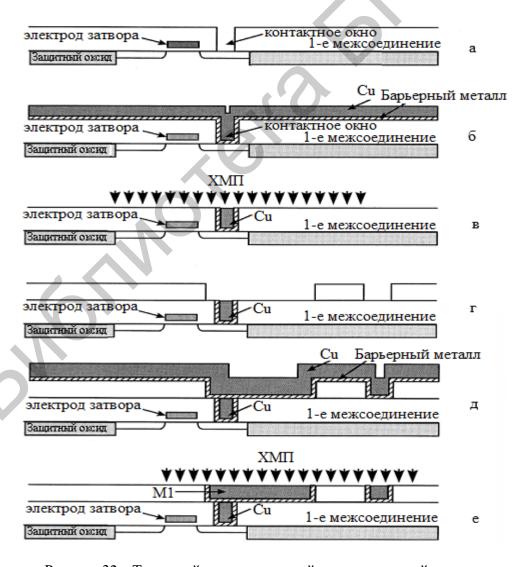

*Технологический процесс формирования медной металлизации*. На рисунке 32 показан технологический маршрут формирования двухуровневой медной металлизации.

Рисунок 32 – Типичный технологический маршрут медной металлизации

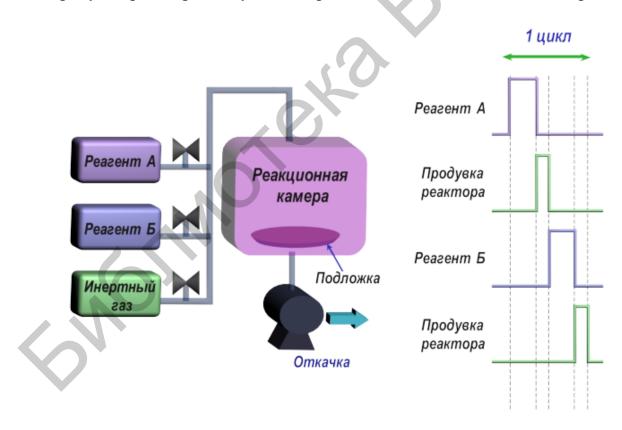

Для создания металлизации был использован метод «двойной гравировки» со стоп-слоем. Первым этапом при создании медной металлизации является создание слоя диэлектрика на подложке. Затем следует процесс нанесения стопслоя, который служит для остановки процесса травления. Следующим процессом является нанесение второго слоя диэлектрика. Слои диэлектрика необходимы для избежания процессов травления меди, что является одной из основных проблем при использовании медной металлизации.

Следующим этапом является формирование сквозных межсоединений. Для этого проводят фотолитографию, вскрывают окна в фоторезисте и проводят процесс травления в диэлектрике сквозных межсоединений. Травление завершается на стоп-слое. Затем производят следующую фотолитографию для травления канавок. После экспонирования и проявления фоторезиста начинают травление стоп-слоя в области сквозных межсоединений, а также первого (в области сквозных межсоединений) и второго слоя диэлектрика (металлические канавки). После операции травления производят удаление фоторезиста.

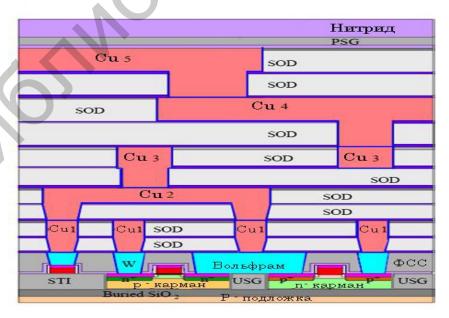

После этапа формирования сквозных межсоединений и канавок следует этап заполнения их медью. Перед осаждением меди необходимо создать барьерный слой, чтобы избежать процесс диффузии меди в кремний, что тоже является проблемой медной металлизации. После создания барьерного слоя с помощью электролизного метода осаждения создают затравочный слой меди для лучшей адгезии основного слоя меди с барьерным слоем, а также для лучшей однородности пленки. Далее электрохимическим методом производят осаждение меди по всей площади пластины. Затем проводят процесс химикомеханической полировки кристалла. В результате получают встроенные металлические соединения. На рисунке 33 показано сечение КМОП-структуры с пятиуровневой металлизацией, изготовленной на основе пленок меди.

Рисунок 33 — Сечение КМОП-структуры с металлизацией, изготовленной на основе пленок меди

## 3.3 Планаризация рельефа

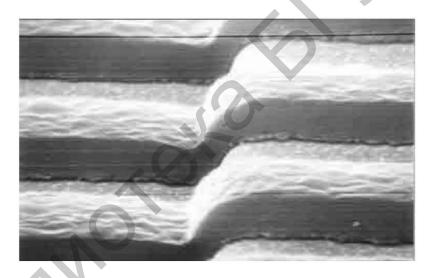

Одной из проблем при создании многоуровневой металлизации ИМС является планаризация межуровневого диэлектрика. С ростом степени интеграции ИМС резко повышаются требования к планарности поверхности полупроводниковых структур на всех стадиях технологического маршрута изготовления микросхем. Дело в том, что на рельефной поверхности затруднено проведение литографических процессов с требуемой точностью воспроизведения геометрических размеров формируемых рисунков, так как глубина фокуса современных проекционных систем близка или даже меньше, чем возможная высота рельефа на полупроводниковой структуре. Рост количества слоев межуровневой разводки приводит к тому, что если не предпринимать специальных мер, то, начиная со второго слоя, становится проблематичным проводить литографический процесс и формировать следующий слой разводки. На рисунке 34 показан рельеф поверхности кристалла после формирования первого уровня металлизации.

Рисунок 34 — Рельеф поверхности кристалла после формирования первого уровня металлизации

Для преодоления данной проблемы была разработана специальная процедура — планаризация рельефа. Планаризация — это процесс, используемый при изготовлении ИМС и предназначенный для уменьшения перепада высоты между низшими и высшими точками рельефа на полупроводниковой пластине вплоть до получения полностью плоской поверхности по всей ее площади.

Известно достаточно большое количество методов планаризации рельефа. Среди наиболее популярных из них следует назвать следующие:

- планаризация оплавлением бор-фосфорно-силикатного стекла;

- планаризация травлением жертвенного слоя (обычно резиста);

- планаризация селективным химическим осаждением вольфрама из газовой фазы;

- планаризация с помощью химико-механической полировки.

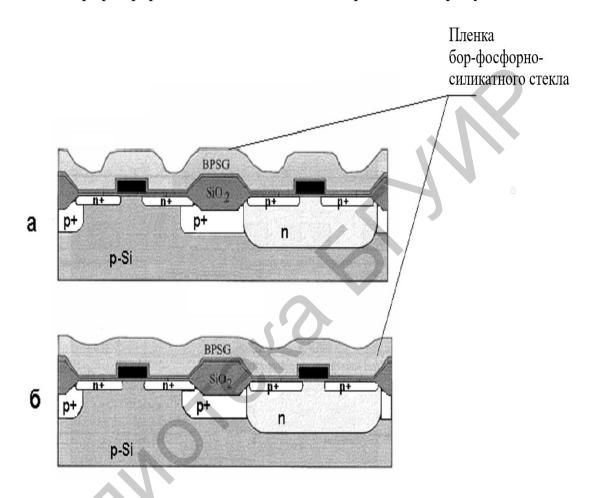

Применение в качестве межслоевого диэлектрика пленки легкоплавкого бор-фосфорно-силикатного стекла позволяет планаризовать поверхность полупроводниковой структуры посредством ее термообработки, выполняемой после осаждения пленки на развитый рельеф. Нагрев приводит к размягчению стекла, его вязкому течению и выравниванию рельефа. Пример планаризации с помощью оплавления бор-фосфорно-силикатного стекла приведен на рисунке 35.

а – до планаризации; б – после планаризации Рисунок 35 – Планаризация полупроводниковой структуры с помощью оплавления слоя бор-фосфорно-силикатного стекла

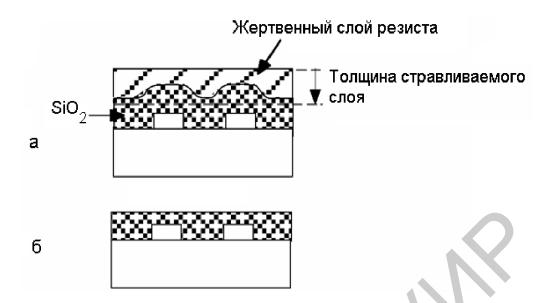

Планаризация травлением жертвенного слоя резиста представлена на рисунке 36. Особенность метода заключается в том, что сглаживание рельефа достигается за счет равенства скоростей травления резиста и межуровневого диэлектрика. На кристалл наносится слой резиста такой толщины, чтобы его поверхность получалась практически ровной и покрывала все выступы рельефа, затем поверхность структуры подвергается травлению вплоть до полного удаления резиста из наиболее «низких» мест. После нанесения резиста его толщина по площади пластины различна, в результате травление лежащих под резистом «высоких» областей начинается раньше, чем травление «низких», что и ведет к планаризации рельефа.

а – до планаризации; б – после планаризации Рисунок 36 – Планаризация полупроводниковой структуры травлением жертвенного слоя резиста

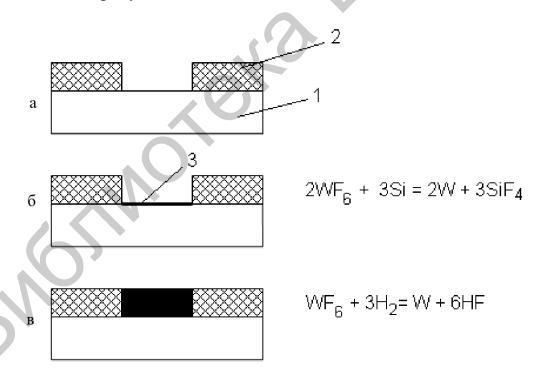

Планаризация селективным химическим осаждением вольфрама из газовой фазы показана на рисунке 37.

а — до планаризации; б — начальная стадия осаждения W; в — после планаризации Рисунок 37 — Планаризация полупроводниковой структуры селективным химическим осаждением вольфрама из газовой фазы ( $WF_6$ ), производимая в окна  $SiO_2$

Методы являются универсальными и применяются как при формировании межуровневых слоев металлизации, так и при создании контактов к полупроводниковым структурам на начальном этапе металлизации ИМС. Суть ме-

тода заключается в том, что сглаживание рельефа достигается путем предварительного заполнения контактных окон вольфрамом, химически осажденным из газовой фазы. На первом этапе в пленке окиси кремния вскрываются окна до поверхности кремния. Затем в контактные окна осаждается вольфрам и в результате происходит селективное заращивание окон.

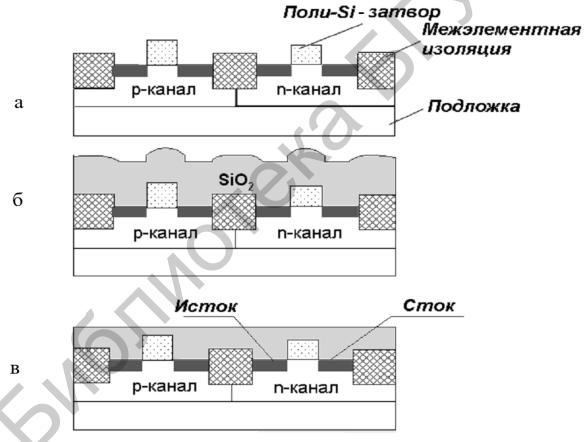

Рассмотренные выше методы используются в основном при изготовлении ИМС с двумя-тремя уровнями металлизации. При изготовлении современных ИМС для планаризации используется метод — химико-механическая полировка (chemical-mechanical polishing, CMP). Химико-механическая полировка, или планаризация (ХМП), — это процесс удаления материала с исходной рельефной поверхности полупроводниковой структуры, выполняемый при одновременном воздействии как абразива, так и химических реагентов, приводящий к утончению полируемого слоя и получению плоской поверхности. На рисунке 38 показан пример планаризации слоя межуровневого диэлектрика, осажденного на поверхность полупроводниковой кремниевой структуры.

а – структура со сформированными транзисторами; б – структура с осажденным слоем межуровневого диэлектрика; в – планаризированная структура

Рисунок 38 — Планаризация слоя межуровневого диэлектрика, осажденного на поверхность полупроводниковой кремниевой структуры

XMП выполняется для пленок межуровневых диэлектриков, для слоев металлов межуровневой и межэлементной разводки, формируемых по дамас-

скому или двойному дамасскому процессу при формировании металлизации на основе пленок меди. Высота рельефа, которая получается при конформном осаждении тонкой пленки на поверхность предыдущего слоя с уже сформированном слое. В тех местах, где размер окон в плоскости подложки много больше толщины пленки, при нанесении последующего слоя получаемый рельеф практически повторяет исходный рельеф. Однако в тех местах, где размер окна меньше или сравним с толщиной пленки, высота рельефа после нанесения последующего слоя становится меньше ее исходной величины. В результате топография рельефа до и после осаждения слоя может достаточно сильно отличаться. Идеальную топографию поверхности (плоская поверхность по всей площади пластины) можно получить только с помощью химико-механической полировки.

Технология химико-механической планаризации включает в себя последовательность нескольких операций. Первой выполняется непосредственно сама полировка, затем проводится отмывка отполированной пластины от остатков суспензии и продуктов полировки и после этого производится контроль качества выполнения операции планаризации и операции очистки поверхности. При XMП одновременно протекает два процесса: химическая реакция между активным реагентом, содержащимся в суспензии, и материалом планаризируемого слоя, а также механическое удаление продуктов реакции и материала планаризируемого слоя абразивными частицами, взвешенными в суспензии. Наличие в суспензии химически активных реагентов приводит к «размягчению» приповерхностного слоя, в результате чего облегчается его механическое удаление абразивом и увеличивается скорость и качество полировки. Состав суспензии и количество процессов ХМП, используемых для планаризации одного слоя, зависят от материала полируемого слоя, а также от толщины слоя, который необходимо удалить, и степени шероховатости поверхности, которую необходимо получить по окончании процесса. Количество процессов ХМП, используемых при изготовлении ИМС, растет с увеличением количества слоев межуровневой разводки.

### 4 КОНСТРУКТИВНО-ТЕХНОЛОГИЧЕСКИЕ ОСОБЕННОСТИ ИЗГОТОВЛЕНИЯ КМОП-ТРАНЗИСТОРОВ

## 4.1 Аномальные эффекты и методы улучшения характеристик КМОП-транзисторов

Каждый технологический шаг в направлении уменьшения размеров КМОП-транзисторов сопряжен с ростом проблем конструирования и производства, которые приходится решать для обеспечения теоретически прогнозируемых характеристик. Любое улучшение одних параметров приводит к ухудшению других, причем с уменьшением размеров взаимное влияние параметров становится все более сильным.

Основными проблемами микроминиатюризации МОП-транзисторов являются туннелирование через затвор, инжекция горячих носителей в окисел, прокол между истоком и стоком, утечки в подпороговой области, уменьшение подвижности носителей в канале, увеличение последовательного сопротивления между истоком и стоком, обеспечение запаса между пороговым напряжением и напряжением питания. Транзистор должен иметь слабую зависимость порогового напряжения от напряжения на стоке, от длины и ширины канала, а также большую передаточную проводимость, большое выходное сопротивление, малое сопротивление областей истока и стока и большую нагрузочную способность. Емкости затвора и р-п-переходов должны быть минимальны. Разброс параметров техпроцесса, который растет с уменьшением размеров транзистора, не должен снижать процент выхода годных кристаллов.

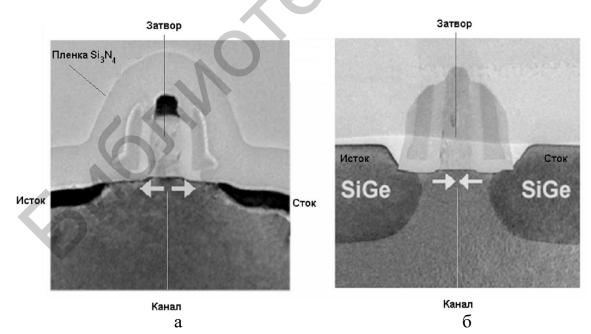

Как было показано в подразделе 2.6, наиболее распространенной конструкцией КМОП-транзистора, используемой в полупроводниковой промышленности, является LDD-структура. Ее особенностью является наличие мелких слаболегированных областей, которые удлиняют области истока и стока в сторону канала. Концентрацию легирующей примеси в этих областях (фосфор и бор) и режим ее разгонки выбирают таким образом, чтобы получить плавный р-п-переход. Обычно концентрация примеси составляет от  $4\cdot10^{18}$  до  $8\cdot10^{18}$  см<sup>-3</sup>, в то время как в  $n^+$ -областях она достигает  $5\cdot10^{19}$ – $1\cdot10^{20}$  см<sup>-3</sup>. Полученное таким способом снижение напряженности электрического поля в канале на границе со стоком уменьшает энергию горячих электронов, которые вызывают долговременную деградацию параметров транзистора. Слаболегированные LDD-области также повышают напряжение прокола, инжекционного и лавинного пробоя транзистора, уменьшают DIBL-эффект и эффект модуляции длины канала.

Для снижения емкостей транзистора выбирают слаболегированную подложку, а для обеспечения необходимого порогового напряжения и снижения напряжения «прокола» применяют легирование канала примесью того же типа, что и в подложке. Легирование выполняют примерно на глубину области пространственного заряда под затвором.

Уменьшение порогового напряжения при снижении длины канала является индикатором появления короткоканальных эффектов при разработке новых

технологий и одновременно существенным препятствием на пути сокращения размеров транзисторных структур. Для борьбы с эффектами короткого канала используется изменение профиля легирующей примеси как в горизонтальном, так и в вертикальном направлении.

Проникновение области обеднения стока в канал является основной причиной появления короткоканальных эффектов. Однако их нельзя устранить путем простого повышения концентрации легирующей примеси в подложке, поскольку при этом растет подпороговый ток и уменьшается подвижность носителей в канале, вызывающая деградацию нагрузочной способности транзистора. Наиболее распространенным решением этой проблемы является реализация так называемого обратного эффекта короткого канала, когда с уменьшением длины канала пороговое напряжение возрастает. Этого можно достичь применением ореола (halo) вокруг областей истока и стока.

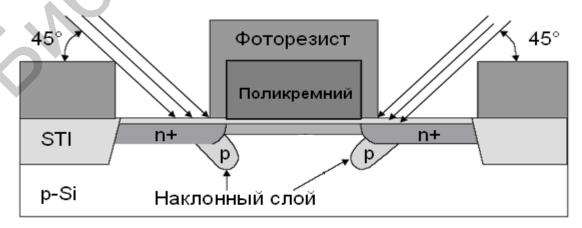

Ореол создается ионным легированием примеси того же типа проводимости, что и карман (бор или индий для п-канального транзистора и мышьяк для р-канального). Индий по сравнению с бором снижает крутизну падения порогового напряжения в зависимости от длины канала и уменьшает разброс наклона подпороговой характеристики. Ионное легирование может выполняться вертикально, но чаще под углом, для чего кремниевую пластину наклоняют на угол от 20–30 до 90° по отношению к ионному пучку, чтобы направить его под затвор. Ореол делают обычно на том же этапе литографии, что и мелкие слаболегированные области истока и стока (рисунок 39).

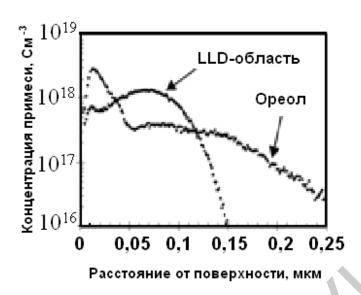

Энергию имплантации при наклонном легировании выбирают достаточно большую, чтобы увеличить глубину залегания ореола. После формирования спейсера во время отжига областей истока и стока имплантант диффундирует за LDD-области, обеспечивая показанный на рисунке 40 профиль распределения примеси. Принцип действия ореола основан на том, что пороговое напряжение МОП-транзистора зависит от средней концентрации примеси под затвором, а не от ее горизонтального распределения. Поэтому введение ореола увеличивает пороговое напряжение, однако практически не влияет на среднюю подвижность носителей в канале.

Рисунок 39 – МОП-структура при наклонном легировании подзатворной области

Рисунок 40 – Профиль примеси в области ореола и слаболегированной (LDD) области истока или стока для 0,25-микрометровой технологии

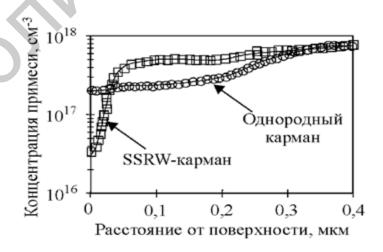

Крутое ретроградное распределение примеси (Super Steep Retrograde Well) (рисунок 41) создается путем медленной диффузии мышьяка или сурьмы для р-канальных приборов и индия для п-канальных. Благодаря возможности устанавливать поверхностную концентрацию легирующей примеси независимо от объемной, появляется дополнительная степень свободы для независимой регулировки порогового напряжения и концентрации примеси в подложке, влияющей на величину области пространственного заряда и, соответственно, короткоканальные эффекты. Правильное применение идеи SSRW позволяет ослабить влияние короткоканальных эффектов и увеличить поверхностную подвижность носителей, однако при этом несколько увеличивается подпороговый ток.

Рисунок 41 — Крутое ретроградное распределение примеси в кармане (SSRW)

Сравнение структур с однородным и ретроградным распределением примеси достаточно неоднозначно из-за сложности выбора условий сравнения и иногда дает противоречивые результаты. Разновидностью крутого ретроградного распределения примеси является дельта-легирование подложки, имеющее аналогичные свойства.

Одним из путей увеличения передаточной проводимости и нагрузочной способности МОП-транзистора является уменьшение толщины подзатворного окисла. Толщина окисла ограничивается появлением паразитного туннельного тока, который увеличивает энергопотребление микросхемы, и нестабильностью напряжения пробоя окисла, снижающей надежность.

Рост туннельного тока через окисел является не единственной преградой на пути уменьшения его толщины. В экспериментах с приборами, имеющими толщину затвора 1,2–2,8 нм, было показано, что с ростом туннельного тока увеличивается статистический разброс порогового напряжения. Это объясняется тем, что пороговое напряжение начинает зависеть от падения напряжения на омическом сопротивлении затвора; падение напряжения вызывается прохождением туннельного тока. При этом в разброс порогового напряжения вносится компонента, связанная с разбросом сопротивления затвора.

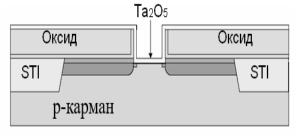

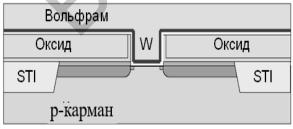

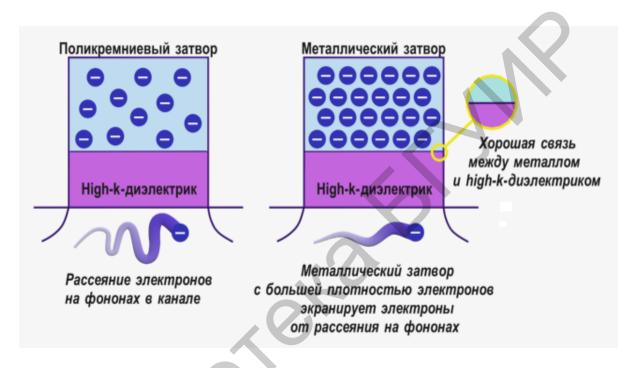

Еще одной причиной, мешающей дальнейшему уменьшению размеров транзисторов, является квантово-механическая природа инверсионного слоя, которая не позволяет электронам располагаться непосредственно у поверхности кремния. Максимум пространственного распределения электронов находится на расстоянии около 1 нм от поверхности. Это увеличивает эффективную толщину окисла примерно на 0,3 нм. Кроме того, вследствие ограниченной концентрации примеси в поликремниевом затворе в нем наступает режим обеднения, из-за которого увеличивается эффективная толщина подзатворного слоя диэлектрика. Общее увеличение эффективной толщины составляет около 0,7 нм, что уменьшает ток стока и нагрузочную способность транзистора. Кроме этого, важной является замена поликремниевого затвора на металлический. На рисунке 42 показан один из вариантов формирования МОП-структуры с металлическим затвором.

В КМОП-транзисторах, имеющих толщину окисла 1,3–1,5 нм, было обнаружено, что туннельный ток через подзатворный диэлектрик может быть существенно уменьшен путем повышения однородности пленки окисла. Однако основной путь, по которому пошли производители КМОП ИС, — использование подзатворного диэлектрика с высокой диэлектрической проницаемостью. Ключевым моментом техпроцесса для длин канала менее 100 нм является получение мелких (менее 20 нм) р-п-переходов. Однако они дают неприемлемо высокое сопротивление областей истока и стока. Для его снижения обычно используют промежуточный слой из TiSi<sub>2</sub> или CoSi<sub>2</sub>.

Формирование слаболегированных областей истока, стока

Формирование бокового окисла

Формирование сильнолегированных областей истока, стока, осаждение  $Si_3N_4$

Осаждение низкотемпературного SiO<sub>2</sub>

Планаризация

Удаление поликремния

Удаление подзатворного SiO<sub>2</sub>

Осаждение Та<sub>2</sub>О<sub>5</sub>

Осаждение W Планаризация

Рисунок 42 — Последовательность формирования МОП-структуры с металлическим затвором

В КМОП-транзисторах, имеющих толщину окисла 1,3–1,5 нм, было обнаружено, что туннельный ток через подзатворный диэлектрик может быть существенно уменьшен путем повышения однородности пленки окисла. Однако основной путь, по которому пошли производители КМОП ИС, — использование подзатворного диэлектрика с высокой диэлектрической проницаемостью. Ключевым моментом техпроцесса для длин канала менее 100 нм является получение мелких (менее 20 нм) р-п-переходов. Однако они дают неприемлемо высокое сопротивление областей истока и стока. Для его снижения обычно используют промежуточный слой из TiSi<sub>2</sub> или CoSi<sub>2</sub>.

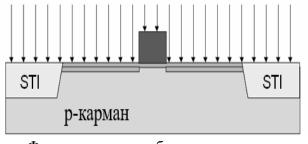

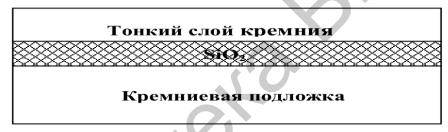

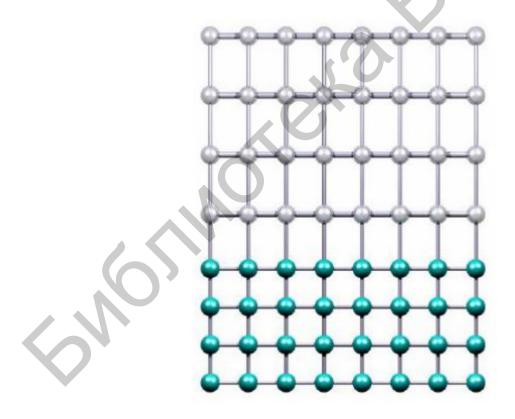

## 4.2 Структура «кремний на изоляторе»

Основное достоинство структур «кремний на изоляторе» (КНИ) заключается в том, что в подложках типа кремний на изоляторе тонкий приповерхностный слой кремния, в котором формируются все элементы ИМС, отсечен от подложки слоем диэлектрика (рисунок 43). В результате предотвращается растекание тока по объему кремния и уменьшается величина тока в выключенном состоянии.

Рисунок 43 – Поперечное сечение структуры «кремний на изоляторе»

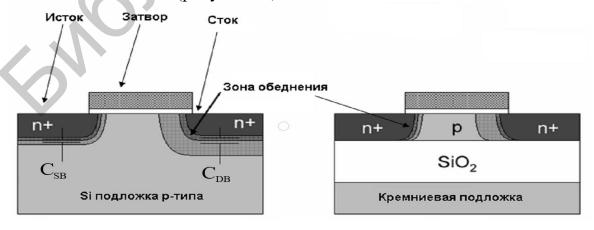

МОП-транзисторы, изготовленные по технологии КНИ, являются весьма перспективными для создания микромощных и высокоскоростных ИМС с напряжением питания до 1,2 В и менее, поскольку наличие толстого окисла вместо кремния под областями истока и стока существенно уменьшает величину емкости на подложке (рисунок 44).

Рисунок 44 – Паразитные емкости стока и истока транзистора, сформированного на «объемном» кремнии и на структуре КНИ

Вторым преимуществом является простой процесс изоляции компонентов и высокая плотность интеграции благодаря отсутствию изолирующих карманов. КНИ-структуры отличаются высокой радиационной стойкостью и повышенной надежностью при высоких температурах. Короткоканальные эффекты в КНИ-приборах могут быть подавлены простым уменьшением толщины кремниевого слоя. Наклон подпороговой характеристики у КНИ-транзисторов получается практически идеальным.

Однако перспективность КНИ-структур не является бесспорной. Основная проблема состоит в том, что КНИ-транзисторы имеют увеличенный подпороговый ток вследствие эффекта плавающей подложки, который устанавливает предел понижения потребляемой мощности в выключенном состоянии транзисторного ключа. Попытка понизить этот ток приводит к увеличению порогового напряжения, которое не позволяет уменьшить напряжение питания для уменьшения потребляемой мощности. Вторым принципиальным аргументом является то, что малая собственная емкость КНИ-транзистора перестает быть его преимуществом при дальнейшем сокращении размеров, поскольку уже в современных СБИС задержка в межсоединениях превышает задержку в вентилях.

Из известных к настоящему времени способов создания КНИ-структур рассмотрены те, которые имеют достаточно очевидные области приборного применения.

Тонкие пленки Si на изолирующих подложках. Как известно, большинство современных полупроводниковых приборов предъявляют очень высокие требования к структурному совершенству и электрофизическим характеристикам исходного материала. В связи с этим критической для методов, использующих осаждение пленки кремния на диэлектрические подложки, является прежде всего возможность формирования монокристаллической пленки.

В КНС-структурах это реализуется благодаря сравнительно малому отличию постоянных  $\Delta a$  решетки Si и сапфира. Однако  $\Delta a$ , не препятствующая эпитаксиальному росту кремния на сапфире, все же достаточно велика, и плотность дефектов структуры в кремнии вблизи границы с подложкой весьма значительна. Кроме того, в настоящее время отсутствует технология, позволяющая изготавливать сапфировые подложки такого диаметра, который типичен для современного микроэлектронного производства (200...300 мм). Но и при меньшем диаметре подложек из сапфира их стоимость весьма высока, что препятствует использованию КНС-структур в массовом производстве приборов. Это объясняет, почему появившиеся на рубеже 70-х годов и производимые до настоящего времени КНС МОП-транзисторы и КНС ИМС выпускаются в ограниченных количествах и используются преимущественно в аппаратуре, предназначенной функционировать при радиационных воздействиях. Существуют и другие диэлектрики, постоянная решетки которых близка к постоянной решетки кремния, к ним относятся прежде всего CaF<sub>2</sub> и ZrO<sub>2</sub>.

Кристаллизация пленок Si на диэлектрических подложках. Известно много работ, в которых различными способами пытались кристаллизовать поликри-

сталлические пленки, Si осажденные на поверхность диэлектрической пленки  $(SiO_2, Si_3N_4)$ , предварительно сформированной на поверхности Si. К таким способам относятся, например, перевод пленки поликристаллического кремния в жидкую фазу с последующей кристаллизацией или создание в пленке диэлектрика системы заполненных поликристаллическим кремнием отверстий, в которых он контактирует с поверхностью монокристаллической кремниевой подложки. Последнее определяет возможность эпитаксиальной кристаллизации поликристаллического кремния при термообработках.

Однако всем этим способам присущ общий недостаток. Они не могут сформировать монокристаллический слой Si высокого качества и большой площади. Поэтому возможности практического использования полученных подобным способом КНИ-структур ограничены КНИ-приборами малых размеров.

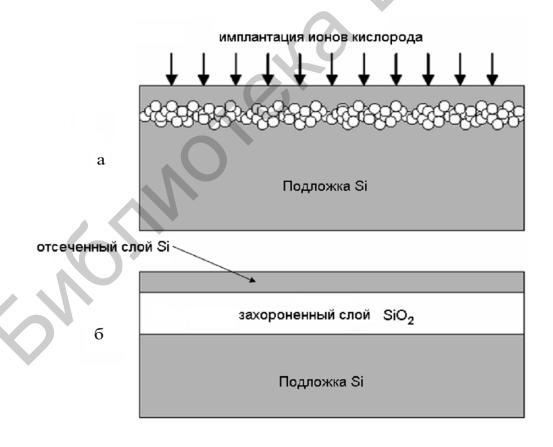

Реактивная ионная имплантация. Метод основан на имплантации химически активных ионов в Si, создании обогащенного ионами скрытого слоя в подложке и стимуляции твердофазной химической реакции между атомами Si и внедренной примеси (рисунок 45). Возможность имплантационного формирования скрытого в Si слоя  $SiO_2$  оказалась весьма привлекательной, и на рубеже 90-х годов рядом фирм был освоен промышленный процесс изготовления КНИ-структур, получивший название SIMOX (Separation by Implanted Oxygen).

а – после ионной имплантации кислородом;

б – после высокотемпературного отжига

Рисунок 45 – КНИ-структура, полученная методом SIMOX

Достоинства SIMOX-процесса очевидны. Прежде всего он позволяет создать КНИ-структуры на основе пластин Si любого диаметра. При этом качество компонентов структуры весьма высоко. Плотность дефектов в слое Si при соблюдении жестких требований производственной гигиены при имплантации и отжиге может быть не выше  $10^2$  см $^{-2}$ . Пробивное напряжение скрытого слоя  ${\rm SiO_2}$  составляет 300...400 В при толщине слоя 0,35...0,4 мкм. Однако столь же очевидны и недостатки SIMOX-процесса. Прежде всего процесс основан на использовании чрезвычайно больших доз имплантации кислорода ( $\sim 1,8\cdot 10^{18}$  см $^{-2}$ ). Для того чтобы внедрить такую дозу в технологически приемлемое время, пришлось разработать специализированные имплантеры с ионным током до 100 мА, что на порядок выше, чем у обычных промышленных имплантеров. Стоимость специализированных имплантеров очень высока, вследствие чего стоимость КНИ-структур, созданных с помощью SIMOX-процесса, существенно превышает стоимость исходной кремниевой пластины.

Другой недостаток SIMOX-процесса — необходимость очень высоких (~1300 °C) температур отжига, которые, как правило, не могут быть реализованы на стандартном термическом оборудовании (отжиг в нейтральной атмосфере необходим для растворения кислородсодержащих дефектов, возникающих при торможении части внедренных ионов кислорода в слое Si КНИструктуры). Предложено несколько способов, в той или иной мере исправляющих недостатки SIMOX-процесса.

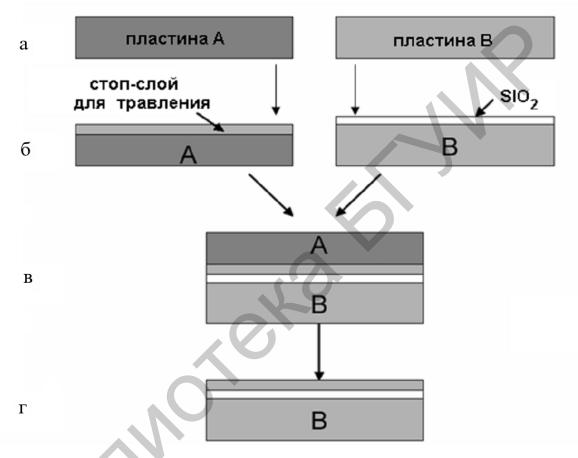

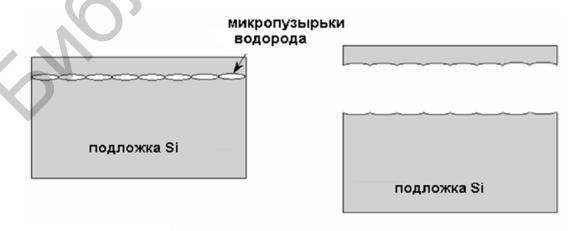

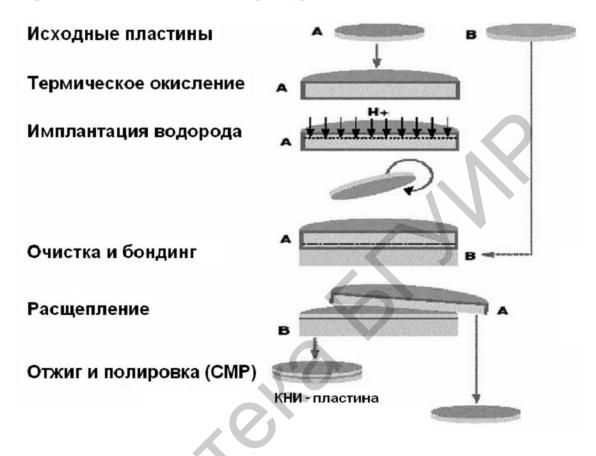

Один из них использует имплантацию пониженными дозами кислорода ( $\sim 5\cdot 10^{17}~{\rm cm}^{-2}$ ). Обычный для SIMOX отжиг таких пластин формирует в Si скрытый диэлектрический слой невысокого качества. Однако, если потом провести дополнительный отжиг при температуре  $\sim 1000~{\rm ^{\circ}C}$  в кислородсодержащей среде, диффузия кислорода сквозь Si дорастит скрытый слой SiO<sub>2</sub> и улучшит его качество. Такая технология, названная низкодозовым SIMOX-процессом, позволяет уменьшить дозу облучения и понизить стоимость КНИ-структур. Однако она не отменяет необходимость в отжиге при очень высоких температурах. Кроме того, дополнительный отжиг в кислороде означает, что толщина слоя Si в процессе термообработки будет уменьшаться из-за неизбежного роста пленки SiO<sub>2</sub> на его поверхности.