## ОПИСАНИЕ ПОЛЕЗНОЙ МОДЕЛИ К ПАТЕНТУ

(12)

(54)

РЕСПУБЛИКА БЕЛАРУСЬ

НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ (19) **BY** (11) **9628**

(13) U

(46) **2013.10.30**

(51) ΜΠΚ *H 03M 13/00* (2006.01) *H 04L 1/00* (2006.01)

# УСТРОЙСТВО ИТЕРАТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ

- (21) Номер заявки: и 20120990

- (22) 2012.11.13

- (71) Заявитель: Учреждение образования "Белорусский государственный университет информатики и радиоэлектроники" (ВҮ)

- (72) Авторы: Конопелько Валерий Константинович; Королёв Алексей Иванович; Салас Валор Нестор Альфредо; Хоанг Нгок Зыонг; Аль-алем Ахмед Саид (ВҮ)

- (73) Патентообладатель: Учреждение образования "Белорусский государственный университет информатики и радиоэлектроники" (ВУ)

(57)

Устройство итеративного кодирования и декодирования сверточных кодов, содержащее передатчик, в состав которого входят последовательно соединенные источник информации, первый ключ управления, первый кодер, первое оперативное запоминающее устройство, второй ключ управления, второй кодер, третий ключ управления, второе оперативное запоминающее устройство и четвертый ключ управления, выход которого подключен к каналу связи, а вторые входы первого, второго, третьего и четвертого ключей управления подключены к соответствующим выходам формирователя сигналов управления ключами передатчика, вход которого подключен к выходу генератора, а приемник содержит последовательно соединенные первый ключ управления, первое оперативное запоминающее устройство, второй ключ управления, первый пороговый декодер, четвертый ключ

Фиг. 1

управления, второе оперативное запоминающее устройство, пятый ключ управления, второй пороговый декодер и мажоритарный элемент, выход которого является выходом устройства итеративного кодирования и декодирования сверточных кодов, а второй вход мажоритарного элемента подключен через буферное устройство к выходу третьего ключа управления, первый вход которого подключен к выходу первого порогового декодера, а вторые входы первого, второго, третьего и пятого ключей управления подключены к соответствующим выходам формирователя сигналов управления ключами приемника, вход которого подключен к выходу генератора, а первый вход первого ключа управления подключен к выходу канала связи, отличающееся тем, что в передатчике введен перемежитель кодовых символов, вход которого подключен к выходу второго кодера, а выход перемежителя кодовых символов подключен к первому входу третьего ключа управления, а в приемнике введены деперемежитель кодовых символов и дополнительное буферное устройство, выход которого подключен к третьему входу мажоритарного элемента, а вход дополнительного буферного устройства объединен со входом первого порогового декодера и подключен к выходу деперемежителя кодовых символов, вход которого подключен к выходу второго ключа управления.

(56)

- 1. A.c CCCP 1185629, 1985.

- 2. A.c CCCP 646451, 1979.

- 3. Патент РБ 6593, 2010.

- 4. Витерби А.Д., Омура Дж.К. Принципы цифровой связи и кодирования. М: Радио и связь, 1982. С. 111.

- 5. Теория прикладного кодирования: Учеб. пособие. В 2 т. Т. 2 / Под ред. В.К.Конопелько. Минск: БГУИР, 2004. С. 49-51.

- 6. Кларк Дж. мл., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. М.: Радио и связь, 1978. С. 271-273.

Полезная модель относится к технике электросвязи и может быть использована в устройствах помехоустойчивого кодирования при передаче двоичной информации по каналам связи с группированием ошибок.

Известен пороговый декодер сверточного кода [1], содержащий кодер, корректор ошибок, формирователь синдрома, анализатор синдрома, три пороговых блока, корректор пакетов ошибок, мультиплексор импульсов коррекции, блок формирования тактовых импульсов, элемент совпадения, пороговый счетчик, формирователь временного интервала, D-триггер, инвертор, ключ и три блока коррекции информационных и синдромных символов.

Однако известный пороговый декодер сверточного кода обладает недостаточной помехоустойчивостью к группирующимся (пакетным) ошибкам, которая определяется тем, что пороговый декодер корректирует пакеты ошибок кратностью (длиной)  $t_{п.корр} \le n_0$  кодовых символов ( $n_0$  - длина миниблока кодовых символов, зависящая от скорости передачи кода R, определяемая выражением  $R = k_0/n_0$ ,  $k_0 = 1, 2, 3, ..., n_0 = n_0 + 1$ ), а также исключается возможность коррекции ошибочных информационных символов при поступлении на вход порогового декодера одновременно пакетных и случайных (независимых) ошибок.

Известно устройство кодирования и декодирования сверточных кодов [2], содержащее на передающей стороне источник информации, кодер и генератор и на приемной стороне содержащее кодер, формирователь синдрома, анализатор ошибок, основной регистр, первый и второй дополнительные регистры, двухсторонний обнаружитель, первый и второй дополнительные пороговые обнаружители, первый, второй и третий корректоры ошибок.

Однако известное устройство кодирования и декодирования сверточных кодов обладает недостаточной помехоустойчивостью к группирующимся (пакетным) ошибкам, а

также возможностью размножения ошибок, так как каждая не обнаруженная многопороговым декодером ошибка вводится через цепи коррекции анализаторов синдромов на входы пороговых обнаружителей в размноженном виде.

Наиболее близким аналогом к предлагаемому решению по совокупности признаков является устройство итеративного кодирования и декодирования сверточных кодов [3], содержащее передатчик, в состав которого входят источник информации, первый и второй кодеры, генератор, формирователь сигналов управления ключами передатчика, первый, второй, третий и четвертый ключи управления передатчика, первое и второе запоминающие устройства, и приемник, в состав которого входит первый, второй, третий, четвертый и пятый ключи управления приемника, первое и второе запоминающие устройства, первый и второй пороговые декодеры, генератор, формирователь сигналов управления ключами приемника, буферное устройство и мажоритарный элемент.

Однако известное устройство итеративного кодирования и декодирования сверточных кодов обладает недостаточной помехоустойчивостью к группирующимся (пакетным) ошибкам кратности  $t_{\rm n} > n_{\rm A1} = n_{\rm A2}$ , а также низкой достоверностью принятия решения мажоритарным элементом о полярности декодируемых информационных символов, так как решение мажоритарным элементом принимается только по двум результатам декодирования переданных информационных символов.

Задача данной полезной модели - повышение помехоустойчивости устройства итеративного кодирования и декодирования сверточных кодов при передаче двоичной информации по каналам связи с группированием ошибок.

Поставленная задача достигается тем, что в устройство итеративного кодирования и декодирования сверточных кодов, содержащее на передающей стороне последовательно соединенные источник информации, первый ключ управления, первый кодер, первое оперативное запоминающее устройство, второй ключ управления, второй кодер, третий ключ управления, второе оперативное запоминающее устройство и четвертый ключ управления, выход которого подключен к каналу с связи, а вторые входы первого, второго, третьего и четвертого ключей управления подключены к соответствующим выходам формирователя сигналов управления ключами передатчика, вход которого подключен к выходу генератора, а на приемной стороне последовательно соединенные первый ключ управления, первое оперативное запоминающее устройство, второй ключ управления, первый пороговый декодер, четвертый ключ управления, второе оперативное запоминающее устройство, пятый ключ управления, второй пороговый декодер и мажоритарный элемент, выход которого является выходом устройства итеративного кодирования и декодирования сверточных кодов, а второй вход мажоритарного элемента подключен через буферное устройство к выходу третьего ключа управления, первый вход которого подключен к выходу первого порогового декодера, а вторые входы первого, второго, третьего и пятого ключей управления подключены к соответствующим выходам формирователя сигналов управления ключами приемника, вход которого подключен к выходу генератора, а первый вход первого ключа управления подключен к выходу канала связи, на передающей стороне введен перемежитель кодовых символов, вход которого подключен к выходу второго кодера, а выход перемежителя кодовых символов подключен к первому входу третьего ключа управления, а на приемной стороне введены деперемежитель кодовых символов и дополнительное буферное устройство, выход которого подключен к третьему входу мажоритарного элемента, а вход дополнительного буферного устройства объединен со входом первого порогового декодера и подключен к выходу деперемежителя кодовых символов, вход которого подключен к выходу второго ключа управления.

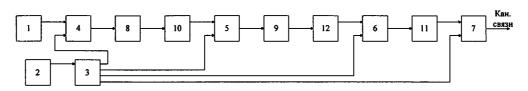

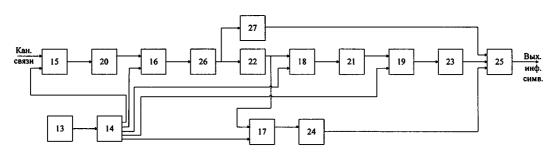

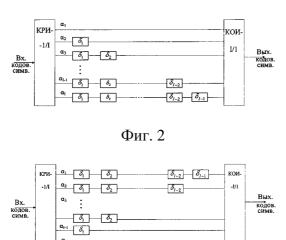

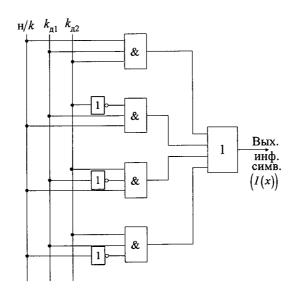

На фиг. 1 приведена структурная схема передатчика и приемника устройства итеративного кодирования и декодирования сверточного кода; на фиг. 2 и 3 - структурные схемы соответственно перемежителя и деперемежителя кодовых символов; на фиг. 4 - функциональная схема трехвходового мажоритарного элемента; на фиг. 5 - алгоритм работы трехвходового мажоритарного элемента.

Устройство итеративного кодирования и декодирования сверточных кодов содержит передатчик (фиг. 1), состоящий из источника информации (1), генератора (2), формирователя (3) сигналов управления ключами передатчика, первого (4), второго (5), третьего (6) и четвертого (7) ключей управления, первого (8) и второго (9) кодеров, первого (10) и второго (11) оперативных запоминающих устройств и перемежителя (12), и приемник, состоящий из генератора (13), формирователя (14) сигналов управления ключами приемника, первого (15), второго (16), третьего (17), четвертого (18) и пятого (19) ключей управления, первого (20) и второго (21) оперативных запоминающих устройств, первого (22) и второго (23) пороговых декодеров, буферного устройства (24), мажоритарного устройства (25), деперемежителя (26) кодовых символов и дополнительного буферного устройства (27).

Устройство работает следующим образом: в первоначальный момент времени первый (4) ключ управления открыт, а второй (5), третий (6) и четвертый (7) ключи управления закрыты. Передаваемые информационные символы через первый (4) ключ управления поступают на вход первого (8) кодера, где осуществляется их кодирование сверточным кодом с параметрами:  $R_{01} = k_{01}/n_{01}$ ,  $n_{01} = k_{01} + 1$ ,  $d_{01} = \mathfrak{I}_{01} + 1$ ,  $t_{\text{исп}} \leq \mathfrak{I}_{01}/2$  бит;  $R_{01}$  - скорость передачи сверточного кода,  $k_{01}$  - миниблок информационных символов,  $n_{01}$  - миниблок кодовых символов,  $d_{01}$  - минимальное кодовое расстояние,  $\mathfrak{I}_{01}$  - число ортогональных проверок,  $t_{\text{исп}}$  - кратность (количество) исправляемых ошибочных символов.

Сформированные символы кодовых последовательностей длиной  $n_{A1} = (m_{01} + 1) \cdot n_{01}$  бит, где  $m_{01}$  - максимальная степень порождающего полинома используемого сверточного кода, записываются по строкам в первое (10) оперативное запоминающее устройство; количество строк и столбцов данного устройства равно соответственно  $(n_{A1} \cdot R_{01}) \cdot n_{A1}$ .

После окончания записи кодовых символов по строкам первый (4) ключ управления закрывается, второй (5) и третий (6) ключи управления открываются, а четвертый (7) ключ управления остается в закрытом состоянии. Далее осуществляется посимвольное считывание кодовых символов по столбцам первого (10) оперативного запоминающего устройства на вход второго (9) кодера сверточного кода с параметрами, равными или отличными от параметров сверточного кода первого (8) кодера; далее рассматривается вариант использования сверточных кодов с равными (одинаковыми) параметрами.

Сформированные символы кодовых последовательностей второго (9) кодера поступают на вход перемежителя (12) кодовых символов, обеспечивающий преобразование пакетов ошибок кратностью  $t_n > n_{A1}$  бит в случайные (независимые) ошибки кратности  $t_{\text{исп}} \leq \mathfrak{I}_{01}/2$  бит;  $t_{\text{исп}} << t_n$ . Перемежитель (12) имеет треугольную конструкцию (фиг. 2) [4].

Интервал перемежения кодовых символов определяется выбором количества параллельных подпотоков (I), на которое распределяется входной поток кодовых символов, и начальной задержкой ( $\delta_1$ ) в тактах кодовых символов во втором ( $i_2$ ) подпотоке кодовых символов; кодовые символы первого ( $i_1$ ) подпотока передаются без задержки, а кодовые символы последнего (I) подпотока имеют задержку  $\delta_1 = (I-1)$  тактов. При выборе  $I = n_{A2}$  и  $\delta_2 = 1$  такт интервал перемежения кодовых символов составляет  $H = \delta_1 \cdot I = (I-1) \cdot I = (n_{A2}-1) \cdot n_{A2}$  тактов; при данных параметрах перемежителя (12) кодовых символов каждый пакет ошибок кратностью  $t_n = I = n_{A2}$  распределяется в одиночные ошибки на длине кодового ограничения  $n_{A2}$ . При выборе  $I = n_{A2}$  и  $\delta_2 = 2$  перемежитель (12) (фиг. 2) кодовых символов преобразует пакеты ошибок кратностью  $t_n = 2 \cdot n_{A2}$  на одиночные ошибки на длине кодового  $n_{A2}$ ; в рассматриваемом примере построения перемежителя (12) кодовых символов принимаем начальную задержку  $\delta_2 = 2$  тактам и интервал перемежения  $H = 2 \cdot \delta_1 \cdot I = 2 \cdot (n_{A2} - 1) \cdot n_{A2}$  двоичных символов, или бит.

Коммутатор объедения информации (КОИ – I/1) выполняется в виде мультиплексоров, имеющих I (I  $\geq$  4) информационных входов ( $a_1, a_2, ..., a_{I-1}, a_I$ ) и  $n = \log_2 I$  управляющих входов, а коммутатор распределения информации (КРИ – 1/I) выполняются в виде демультиплексоров, имеющих один вход и I/(I  $\geq$  4) выходов ( $a_1, a_2, ..., a_{I-1}, a_I$ ).

Перемеженные кодовые символы с выхода перемежителя (12) кодовых символов записываются через третий (6) ключ управления во второе (11) оперативное запоминающее устройство по столбцам; ранг второго (11) оперативного запоминающего устройства равен  $n_{A1} \times n_{A1}$  и определяется параметрами используемых сверточных кодов. По окончании записи  $N = n_{A1}^2$  кодовых символов второй (5) и третий (6) ключи управления закрываются, а открывается четвертый (7) ключ управления, и далее осуществляется считывание по строкам символов кодовых последовательностей сформированного итеративного сверточного кода.

Параметры итеративного сверточного кода в соответствии [5] и с методом кодирования передаваемой двоичной информации равны:  $R_{\text{и}} = R_{01} \cdot R_{02}, \ \Im_{\text{и}} = \Im_{01} \cdot \Im_{02}, \ d_{0\text{и}} = \Im_{\text{u}} + 1,$   $N_{\text{u}} = n_{\text{A1}} \cdot n_{\text{A2}} = n_{\text{A1}}^2, \ t_{\text{исп.и}} \leq \frac{(d_{0\text{u}} - 1(2))}{2}$  ошибочных символов. По окончании считывания

$N_{\rm u}$  кодовых символов четвертый (7) ключ управления закрывается, а первый (4) ключ управления открывается, и далее аналогичным образом осуществляется формирование символов следующей кодовой последовательности итеративного сверточного кода.

Декодер итеративного сверточного кода работает следующим образом: в первоначальный момент времени первый (15) ключ управления работой декодера открыт, а второй (16), третий (17), четвертый (18) и пятый (19) ключи управления работой декодера закрыты. Принятые символы кодовой последовательности итеративного сверточного кода записываются в течение  $N = N_{AU}$  тактов по строкам в первое (20) оперативное запоминающее устройство. В результате данной процедуры одиночный пакет ошибок кратности  $t_n \le n_{A1} = n_{A2}$  распределяется в одиночные ошибки на длине каждой кодовой последовательности исходных (базовых) сверточных кодов. По окончании записи  $n_{A1}^2 = n_{A2}^2$  кодовых символов первый (15) ключ управления закрывается, а открываются второй (16), третий (17) и четвертый (18) ключи управления, а пятый (19) ключ управления остается в закрытом положении.

Считываемые по столбцам кодовые символы из первого (20) оперативного запоминающего устройства поступают одновременно на вход дополнительного буферного устройства (27) и на вход деперемежителя (26) кодовых символов, структурная схема которого представлена на фиг. 3; деперемежитель (26) кодовых символов имеет конструкцию обратную перемежителю (12) кодовых символов: кодовые символы первого подпотока имеют задержку в  $2 \cdot (I-1)$  тактов, предпоследний подпоток кодовых символов передается с задержкой в  $\delta_{I-1} = 2$  такта, а последний подпоток кодовых символов передается без задержки. В результате деперемежения кодовых символов восстанавливается их порядок передачи, принятый на входе перемежителя (12) кодовых символов, а также преобразование пакетов ошибок кратности  $t'_n = 2 \cdot n_{A2} > t_n = n_{A2}$  бит в одиночные ошибки на длине каждой кодовой последовательности исходных сверточных кодов, обеспечивая таким образом возможность коррекции пакетных ошибок кратности  $t'_n = 2 \cdot n_{A2}$  бит, т.е. в два раза большей кратности, чем известное устройство итеративного кодирования и декодирования сверточных кодов.

Дополнительное буферное устройство (27) имеет задержку, равную  $Q = N + k_{02} + n_{02} = n_{A2}^2 + k_{02} + n_{02}$  тактов, и предназначено для хранения ( $n_{A2} \cdot R_{02}$ ) информационных символов, принятых из канала связи. Далее информационные ( $n_{A2} \cdot R_{02}$ ) символы последовательно поступают на один из входов мажоритарного элемента (25).

Кодовые символы, поступившие на вход первого (22) порогового декодера, проходят процедуру декодирования, обратную процедуре кодирования второго (9) кодера. В процессе декодирования сформированные символы с выхода первого (22) порогового декодера одновременно поступают на входы второго (21) оперативного запоминающего устройства и буферного устройства (24); в буферное устройство (24) записываются информационные символы сверточного кода второго этапа кодирования, выполненного в передатчике.

По окончании процедуры декодирования  $N_{AU}$  кодовых символов третий (17) ключ управления закрывается, пятый (19) ключ управления открывается, а первый (15) и второй (16) ключи управления приемного устройство остаются в закрытом состоянии. Далее осуществляется реализация второго этапа декодирования кодовых символов итеративного сверточного кода, а именно символов кодовых последовательностей, сформированных первым (8) кодером передатчика (фиг. 1), для чего кодовые символы с выхода второго (21) оперативного запоминающего устройства считываются построчно и поступают на вход второго (23) порогового декодера; первый (22) и второй (23) пороговые декодеры приемного устройства имеют одинаковый принцип построения; принцип построения пороговых декодеров зависит от конкретных параметров исходных сверточных кодов и алгоритма декодирования [6].

Информационные символы с выхода второго (23) порогового декодера поступают на второй вход мажоритарного элемента (25), а на третий вход мажоритарного элемента (25) поступают информационные символы, сформированные после первого этапа декодирования с выхода буферного устройства (24). Мажоритарный элемент (25) принимает решение по достоверности каждого принятого информационного символа по большинству одинаковых значений полярностей из трех входных информационных двоичных символов. На фиг. 4 приведена функциональная схема мажоритарного элемента (25), а на фиг. 5 - алгоритм формирования мажоритарным элементом (25) выходных информационных символов.

Так как принятие решения мажоритарным элементом (25) по типу (знаку) полярности декодируемых информационных символов выполняется по трем значениям полярностей информационных символов, то вероятность ошибочного принятия полярности принятого информационного символа в 1,5 меньше известного. Введение перемежителя (12) и деперемежителя (26) в устройство итеративного кодирования и декодирования сверточных кодов обеспечивает коррекцию пакетов ошибок в два раза большей кратности (длины), чем известное устройство. Для выбранных параметров перемежителя (12) и деперемежителя (26) кодовых символов и исходных сверточных кодов кратность корректируемых пакетов ошибок составляет  $t'_n = 2 \cdot n_{A2} = 2 \cdot 14 = 28$  бит, а известное устройство корректирует пакеты ошибок кратности  $t_{исп.и} = n_{A2} = 14$  бит.

Фиг. 3

Фиг. 4

| N  | н/k – не- | k <sub>ді</sub> – ко- | k <sub>д2</sub> – ко- | 1(x) -  |

|----|-----------|-----------------------|-----------------------|---------|

| ПП | кодиров.  | диров.                | диров.                | выходн. |

|    | инф.      | первой                | второй                | инф.    |

|    | симв.     | ступени               | сиупени               | симв.   |

| 1  | 1         | 1                     | 1                     | 1       |

| 2  | 1         | 1                     | 0                     | 1       |

| 3  | 0         | 1                     | 1                     | 1       |

| 4  | 1         | 0                     | 1                     | 1       |

| 5  | 1         | 0                     | 0                     | 0       |

| 6  | 0         | 1                     | 0                     | 0       |

| 7  | 0         | 0                     | 1                     | 0       |

Фиг. 5