## РАЗРАБОТКА 8-БИТНОГО АРИФМЕТИКО-ЛОГИЧЕСКОГО УСТРОЙСТВА

## Новиков П.Э.

Белорусский государственный университет информатики и радиоэлектроники г. Минск, Республика Беларусь

Ловшенко И.Ю. – ст. преподаватель каф. МНЭ, зав. НИЛ 4.4 НИЧ БГУИР

Аннотация. Приведены этапы разработки и основные результаты схемотехнического моделирования арифметико-логического устройства 8-битного микроконтроллера с архитектурой компьютера с сокращенным набором команд.

Арифметико-логическое устройство (АЛУ) представляет собой многофункциональную комбинационную цифровую логическую схему, которая требует одного или двух операндов (чисел на входе), на основе преобразования которых выдает результат.

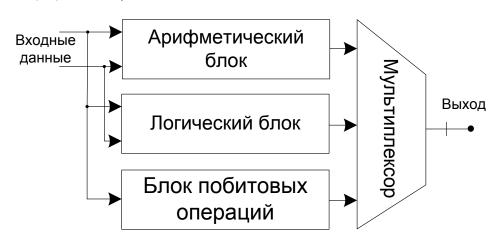

Структурная схема АЛУ, представленная на рисунке 1, позволяет выполнять арифметические, логические и побитовые операции. Логический блок представлен функциями «И», «ИЛИ», «НЕ», «ИСКЛЮЧАЮЩЕЕ ИЛИ», «ДОПОЛНЕНИЕ», арифметический — целочисленным многоразрядным сумматором, схема которого дополнена логикой, расширяющей его функциональные возможности, побитовый — операциями сдвига и сброса (установки) одного бита (всего 48 команд). Все блоки работают параллельно, выходной сигнал АЛУ формируется путем выбора выходного сигнала требуемого блока.

В целях достижения максимальной производительности и параллельности используется архитектура с раздельными памятью и шинами программ и данных. Команды в памяти программ выполняются с одноуровневой конвейеризацией. В процессе выполнения одной инструкции следующая предварительно считывается из памяти программ. Данная концепция позволяет выполнять одну инструкцию за один машинный цикл.

Помимо результирующего выхода АЛУ, также есть регистр флагов. Флаги АЛУ обычно включают флаг переноса, переполнения, отрицательный и нулевой и характеризуют выходные данные. Ряд операций использует только регистр флагов. Например, процесс реализации операции сравнения и требования к операндам такие же, как для операции вычитания, но при этом результат вычитания не сохраняется, а результат — установка флага нуля, если операнды равны, или отрицательного, если второй операнд больше первого. Данная информация может использоваться для ветвления программы по условию.

Рисунок 1 – Структурная схема АЛУ

Разработка устройства проводилась в программном комплексе компании Cadence на основе КМОП-транзисторов с проектными нормами 180 нм. В результате моделирования эксплуатационных характеристик установлено, что времена задержек сигналов на уровне 50% составили 1,1 нс, 1,0 нс, 0,7 нс и 2,1 нс при переключении из логического «0» в логическую «1», и 0,8 нс, 0,6 нс, 0,6 нс и 2,4 нс из «1» в «0» для арифметического, логического блоков и блока побитовых операций соответственно.

## Список использованных источников:

- 1. An optimization design approach for arithmetic logic unit / J. R. Shinde [et al.] // International Conference on Intelligent Computing and Communication Technologies, 2019. P. 707-716

- 2. The design off arithmetic logic unit based on ALM / H. Zhang [et al.] // International Workshop on Information and Electronics Engineering, 2012. P. 1969-1973