УДК 004.05:621.391.8

Курников Дмитрий Сергеевич, Кривабоков Дмитрий Андреевич

# РЕАЛИЗАЦИЯ БЛОЧНЫХ АЛГОРИТМОВ ПОМЕХОУСТОЙЧИВОГО КОДИРОВАНИЯ НА ПЛИС

В данной работе ведётся исследование блочных алгоритмов помехоустойчивого кодирования Хемминга, Рида-Соломона и ВСН на базе ПЛИС Altera Cyclone IV с архитектурой FPGA. Представлена система тестирования алгоритмов помехоустойчивого кодирования, описаны её основные узлы и принцип работы. Получены и проанализированы результаты синтеза и тестирования представленных кодов коррекции ошибок.

Помехоустойчивый код, кодирование ошибок, блочные алгоритмы, ПЛИС.

Kurnikov Dmitry Sergeevich, Krivabokov Dmitry Andreevich

## IMPLEMENTATION OF BLOCK ALGORITHMS FOR NOISE-TOLERANT CODING ON FPGAS

This paper studies block algorithms of noise-tolerant coding of Hemming, Reed-Solomon and BCH based on Altera Cyclone IV FPGA with FPGA architecture. The system of testing algorithms of noise-tolerant coding is presented, its main nodes and principle of operation are described. The results of synthesis and testing of the presented error correction codes are obtained and analyzed.

Noise-tolerant code, error coding, block algorithms, FPGA.

### Ввеление

Специфичные условия сред в которых распространяются сигналы различной природы и хранится информация могут вносить определённые искажения в исходные данные. Для борьбы с помехами, возникающими при приёмо-передаче и считывании информации учёными были разработаны специальные методы, одним из которых является помехоустойчивое кодирование.

Высокая помехоустойчивость сложной системы заключается во введении избыточности, необходимой для обнаружения и исправления ошибок, возникающих при взаимодействии с потоком данных [1]. Данный метод обработки информации нашёл своё применение в цифровой связи, компьютерных сетях, центрах обработки и хранения информации и космической технике. Существуют два принципиально различных типа помехоустойчивых кодов блочные и древовидные (непрерывные). Принцип работы первых заключается в разбиении непрерывной последовательности информационных символов на отрезки, содержащие к символов, или блоки. В дальнейшем операции производятся над каждым блоком в отдельности в соответствии с выбранным кодом.

При использовании древовидных кодов информационная последовательность подвергается обработке без предварительного разбиения её на независимые блоки. В кодирующем устройстве этого типа информация обрабатывается непрерывно и каждой длинной информационной последовательности сопоставляется кодовая последовательность, состоящая из несколько большого количества символов.

Существуют также свёрточные коды являющиеся частным случаем древовидных кодов. Эти коды отличаются наиболее простой реализацией, благодаря чему они получили широкое распространение.

В текущей работе будет рассмотрена реализации блочных алгоритмов помехоустойчивого кодирования (АПК) ошибок Хемминга [2], Рида-Соломона [3] и Боуза-Чодхури-Хоквингема (ВСН) [4] на программируемых логических интегральных схемах (ПЛИС). Результаты исследования могут быть полезны инженерам разработчикам при проектировании устройств обеспечивающих надёжную передачу и хранение данных.

В литературе [5] ПЛИС определяют, как интегральные схемы, выполняемые функции которых можно многократно изменять (конфигурировать) после изготовления. Основное преимущество использования подобных устройств заключается в возможности эффективно выполнять параллельные вычисления на больших тактовых частотах с малым энергопотреблением.

### Основная часть

Для аппаратного тестирования АПК была применена ПЛИС производства компании Altera семейства Cyclone IV с артикулом EP4CE6F17C8N. Данная программируемая логика построена на архитектуре FPGA (Field Programmable Gates Array) [6], имеет 6272 логических элемента, 179 портов ввода-вывода и 270 кбит встроенной памяти.

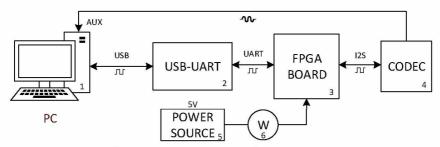

В рамках выполненной работы была разработана FPGA-система тестирования помехоустойчивых кодов на базе ПЛИС (рис. 1).

Рис. 1. Система тестирования кодов коррекции ошибок

Система состоит из следующих ключевых компонентов: 1 – персонального компьютера (ПК) с аудио входом AUX и интерфейсом USB версии 2.0 и выше; 2 – преобразователя интерфейсов USB-UART на микросхеме PL2303; 3 –отладочной платы на базе плис EP4CE6F17C8N; 4 – аудио кодека WM8960 с интерфейсом I2S; 5 – стабилизированного источника питания, настроенного на постоянное выходное напряжение 5В, имеющего нестабильность выходного напряжения на выбранном диапазоне до 10мВ; 6 – ваттметра с разрешением 0.001Вт и точностью ±(0.5%+2).

С помощью персонального компьютера осуществляется управление процессом тестирования. Для этого было написано специализированное программное обеспечение, в котором реализованы следующие функции: 1 – кодирование и декодирование аналоговых и цифровых сигналов в соответствии с выбранным алгоритмом коррекции ошибок; 2 – управление ПЛИС по интерфейсу UART [7] (переключение режима приём/передача); 3 – отправка и приём блоков помехоустойчивого кода по интерфейсу UART; 4 – отправка и приём аналоговых сигналов через звуковую карту ПК; 5 – сбор статистики о пакетах потерянных, принятых без ошибок, успешно декодированных и декодированных с ошибками (возникают в том случае, когда количество помех превышает корректирующую способность кода).

Ядром систем является отладочная плата с установленной на ней ПЛИС. На плате выведены интерфейсы для подключения вспомогательных модулей, присутствует загрузчик конфигурации, внешняя память, органы управления (кнопки, переключатели) и светодиодные индикаторы.

Для каждого АПК были разработаны модули кодирования и декодирования ошибок, конфигурация которых при очередном тестировании загружалась во внешнюю память. Применяемая в работе ПЛИС не имеет

встроенных аппаратных интерфейсов UART и I2C, поэтому они были описаны программно на языке Verilog [8]. Помимо этого, были добавлены модули преобразования последовательного кода в параллельный и обратно.

Кодек в системе выполняет функции аналогово цифрового и цифроаналогового преобразования [9]. Благодаря ему получившуюся систему можно встраивать в приложения, где использование аналогового сигнала целесообразнее (следует учитывать, что существуют различные методы модуляции и манипуляции аналоговых сигналов и для конкретного способа обмена информацией в конфигурацию ПЛИС нужно включать дополнительные модули преобразующие сигналы разного типа в нужную кодовую последовательность).

С помощью ваттметра осуществляется замер потребляемой ПЛИС мощности при работе того или иного алгоритма помехоустойчивого кодирования. Так как было произведено несколько замеров в таблицу 2 вошли усреднённые значения мощности. Все реализуемые в работе модули были написаны на языке описания аппаратуры Verilog. Разработка и тестирование модулей велись в программе Active-HDL\_SE\_2022. Синтез внутренней конфигурации ПЛИС и загрузка её в ПЗУ производились в программе Quartus Prime 22. Дополнительно при разработке и отладке модулей строились математические модели в программе РТС Matchcad Prime 6.0 и создавались приложения на языке Руthоп версии 3.8 с использованием фреймворка Qt Designer 5.14.1.

При синтезе логических схем [10] программой Quartus Prime были предоставлены параметры, отражающие использование ресурсов ПЛИС (табл. 1).

Использование ресурсов АПК

Таблица 1

| тенользование ресурсовиние |             |            |                         |                     |  |  |  |  |

|----------------------------|-------------|------------|-------------------------|---------------------|--|--|--|--|

| Название модуля            | Общее число | Количество | Логические ячейки, ис-  | Логические ячейки,  |  |  |  |  |

| или функции                | логических  | логических | пользующиеся только для | использующие        |  |  |  |  |

|                            | ячеек       | регистров  | реализации комбинаци-   | только регистры для |  |  |  |  |

|                            |             |            | онной логики            | хранения данных     |  |  |  |  |

| Hamming                    | 169         | 3          | 153                     | 2                   |  |  |  |  |

| -decoder                   | 58          | 0          | 57                      | 2                   |  |  |  |  |

| -encoder                   | 35          | 0          | 34                      | 2                   |  |  |  |  |

| Reed_Solomon               | 2874        | 1535       | 1091                    | 72                  |  |  |  |  |

| -decoder                   | 2463        | 1325       | 1136                    | 46                  |  |  |  |  |

| -encoder                   | 731         | 398        | 49                      | 8                   |  |  |  |  |

| ВСН                        | 1749        | 1262       | 917                     | 11                  |  |  |  |  |

| -decoder                   | 833         | 340        | 1097                    | 39                  |  |  |  |  |

| -encoder                   | 304         | 213        | 80                      | 25                  |  |  |  |  |

Анализ результатов синтеза (таблица 1) приводит к пониманию того, что модули, реализующие алгоритм Рила-Соломона, являются самыми сложными, в них задействовано наибольшее количество логических ячеек, регистров и комбинационной логики. Модули реализации ВСН занимают промежуточное положение. Модули реализации кода Хемминга имеют минимальными требованиями к логическим ячейкам и регистрам, они лучше подходят для менее требовательных задач.

Для проведения тестирования алгоритмов были созданы тестовые пакеты информации, состоящие из 24 бит каждый. В случайных местах пакетов были инвертированы от 1 до 8 бит. При кодировании пакетов помехоустойчивым алгоритмом данные разбивались на блоки по 6 бит к которым добавлялось по 2 контрольных бита (ограничено пропускной способностью интерфейса UART). Всего в обмене участвовало 1000 пакетов для каждого алгоритма. Результаты тестирования АПК представлены в табл. 2.

Результаты тестирования АПК

Таблица 2

| Назва-    | Процесс     | Время    | Потребляе- | Успешно    | Число паке- | Число успешно |

|-----------|-------------|----------|------------|------------|-------------|---------------|

| ние АПК   |             | обработ- | мая мощ-   | обработан- | тов содер-  | декодирован-  |

|           |             | ки (мс)  | ность      | ные пакеты | жащих       | ных пакетов   |

|           |             |          | (мВт)      |            | ошибки      |               |

| Код Хе-   | кодирование | 11       | 21         | 985        | 60          | 45            |

| мминга    | декодирова- | 13       | 26         | 989        | 57          | 49            |

|           | ние         |          |            |            |             |               |

| Код Рида- | кодирование | 53       | 105        | 996        | 38          | 33            |

| Соломона  | декодирова- | 61       | 113        | 995        | 49          | 45            |

|           | ние         |          |            |            |             |               |

| ВСН код   | кодирование | 31       | 73         | 991        | 30          | 25            |

|           | декодирова- | 38       | 82         | 993        | 48          | 40            |

|           | ние         |          |            |            |             |               |

При аппаратном тестирования АПК код Рида-Соломона проявил себя как наиболее эффективный в контексте исправления ошибок. Однако его эффективность обусловлена увеличенным временем обработки и потреблением энергии по сравнению с алгоритмами Хемминга и ВСН. Код Хемминга, в свою очередь, обеспечивает быструю обработку и низкое энергопотребление, но ограничен в возможностях исправления ошибок. ВСН код показывает результаты промежуточного уровня, он сбалансирован между способностью к исправлению ошибок и затратами времени и энергии.

### Выводы

Работа по реализации и тестированию блочных АПК на ПЛИС подтвердила их эффективность в обнаружении и исправлении ошибок.

Разработанная в данном исследовании система тестирования АПК помогла выявить наиболее эффективный с точки зрения надёжности алгоритм – код Рида-Соломона и расставить приоритеты использования других АПК. Применяя представленную схему, инженеры могут производить собственные исследования интересующих их параметров.

Результаты синтеза и тестирования АПК могут быть использованы разработчиками на этапе проектирования изделий при выборе модели ПЛИС и АПК необходимых для выполнения технического задания.

## БИБЛИОГРАФИЧЕСКИЙ СПИСОК

- 1. *Питерсон У У.* Коды, исправляющие ошибки. М.: Мир, 1976. 600 с.

- 2. *Кудрявцев А.В., Енгалычев И.Р., Кашапов А.Р.* Применение помехозащищённого кодирования для повышения целостности информации погружной телеметрии //Молодой ученый. -2011. -№ 1 (24). C. 25-27.

- 3. Дружсинин В.И., Кузьмин О.В. Коды Рида-Соломона в системах обнаружения и исправления оппибок при передаче данных //Современные технологии. Системный анализ. Моделирование. 2015. №1 (45). С. 21-30.

- 4. *Калыгин Г.О.* Исследование дистанционных свойств кода БЧХ //Молодой ученый. -2020. -№ 9 (299). C. 22-26.

- 5. *Ушенина И.В.* Проектирование цифровых устройств на ПЛИС 2-е изд., стер. СПб.: Лань, 2023. 408 с.

- 6. *Игошина М.С.* Архитектуры современных ПЛИС: Достоинства и недостатки //Теория и практика современной науки. −2021. №11 (77). С. 228-231.

- 7. *Магада Ю.С.* Программирование последовательных интерфейсов. СПб.: БХВ-Петербург, 2009 304 с.

- 8. Строгонов А.А. Изучение принципов работы ЦАП и АЦП с помощью средств смешанного аналого-цифрового моделирования САПР OrCAD //Компоненты и Технологии. 2007. №76. С. 137-143.

- 9. *Соловьев В.В.* Основы языка проектирования цифровой аппаратуры Verilog 2-е изд., испр. и доп. М.: Горячая линия Телеком, 2024. 284 с.

- 10. Цифровой синтез: практический курс / А.А. Антонов, А.В. Барабанов, Ч.Т. Данчек, С.Л. Жельнио, С.А. Иванец, И.А. Кудрявцев, Ю.В. Панчул, А.Ю. Романов, И.И. Романова, А.А. Телятников, М.С. Шуплецов. М.: ДМК Пресс, 2020. 556 с.

**Курников Дмитрий Сергеевич**, студент группы ЭВМ-2.1 Волгоградского государственного технического университета, Россия, город Волгоград, email: <u>kurnikov.2000@yandex.ru</u>.

**Кривабоков Дмитрий Андреевич**, студент группы ЭВМ-2.1 Волгоградского государственного технического университета, Россия, город Волгоград, email: dimakrivabokov@yandex.ru.

**Kurnikov Dmitry Sergeevich**, Student of group EVM-2.1 of Volgograd State Technical University, Russia, Volgograd, email: <a href="mailto:kurnikov.2000@yandex.ru">kurnikov.2000@yandex.ru</a>.

**Krivabokov Dmitry Andreevich**, Student of group EVM-2.1 of Volgograd State Technical University, Russia, Volgograd, email: <a href="mailto:dimakrivabokov@yandex.ru">dimakrivabokov@yandex.ru</a>.