# ИССЛЕДОВАНИЕ ВРЕМЕНИ ВЫПОЛНЕНИЯ ЧАСТИЧНОЙ РЕКОНФИГУРАЦИИ FPGA XILINX

Босько Н. В., Луцик Ю. А. Кафедра электронных вычислительных машин, Белорусский государственный университет информатики и радиоэлектроники Минск, Республика Беларусь E-mail: nadezhdabosko@gmail.com

В данной работе представлены результаты исследования времени, затрачиваемого на выполнение частичной реконфигурации на FPGA Xilinx. Представлены результаты измерения времени реконфигурации для ряда реконфигурируемых модулей с различными характеристиками. Проанализирована зависимость данного времени от размера используемых частичных битстримов, а также размера битстримов от размера заданной реконфигурируемой области.

#### Введение

Способность FPGA к реконфигурации — изменению реализуемой ресурсами кристалла FPGA логической схемы — является их определяющим свойством. Под функцией частичной реконфигурации понимается возможность изменения отдельной части реализуемой на FPGA логической схемы, в то время как остальная, статическая её часть остается неизменной и продолжает работать.

Для использования частичной реконфигурации предварительно задаются области кристалла, доступные для частичной реконфигурации (реконфигурируемые области) и разрабатываются все доступные для загрузки в них реконфигурируемые модули. Для выполнения частичной реконфигурации используются частичные битстримы (файлы для конфигурации FPGA), каждому из которых соответствует определенный реконфигурируемый модуль.

При разработке динамически реконфигурируемых устройств на FPGA важно иметь представление о времени, затрачиваемом на выполнение частичной реконфигурации, и влияющих на него факторах. Это позволяет принять наиболее оптимальные решения о характеристиках предполагаемых к реконфигурации модулей.

## І. Описание исследования

Исследование было проведено с использованием FPGA Xilinx XC7A100TFGG484-2. В терминологии Xilinx технология динамической частичной реконфигурации имеет название Dynamic Function eXchange (DFX) [1]. В [1] указано, что время частичной реконфигурации напрямую зависит от размера используемого частичного битстрима. В данном исследовании была проанализирована указанная зависимость.

Частичная реконфигурация выполнялась с помощью IP-ядра DFX Controller [2], подключенного к ICAP (Internal Configuration Access Port). Используемая в проекте тактовая частота составляла 100 МГц, что является максимальной тактовой частотой для ICAP [1]. Частичные битстримы

для всех реконфигурируемых модулей были предварительно записаны во внешнюю DDR3-память, доступную IP-ядру DFX Controller.

Выполнение частичной реконфигурации инициировалось путем подачи на DFX Controller сигналов-триггеров, соответствующих необходимым для загрузки модулям. Данные сигналы контролировались с помощью VIO (Virtual Input-Output). Измерение времени частичной реконфигурации производилось с помощью пользовательского ІР-ядра, сохраняющего количество тактов, на протяжении которых был активен заданный сигнал. В данном случае измерение проводилось с использованием сигналов vsm <name> rm decouple от DFX Controller, которые переходят в состояние «1» по началу реконфигурации и возвращаются в состояние «0» по ее завершению [2]. Стоит отметить, что в проведенных экспериментах было использовано сжатие частичных битстримов.

На кристалле были заданы три реконфигурируемые области (РО) разных размеров, содержащие указанное в таблице I количество основных ресурсов.

Таблица 1 – Количество ресурсов в исследуемых РО

| *  |       | 1 /1  |       | •   |

|----|-------|-------|-------|-----|

| PO | Slice | Slice | Slice | DSP |

|    | LUTs  | regs  |       |     |

| A  | 6856  | 13712 | 1714  | 16  |

| В  | 1152  | 2592  | 288   | 0   |

| C  | 160   | 320   | 40    | 0   |

Для РО «А» было создано четыре реконфигурируемых модуля (РМ): А1-А4, для РО «В» и РО «С» – по два: В1-В2 и С1-С2. Используемые для проведения исследования модули реализуют различные арифметические операции. В таблице 2 указаны используемые данными модулями ресурсы, а также размеры в байтах частичных битстримов, сгенерированных для каждого из модулей.

## II. Результаты исследования

Было измерено количество тактов, затрачиваемое на выполнение частичной реконфигурации для каждого из модулей. Измерение для

каждого модуля было проведено 3 раза, после чего было определено среднее значение. Результаты измерений, переведенные в наносекунды, представлены в таблице 3 (средние значения были округлены).

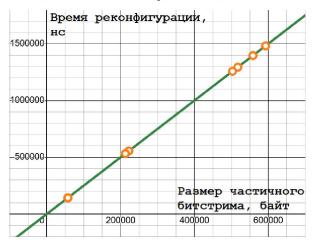

По результатам измерений можно увидеть линейную зависимость между размером частичного битстрима реконфигурируемого модуля и временем, требуемом для его загрузки. График данной зависимости представлен на рисунке 1. Точками отмечены измеренные значения.

Рис. 1 – График зависимости времени реконфигурации от размера битстрима

Реконфигурация начинается тогда, когда начинается передача частичного битстрима на ICAP, и завершается, когда весь битстрим был передан. Соответственно, время реконфигурации увеличивается линейно при доставке на ICAP больших объемов данных. Примерная формула зависимости: y=2,50001x+666,2277.

С помощью данной зависимости можно получить представление о времени, требуемом на реконфигурацию модуля, размер битстрима которого известен. На время реконфигурации также могут оказывать влияние другие факторы, такие

как, например, задержки при чтении данных из внешней памяти IP-ядром DFX Controller.

### III. Размер битстрима

Так как время частичной реконфигурации напрямую зависит от размера используемого частичного битстрима, следует обратить внимание также на факторы, от которых зависит последний. Можно заметить, что реконфигурируемые модули области «А» используют разные объемы ресурсов. Однако при этом размеры частичных битстримов модулей примерно схожи в пределах одной РО, и значительно различаются между разными РО.

Из этого можно сделать вывод, что размер частичного битстрима модуля напрямую зависит от размера реконфигурируемой области, в которой он используется, даже если в действительности реконфигурируемый модуль занимает только малую часть данной реконфигурируемой области.

#### IV. Выводы

Из результатов проведенного исследования можно сделать вывод, что при планировании реконфигурируемых областей и разработке реконфигурируемых модулей являются нежелательными ситуации, в которых в РО используются модули, занимающие лишь малую часть их ресурсов. При этом для сокращения затрачиваемого на частичную реконфигурацию времени размеры реконфигурируемых областей следует минимизировать.

- AMD. Vivado Design Suite User Guide: Dynamic Function eXchange [Electronic resource]. - Mode of access: https://docs.amd.com/r/en-US/ug909vivado-partial-reconfiguration/. - Date of access: 23.10.2025.

- AMD. Dynamic Function eXchange Controller Product Guide [Electronic resource]. – Mode of access: https: //docs.amd.com/v/u/en-US/pg374-dfx-controller/. – Date of access: 23.10.2025.