# ГРАФОВЫЕ МОДЕЛИ ЗАДАЧ, ВОЗНИКАЮЩИХ ПРИ ДЕКОМПИЛЯЦИИ КМОП СБИС

#### Черемисинова Л. Д.

Объединённый институт проблем информатики Национальной академии наук Беларуси Минск, Республика Беларусь E-mail: cld@newman.bas-net.by

Рассматриваются методы решения ключевых задач, возникающих при распознавании подсхем, реализующих КМОП-вентили, в плоской транзисторной схеме. Предлагаются графовые модели представления транзисторных схем при решении этих задач.

#### Введение

Современные КМОП СБИС содержат миллионы примитивных элементов уровня транзисторов, и их сложность быстро увеличивается. Инструментом, позволяющим существенно снизить трудоемкость тестирования схем такой сложности, служит средство их обратного проектирования (декомпиляции), в процессе которого представление схемы на транзисторном уровне заменяется функционально эквивалентным представлением на уровне логических элементов.

В настоящей работе рассматриваются некоторые ключевые задачи и методы, на которые разбивается процесс обратного проектирования КМОП схем на транзисторном уровне, заключающийся в экстракции из них структур на уровне логических элементов. Предлагаются графовые модели представления транзисторных схем при решении этих задач.

### І. Декомпиляция транзисторных схем

Исходным объектом декомпиляции является плоское описание схемы из р-МОП и п-МОП транзисторов. Исходная плоская и результирующая иерархическая транзисторные схемы представляются в формате проектирования SPICE. Рассматривается наиболее распространенный стиль логики — логические комплементарные МОП-структуры и структуры на основе проходных транзисторов. Предполагается, что декомпилированная схема может содержать КМОП вентили, передаточные логические элементы и подсхемы на их основе, а также псевдоэлементы (нераспознанные как КМОП вентили).

В процессе декомпиляции выполняются следующие основные этапы [1]: 1) выделение подсхем, представляющих передаточные вентили и подсхемы (типа мультиплексоров) на их основе; 2) разбиение транзисторной схемы на подсхемы, состоящие из транзисторов, связанных по постоянному току; 3) распознавание «правильных» подсхем, представляющих КМОП вентили, а также реализуемых ими функций; 4) выделение групп функционально и топологически идентичных КМОП вентилей и псевдоэлементов — формирование библиотеки; 5) построение двухуровневой логической сети.

## II. Задание транзисторных схем

Главной частью исходного плоского SPICE-описания является список транзисторов, в котором для каждого транзистора указываются имена цепей nd, ng, ns и nb, соединяющих его выводы (стока - drain, затвора - gate, истока - source, подложки - substrate) с остальными частями схемы: M<name> <nd> <ng> <ns> <nb> <model-name>, где name и model-name - название и тип (например, nmos или pmos) транзистора.

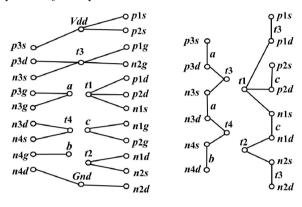

Связи транзисторной схемы удобно представлять помеченным неориентированным двудольным графом  $G=(V_1,V_2,E),\,V_1\,\cap\,V_2=\oslash$ . В нем вершины из первой доли  $V_1$  соответствуют выводам экземпляров транзисторов и портов схемы, а вершинам из  $V_2$  ставятся в соответствие цепи схемы. Например, структура приведенной на рис. 1 транзисторной схемы представляется графом G (рис. 2), для которого  $V_1=\{n_1d,n_1g,n_1s,\ldots,p_3d,p_3g,p_3s\},\,V_2=\{Vdd,Gnd,a,b,c,t_1,t_2,t_3,t_4\}.$

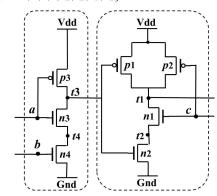

Рис. 1 – Пример транзисторной схемы

# III. РАСПОЗНАВАНИЕ ГРУПП ТРАНЗИСТОРОВ, СВЯЗАННЫХ ПО ТОКУ

Статическая КМОП-схема имеет четко определенную структуру, и соответствующая ей подсхема, представляет собой группу транзисторов, связанных по току. Такой группой является произвольная схема из МОП-транзисторов с тремя типами внешних соединений: 1) входы группы подаются только на затворы ее транзисторов; 2) выходы группы подаются только на затворы тран-

зисторов других групп; 3) имеются связи транзисторов с шинами питания (Vdd и Gnd).

В графовой интерпретации задача поиска групп транзисторов, связанных по току, сводится к нахождению компонент связности графа H (рис. 2), получаемого из графа G путем: 1) удаления вершин, соответствующих выводам затворов транзисторов и цепям питания; 2) соединения ребром вершин, соответствующих выводам стока и истока, для каждого транзистора. Группы транзисторов, соответствующие найденным двум компонентам связности графа H, выделены на рис. 1 пунктирными линиями.

Рис. 2 – Графы G и H

# IV. Распознавание подсхем, реализующих КМОП-вентили

Статический КМОП-вентиль содержит n- и p-подсхемы, состоящие соответственно из п-МОП- и p-МОП-транзисторов. Эти подсхемы включены последовательно между цепями питания и разделены выходной цепью, а их проводимости комплементарны. Группа транзисторов, связанных по току, реализует КМОП-вентиль, если p- и п-блоки имеют одинаковое количество транзисторов и реализуют взаимно инверсные функции проводимости  $f_n$  и  $f_p$ . Группы, не удовлетворяющие этим двум условиям, относятся у псевдоэлементам. Например, левая из выделенных на рис. 1 подсхем является псевдоэлементом, так как не удовлетворяет первому условию.

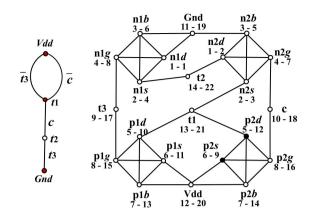

В графовой постановке задача нахождения функций проводимости  $f_n$  и  $f_p$  сводится к поиску путей, связывающих выходную цепь подсхемы (на рис. 1 это  $t_1$ ) с цепями питания (Gnd и Vdd). Задача решается на графе I, который получается графа G путем удаления вершин, соответствующих выводам затворов транзисторов и соединения вершин выводов стока и истока для каждого транзистора, ребром, которое помечается именем цепи, связанной с затвором данного транзистора (рис. 3). Просмотр цепей графа І позволяет найти функции, реализуемые p- и n-блоками:  $f_p = \overline{t_3} \vee \overline{c}$  и  $f_n = c \wedge t_3$ . Эти функции взаимно инверсны, что говорит о том, что правая подсхема на рис. 1 есть КМОП-вентиль 2И-НЕ, реализующий функцию  $f = c \wedge t_3$ .

Рис. 3 — Графы I и T

# V. Выделение классов топологически изоморфных элементов

На этом этапе множества подсхем, соответствующих распознанным КМОП-вентилям и псевдоэлементам, разбиваются на классы топологически изоморфных. Каждая из таких групп определяет элемент библиотеки подсхем второго уровня описания транзисторной схемы. Задача сводится к проверке изоморфизма помеченных графов для анализируемых подсхем путем приведения каждого из них к каноническому виду. Хеши канонических маркировок графов для изоморфных подсхем будут совпадать.

Для выполнения задачи канонизации граф, представляющий каждую из анализируемых подсхем, дополняется ребрами, связывающими попарно выводы каждого из его транзисторов. Каждая из подсхем задается помеченным графом T=(W,F,h), где  $h(w_i)$  — метка вершины из W. Метки 1–4 (5–8) присвоены вершинам графа, соответствующим выводам стока, истока, подложки и затвора п-МОП-транзисторов (р-МОП-транзисторов), затем идут метки входных и выходных полюсов схемы, Gnd, Vdd и, наконец, цепей схемы. Для найденной подсхемы И-НЕ на рис. З приведен граф T, в котором под именем каждой вершины указаны ее метки (начальная и полученная в результате канонизации).

### VI. Заключение

Предложенные графовые модели и основанные на них методы решения ключевых задач распознавания подсхем КМОП-вентилей и построения иерархического описания на уровне логических элементов реализованы на языке C++ как часть программы декомпиляции плоской транзисторной схемы.

### VII. Список литературы

Черемисинов, Д. И. Извлечение сети логических элементов из КМОП схемы транзисторного уровня / Д. И. Черемисинов, Л. Д. Черемисинова // Микроэлектроника. – 2019. – № 3 (48). – С. 224-234.