Министерство образования Республики Беларусь

Учреждение образования

«Белорусский государственный университет

информатики и радиоэлектроники»

Факультет компьютерных систем и сетей

Кафедра электронных вычислительных средств

**М. И. Вашкевич, В. Н. Пригодич**

**ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ

НА ЯЗЫКАХ VHDL И SYSTEMVERILOG.

ЛАБОРАТОРНЫЙ ПРАКТИКУМ**

*Рекомендовано УМО по образованию в области информатики

и радиоэлектроники в качестве пособия для специальности

6-05-0611-05 «Компьютерная инженерия»*

Минск БГУИР 2025

УДК 004.43(076.5)

ББК 32.973.2я73

В23

Рецензенты:

кафедра «Технология и методика преподавания»

Белорусского национального технического университета

(протокол № 1 от 02.09.2024);

ведущий инженер-программист ООО «МайкоДизайн»

кандидат физико-математических наук, доцент С. Е. Бухтояров

**Вашкевич, М. И.**

В23      Проектирование цифровых устройств на языках VHDL и SystemVerilog. Лабораторный практикум : пособие / М. И. Вашкевич, В. Н. Пригодич. – Минск : БГУИР, 2025. – 91 с. : ил.

ISBN 978-985-543-806-0.

Предназначено для изучения основ проектирования цифровых устройств с использованием языков описания аппаратуры – VHDL (Very high speed integrated circuit Hardware Description Language) и SystemVerilog. Подробно разобраны основные конструкции языка VHDL, используемые для описания комбинационных схем и тестового окружения VHDL-проекта. Уделено внимание вопросам иерархического и поведенческого описания работы цифровых устройств. Описан процесс моделирования цифровых устройств с учетом временных задержек логических вентилей, показано, как оценить критический путь комбинационной схемы. Дано описание основных средств языка SystemVerilog, используемых как для структурного описания проектов, так и описания на уровне регистровых передач. Приведен общий маршрут проектирования цифрового устройства в САПР Vivado.

УДК 004.43(076.5)

ББК 32.973.2я73

**ISBN 978-985-543-806-0**

© Вашкевич М. И., Пригодич В. Н., 2025

© УО «Белорусский государственный

университет информатики

и радиоэлектроники», 2025

## СОДЕРЖАНИЕ

|                                                                                                                                   |    |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| Лабораторная работа № 1. Проектирование комбинационных схем на VHDL .....                                                         | 4  |

| 1.1. Теоретические сведения.....                                                                                                  | 4  |

| 1.2. Порядок выполнения работы.....                                                                                               | 31 |

| 1.3. Дополнительные вопросы и задания .....                                                                                       | 32 |

| Лабораторная работа № 2. Временное моделирование цифровых устройств .....                                                         | 33 |

| 2.1. Теоретические сведения.....                                                                                                  | 33 |

| 2.2. Порядок выполнения работы.....                                                                                               | 43 |

| 2.3. Дополнительные вопросы и задания .....                                                                                       | 43 |

| Лабораторная работа № 3. Проектирование цифровых устройств на уровне<br>вентилей и регистрационных передач на SystemVerilog ..... | 45 |

| 3.1. Теоретические сведения.....                                                                                                  | 45 |

| 3.2. Порядок выполнения работы.....                                                                                               | 80 |

| 3.3. Дополнительные вопросы и задания .....                                                                                       | 81 |

| Приложение. Варианты для лабораторной работы № 2 .....                                                                            | 82 |

| Список использованных источников.....                                                                                             | 89 |

# ЛАБОРАТОРНАЯ РАБОТА № 1. ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННЫХ СХЕМ НА VHDL

ЦЕЛЬ РАБОТЫ: изучение основных конструкций языка VHDL, освоение маршрута проектирования и моделирования цифрового устройства в САПР Vivado.

## 1.1. Теоретические сведения

### 1.1.1. Краткая история VHDL

Язык VHDL (*Very high speed integrated circuits Hardware Description Language*) применяется для описания цифровых устройств во многих САПР, используемых для разработки заказных интегральных схем (*application specific integrated circuit – ASIC*), а также для создания проектов на базе программируемых логических интегральных схем (ПЛИС) и программируемых пользователями вентильных матриц (*Field-Programmable Gate Arrays – FPGA*). Данный язык предназначен для описания проектируемых систем и их моделирования на начальных этапах проектирования – алгоритмическом и логическом.

VHDL был разработан по заказу министерства обороны США. Первоначально язык VHDL предназначался для описания структуры и функциональности электронных схем и выступал альтернативным способом представления принципиальной и функциональной схемы устройства. Однако вскоре стало понятно, что такой способ описания хорошо подходит для задач моделирования, а также синтеза цифровых схем. В 1987 году конструкции языка VHDL были закреплены в стандарте IEEE 1076–1987. Данный стандарт еще называют VHDL'87. В 1993 году был принят второй стандарт на язык VHDL – IEEE 1076–1993, называемый еще VHDL'93. Опыт разработчиков со временем обобщается и формализуется в новых версиях стандартов на языки описания аппаратуры. В настоящее время наибольшее распространение имеет версия языка VHDL 2008 года (стандарт IEEE 1076–2008).

### 1.1.2. Базовые конструкции языка VHDL

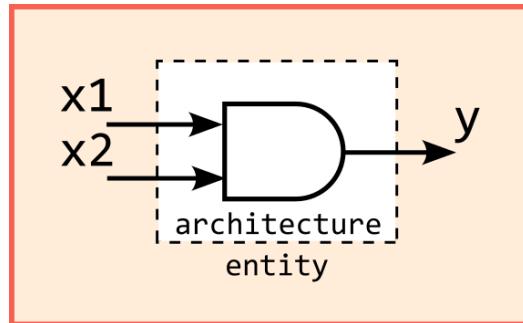

Чтобы начать знакомство с языком VHDL, рассмотрим, как на нем можно описать двухходовой вентиль И (рис. 1.1).

Рис. 1.1. Вентиль И

Ниже приведено VHDL-описание вентиля И.

```

entity gate_and is

port (

x1 : in  std_logic;

x2 : in  std_logic;

y  : out std_logic

);

end gate_and;

architecture RTL of gate_and is

begin

y <= x1 and x2;

end RTL;

```

Рассмотрев внимательно данный код, можно отметить ряд особенностей VHDL-описания цифровых схем. Описание начинается с ключевого слова `entity`, после которого указывается название схемы, далее описывается ее интерфейс. Таким образом, `entity` определяет интерфейс между объектом и внешним окружением, при этом «внутренность» объекта проекта уподобляется «черному ящику».

В интерфейсе рассматриваемой схемы присутствует несколько портов, которые задаются с использованием следующего формата.

```

<идентификаторы портов> : <направление> <тип порта>;

```

В приведенном примере схема имеет два входных порта: `x1` и `x2`, а также один выходной порт `y`. Для каждого порта указывается его направление `in` или `out`, кроме этого, для описания двунаправленных портов используется ключевое слово `inout`. Также для портов указывается тип данных, в данном случае это `std_logic`. Этот тип данных используется для описания логических уровней цифровых сигналов. Помимо значений '`0`' и '`1`' тип `std_logic` может принимать значения '`Z`' (третье состояние), '`X`' (неопределенное состояние) и некоторые другие.

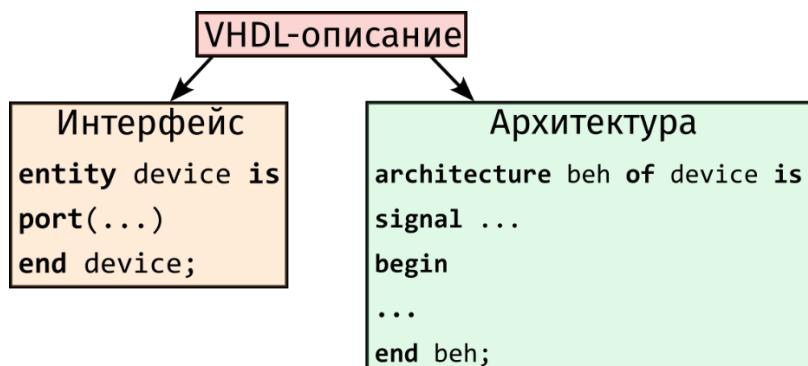

После интерфейсной части схемы описывается ее архитектурное тело (рис. 1.2).

Рис. 1.2. Структура VHDL-описания

В приведенном примере описания вентиля И архитектурное тело имеет название RTL. Внутри архитектурного тела описывается логика работы схемы. В рассматриваемом примере выходу у назначается результат выполнения логической операции И над двумя входными сигналами  $x_1$  и  $x_2$  (рис. 1.3).

Рис. 1.3. VHDL-описание: интерфейс (entity) и архитектура

В общем виде интерфейс схемы/устройства на языке VHDL описывается следующим образом.

```

entity <название схемы> is

[generic(<список параметров>);]

[port(<список портов>);]

end [<название схемы >];

```

Помимо уже известной нам секции `port` в интерфейсе может содержаться секция `generic`, которая используется для задания параметров схемы. Например, при описании сумматора в качестве параметра может выступать разрядность входных/выходных сигналов.

Общее описание архитектурного тела приведено ниже.

```

architecture <имя архитектуры> of <название схемы> is

[<область объявлений архитектуры>]

begin

<операторы архитектуры>

end [<имя архитектуры>];

```

Язык VHDL позволяет для каждого объекта иметь несколько архитектур. Например, часто для одного объекта создают два описания архитектуры: одно поведенческое, а другое структурное. «Внутренность» архитектуры представляет собой ряд параллельных операторов.

VHDL-описание устройства, состоящее из интерфейса (entity) и архитектуры (architecture), сохраняется в проектном файле с расширением .vhd (рис. 1.4).

### Проектный файл device.vhd

```

entity device is

port(...);

end device;

architecture beh of device is

begin

...

...

end beh;

```

Рис. 1.4. Проектный файл с VHDL-описанием устройства

VHDL является языком, нечувствительным к регистру, поэтому объекты с именами Temp1 и TEMP1 будут считаться одним и тем же объектом.

VHDL является языком со строгой типизацией. В частности, это означает, что при попытке присвоить сигналу значение, которое не имеет полного соответствия с типом этого сигнала, компилятор языка будет выдавать ошибку. У данного подхода есть и преимущества, и недостатки. С одной стороны, строгая типизация позволяет не делать глупых ошибок, а с другой – на разработчика ложится дополнительный объем работы, заключающийся в явном приведении типов даже в случаях, которые кажутся очевидными.

#### 1.1.3. Структурное и поведенческое описание цифровой системы

Структурное описание – это описание системы в виде совокупности компонентов и связей между ними. Поведенческое описание – описание системы на уровне зависимости выходов от входов при помощи некоторых процедур. Таким образом, поведенческое описание задает алгоритм, реализуемый системой.

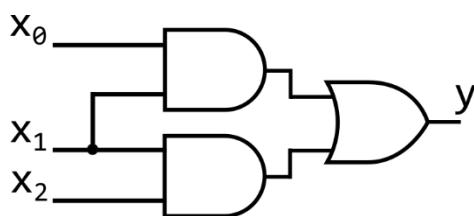

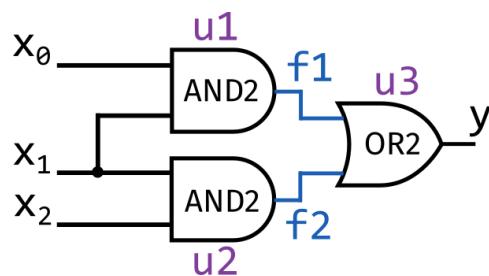

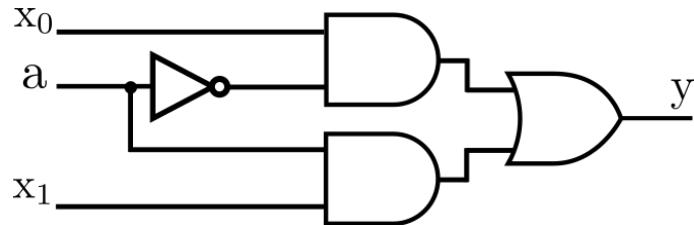

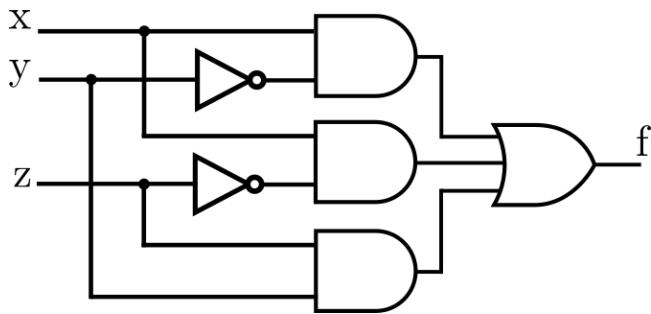

Рассмотрим отличие структурного и поведенческого описания цифровой схемы на примере схемы, показанной на рис. 1.5.

Рис. 1.5. Комбинационная схема

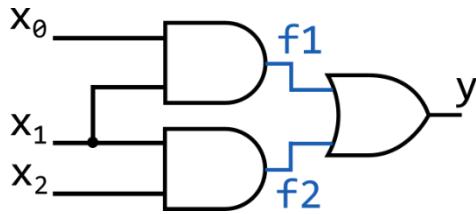

Чтобы составить для данной схемы структурное VHDL-описание, обозначим на ней внутренние сигналы, как показано на рис. 1.6.

Рис. 1.6. Комбинационная схема с обозначением внутренних сигналов

VHDL-описание данной схемы показано в листинге 1.1.

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity device_01 is

port (x: in std_logic_vector(2 downto 0);

y: out std_logic);

end device_01;

architecture Structural of device_01 is

signal f1, f2 : std_logic;

begin

f1 <= x(0) and x(1);

f2 <= x(0) and x(2);

y <= f1 or f2;

end Structural;

```

Листинг 1.1. VHDL-описание комбинационной схемы

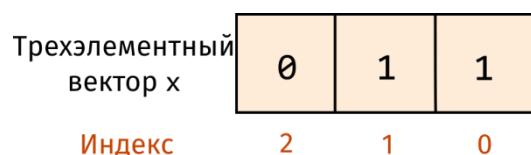

Разберем особенности данного VHDL-описания. Первые две строки нужны, чтобы подключить библиотеку IEEE.STD\_LOGIC\_1164, в которой определен тип std\_logic. Далее следует описание интерфейса схемы, начинающееся с ключевого слова entity. В отличие от предыдущего примера при объявлении входов схемы использован тип std\_logic\_vector, который также содержится в библиотеке STD\_LOGIC\_1164. Как следует из названия, тип std\_logic\_vector является векторным типом данных, причем каждый элемент вектора имеет тип std\_logic. Особенностью std\_logic\_vector является возможность восходящей (to) и нисходящей (downto) индексации элементов вектора. В разбираемом примере объявлен трехэлементный вектор, который имеет нисходящую индексацию элементов, как показано на рис. 1.7.

Рис. 1.7. Вектор с нисходящей индексацией – std\_logic\_vector(2 downto 0)

Таким образом, при использовании нисходящей индексации первый элемент вектора имеет максимальное значение индекса. Восходящая индексация более привычна и напоминает использование обычных одномерных массивов в языках программирования высокого уровня. Пример восходящей индексации показан на рис. 1.8.

|                         |                                                                      |   |   |   |

|-------------------------|----------------------------------------------------------------------|---|---|---|

| Трехэлементный вектор x | <table border="1"> <tr> <td>1</td><td>0</td><td>1</td></tr> </table> | 1 | 0 | 1 |

| 1                       | 0                                                                    | 1 |   |   |

| Индекс                  | 0 1 2                                                                |   |   |   |

Рис. 1.8. Вектор с восходящей индексацией – `std_logic_vector(0 to 2)`

Можно сделать вывод, что тип `std_logic_vector` – это простой способ представления группы сигналов или шины данных. Наличие двух способов индексации обусловлено тем, что в цифровых устройствах данные могут храниться в различном порядке: иногда начальные биты являются старшими (в этом случае удобнее использовать нисходящую индексацию), а иногда начальные биты являются младшими, и в этом случае лучше подойдет восходящая индексация. Нисходящий порядок разрядов называется *little-endian* (т. е. «оканчивающийся на младший»). Восходящая индексация описывает порядок бит, называемый *big-endian* (т. е. «оканчивающийся на старший»), поскольку младший бит имеет наибольшее значение индекса.

Вернемся к рассматриваемому примеру (см. листинг 1.1). После объявления для `device_01` архитектуры с именем `Structural` следует объявление внутренних сигналов схемы, которое начинается с ключевого слова `signal`. В данном случае внутренними являются два сигнала с именами `f1` и `f2`, имеющие тип `std_logic`. Непосредственно схема, показанная на рис. 1.6, описывается тремя строками VHDL-кода.

```

f1 <= x(0) and x(1);

f2 <= x(0) and x(2);

y <= f1 or f2;

```

Каждая строка, по сути, отражает работу одного логического вентиля. Таким образом, полученное VHDL-описание можно считать примером структурного описания, поскольку операторы языка использованы для описания структуры цифровой схемы. Список логических операций языка VHDL шире, чем использованные выше `and` и `or`, полный их перечень приведен в табл. 1.1.

VHDL не определяет соотношение приоритетов логических операций (`and`, `or` и т. д.), поэтому при записи логических выражений нужно всегда использовать скобки.

Таблица 1.1

Логические операторы VHDL

| Операция | Значение           |

|----------|--------------------|

| and      | Операция И         |

| or       | Операция ИЛИ       |

| nand     | Операция И-НЕ      |

| nor      | Операция ИЛИ-НЕ    |

| xor      | Исключающее ИЛИ    |

| xnor     | Исключающее ИЛИ-НЕ |

Рассматриваемая схема (см. рис. 1.6) может также быть описана с использованием поведенческого стиля. Ниже приведен вариант такого описания.

```

entity device_01 is

port (x: in std_logic_vector(2 downto 0);

y: out std_logic);

end device_01;

architecture Behavioral of device_01 is

begin

process (x) begin

if (x(0)='1') and (x(1)='1') then

y <= '1';

elsif (x(0)='1') and (x(2)='1') then

y <= '1';

else

y <= '0';

end if;

end process;

end Behavioral;

```

Перед тем как приступить к анализу приведенного VHDL-описания, следует заметить, что здесь использованы операторы языка, которые ранее не упоминались. В частности, речь идет об операторе `process`. Формально данный оператор имеет следующий синтаксис.

```

<имя процесса>: process([<список сигналов активации>])

[<область объявления>]

begin

<последовательные операторы>

end process <имя процесса>;

```

Процесс является языковой конструкцией языка VHDL, которая используется для описания функциональных блоков, работающих параллельно. Концепция процесса полностью соответствует логике работы цифровых устройств, в которых внешние сигналы могут поступать сразу на несколько внутренних блоков и обрабатываться параллельно. При помощи оператора `process` можно описывать как комбинационные, так и последовательностные схемы.

Как видно из описания, после ключевого слова `process` указывается список сигналов, которые переводят данный процесс в активное состояние. Часто его называют *списком чувствительности* процесса. Важно уяснить, что несмотря на то, что процесс сам по себе является параллельным оператором, действия внутри процесса выполняются последовательно. То есть внутри процесса описывается логика получения выходных сигналов после того, как входные сигналы из списка чувствительности изменились.

Вернемся к архитектуре `Behavioral` модуля `device_01`. Вся логика работы устройства описана внутри одного процесса. В качестве списка чувствительности указан вектор `x`, поскольку выход схемы у зависит от всех компонентов вектора. В первой ветке условного оператора проверяется одновременное равенство единице сигнала `x(0)` и `x(1)`, во второй ветке проверяется на равенство единице `x(0)` и `x(2)`. В обоих случаях выходу схемы у присваивается значение единицы. Данные условия можно было проверить, используя только одну ветку оператора `if`, однако это снизило бы наглядность кода. Если условия установки у в единицу не выполняются, то у устанавливается в нуль.

Таким образом, поведенческое описание лучше выражает логику работы устройства, чем структурное, и поэтому чаще применяется на практике.

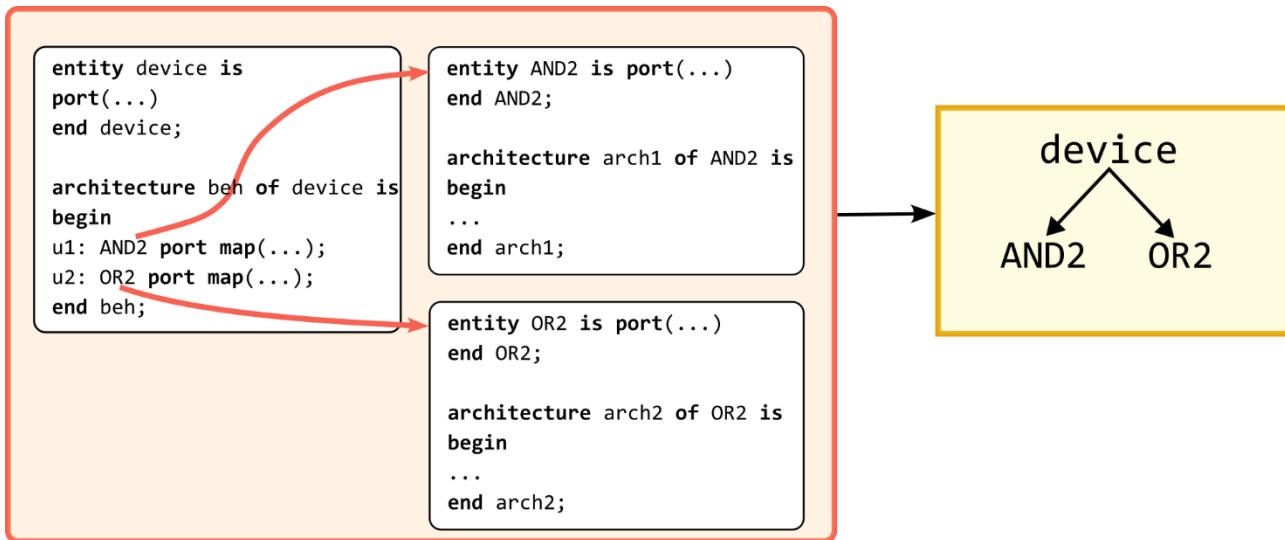

#### 1.1.4. Иерархическое описание проекта

Важной особенностью VHDL является возможность иерархического описания проекта. Это означает, что можно составить VHDL-описание отдельных блоков (модулей) проекта, а затем объединить их в схему верхнего уровня. Для вставки модуля нижнего уровня в модуль верхнего уровня используется языковая конструкция создания экземпляра (англ. *instantiation*). На рис. 1.9 показана иерархическая структура проекта из нескольких модулей.

Рассмотрим опять устройство, показанное на рис. 1.6. В его состав входят вентили И и ИЛИ, которые можно описать в виде VHDL-модулей, как показано в листинге 1.2.

Рис. 1.9. Иерархическое описание VHDL-проекта

|                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre> library IEEE; use IEEE.STD_LOGIC_1164.ALL;  entity AND2 is   Port (a : in STD_LOGIC;         b : in STD_LOGIC;         c : out STD_LOGIC); end AND2;  architecture arch1 of AND2 is begin   c &lt;= a and b; end arch1; </pre> | <pre> library IEEE; use IEEE.STD_LOGIC_1164.ALL;  entity OR2 is   Port (a : in STD_LOGIC;         b : in STD_LOGIC;         c : out STD_LOGIC); end OR2;  architecture arch2 of OR2 is begin   c &lt;= a or b; end arch2; </pre> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Листинг 1.2. VHDL-описание базовых вентилей И и ИЛИ

Дополним схему на рис. 1.6, введя в нее обозначение вентилей и их метки (рис. 1.10).

Рис. 1.10. Схема устройства с обозначением связей и модулей

Ниже приводится VHDL-описание схемы, представленной на рис. 1.10.

```

entity device_01 is

port (x: in std_logic_vector(2 downto 0);

y: out std_logic);

end device_01;

architecture Beh3 of device_01 is

component AND2 port (a : in STD_LOGIC;

b : in STD_LOGIC;

c : out STD_LOGIC);

end component;

component OR2 port (a : in STD_LOGIC;

b : in STD_LOGIC;

c : out STD_LOGIC);

end component;

signal f1, f2 : std_logic;

begin

u1: AND2 port map(a=>x(0), b=>x(1), c=>f1);

u2: AND2 port map(a=>x(0), b=>x(2), c=>f2);

u3: OR2 port map(a=>f1, b=>f2, c=>y);

end Beh3;

```

В отличие от предыдущих примеров в данном VHDL-коде внутри архитектуры имеется декларация компонентов, которые впоследствии будут использованы. В нашем случае объявляются компоненты AND2 и OR2, которые были описаны ранее. Файлы с описанием компонентов должны находиться в одном каталоге с описанием модуля верхнего уровня. Компоненты, используемые при описании архитектуры, должны быть описаны в области объявления архитектуры. В общем случае описание компонента имеет следующий вид.

```

component <имя модуля>

generic(<список параметров>);

port(<список портов>);

end <имя модуля>;

```

Список параметров `generic` и список портов `port` должны соответствовать описаниям `generic` и `port` соответствующего модуля.

Для использования компонента внутри архитектуры ему необходимо присвоить уникальное имя и назначить портам компонента сигналы. Создание экземпляра компонента осуществляется оператором `port map`, который имеет следующий синтаксис.

```

<уникальное имя компонента> : <имя интерфейса>

port map (<список сигналов>);

```

Список сигналов связывает сигналы описываемого устройства с портами компонента. В рассматриваемом примере экземпляр вентиля OR2 создается следующим образом.

```

u3: OR2 port map(a=>f1, b=>f2, c=>y);

```

Здесь u3 – это уникальное имя экземпляра компонента внутри проекта.

Есть два варианта описания списка сигналов в операторе **port map**: позиционное соответствие и явное соответствие. Рассмотрим их на примере компонента u1:

1) явное соответствие.

```

u1: AND2 port map(a=>x(0), b=>x(1), c=>f1);

```

При явном соответствии порт компонента связывается с сигналом с помощью оператора **=>**, при этом назначать сигналы можно в произвольном порядке, как показано в следующем примере.

```

u1: AND2 port map(c=>f1, b=>x(1), a=>x(0));

```

2) позиционное соответствие означает, что сигналы назначаются в том порядке, в котором они были объявлены в интерфейсе схемы. Пример позиционного соответствия приведен ниже.

```

u1: AND2 port map(x(0), x(1), f1);

```

В данном примере сигнал **x(0)** путем позиционного соответствия будет связан с портом **a**, **x(1)** с портом **b**, а **f1** с портом **c**. Обычно разработчики советуют не использовать позиционное назначение, поскольку данный способ потенциально может приводить к трудно выявляемым ошибкам. Представьте себе, что в процессе проектирования вы изменили порядок объявления портом в схеме нижнего уровня. В этом случае ошибки в модуле верхнего уровня не возникнет, хотя логика работы устройства может стать неверной.

### *Непосредственное создание экземпляра*

Помимо описанного выше, есть упрощенный вариант создания иерархического VHDL-описания проекта – через непосредственное указание интерфейса (**entity**) и имени архитектуры компонентов схемы. Пример такого стиля описания схемы, изображенной на рис. 1.10, приведен ниже (листинг 1.3).

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity device_01 is

port (x: in std_logic_vector(2 downto 0);

y: out std_logic);

end device_01;

architecture Beh4 of device_01 is

signal f1, f2 : std_logic;

begin

u1: entity work.AND2(arch1) port map(a=>x(0), b=>x(1), c=>f1);

u2: entity work.AND2(arch1) port map(a=>x(0), b=>x(2), c=>f2);

u3: entity work.OR2(arch2) port map(a=>f1, b=>f2, c=>y);

end Beh4;

```

Листинг 1.3. VHDL-описание схемы устройства с использованием механизма непосредственного создания экземпляров модулей

Данное описание отличается в первую очередь тем, что здесь нет секции с описанием компонентов схемы (ключевое слово `component` не используется). При создании экземпляра каждого вентиля мы указываем его метку, после чего используем ключевое слово `entity`, чтобы показать, что мы хотим использовать *непосредственное создание экземпляра*. После этого мы специфицируем модуль, указывая библиотеку и название интерфейса и архитектуры. Пример в следующем фрагменте.

```

u1: entity work.AND2(arch1) port map(a=>x(0), b=>x(1), c=>f1);

```

Здесь `work` – это название библиотеки (в данном случае это текущая рабочая библиотека проекта); `AND2` – название интерфейса схемы; `arch1` – название архитектуры. Указывать название архитектуры необязательно, но ее указание может помочь избежать досадных ошибок в тех случаях, когда для одного интерфейса есть несколько архитектур. Если явно не указать конкретную архитектуру, то в проекте будет использоваться последняя скомпилированная архитектура.

### ***Сравнение компонентного и непосредственного создания экземпляра объекта***

Описание компонента полностью соответствует интерфейсу (`entity`) модуля, экземпляр которого вы хотите создать. Если в ходе разработки возникнет необходимость изменить интерфейс модуля, нужно будет внести изменения в трех местах проекта: в интерфейсе модуля, в объявлении компонента и в экземпляре.

Кроме того, при использовании компонентного способа создания экземпляра нет простого способа указать, какую именно архитектуру необходимо использовать. Если в проекте есть две или более архитектуры для данного модуля, то будет задействована последняя скомпилированная архитектура.

По этим причинам компонентный способ создания экземпляра модуля уступает непосредственному способу. Тем не менее существует один очень важный случай, когда компонентный способ необходим. Он используется в том случае, когда проект имеет смешанное описание (например, используются два языка: VHDL и Verilog). В этом случае, если модуль, который необходимо подключить, написан на Verilog, сделать это можно, только используя компонентный способ создания экземпляра объекта.

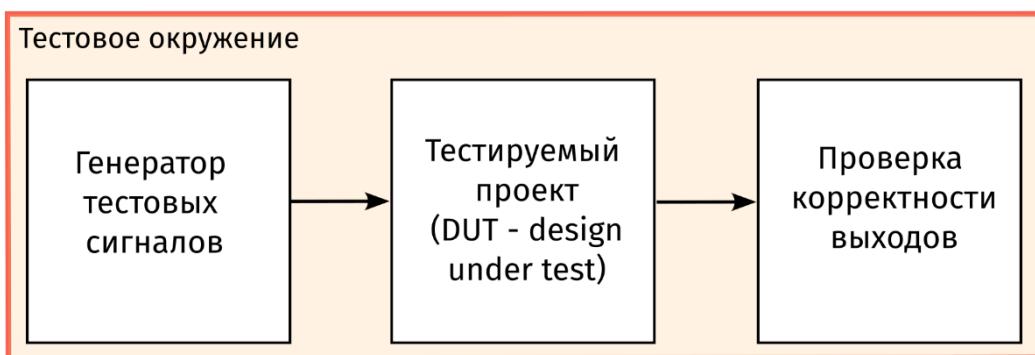

### 1.1.5. Тестовое окружение VHDL-проекта

Важной частью процесса разработки цифрового устройства является его тестирование. Полученные в процессе проектирования VHDL-описания требуют проверки правильности описываемой ими логики работы устройства.

Чтобы проверить корректность VHDL-описания некоторой цифровой схемы на языке VHDL, обычно проводят моделирование и получают временные диаграммы для всех сигналов схемы. Задачей разработчика в данном случае становится написание так называемого *тестового окружения* (англ. *testbench*). Под тестовым окружением понимается VHDL-код, который позволяет генерировать сигналы, необходимые для проверки корректности полученного VHDL-описания устройства. При написании теста может быть использовано как синтезируемое, так и несинтезируемое подмножество языка VHDL, поскольку тест не предназначен для отображения на аппаратуру.

Следующая диаграмма (рис. 1.11) отражает типичную структуру простого тестового окружения.

Рис. 1.11. Структура тестового окружения

Блок генератора тестовых сигналов формирует входные данные для тестируемого проекта, а отдельный блок проверяет корректность выходных данных.

Для крупных проектов генератор тестовых сигналов и средство проверки выходных данных могут находиться в отдельных файлах. Для небольших проектов разумно описывать все эти блоки в одном файле.

Блок проверки корректности вывода необходим в тех случаях, когда на передний план выходит автоматизация процесса тестирования крупных проектов. В более простом варианте он не используется, поскольку добавляет ненужной сложности. Вместо этого можно воспользоваться программой-симулятором, которая позволяет непосредственно просматривать временную форму входных/выходных сигналов. Например, в САПР Vivado (Xilinx) есть встроенное средство построения временных диаграмм сигналов.

### *Временное моделирование*

Для моделирования процессов, происходящих во времени, в VHDL используется встроенный тип данных `time`.

```

type time is range 0 to 1E20

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

s = 1000 ms;

min = 60 s;

hr = 60 min;

end units;

```

Определяя в тесте временной интервал с использованием типа `time`, необходимо указать как значение, так и единицу времени. По умолчанию минимальное временное разрешение равно 1 fs (одна фемтосекунда, или  $10^{-15}$  с).

Ключевое слово `after` используется в VHDL для присвоения сигналам значения в указанное время в будущем. Оператор `after` можно использовать в параллельных операторах или в процессах.

Приведенный ниже фрагмент кода на VHDL показывает синтаксис оператора `after`.

```

<signal> <= [<initial_value>,<end_value> after <time>];

```

Первая часть назначения, которая стоит перед запятой, относительно проста для понимания, поскольку `<signal> <= <initial_value>` соответствует обычному назначению сигналов. Вторая часть кода представляет собой планирование дальнейшего обновления сигнала (значением `<end_value>`) спустя указанный интервал времени (`<time>`). Переменная `<time>` должна иметь тип `time`, который был описан

выше. Оператор `after` часто используется в VHDL для сброса ПЛИС в начале моделирования, как показано в следующем примере.

```

reset <= '1', '0' after 1 us;

```

В начальный момент времени сигнал `reset` переводится в активное состояние ('1'). Далее при помощи оператора `after` выполняется планирование (англ. *schedule*) перехода сигнала в неактивное состояние ('0') после 1 мкс модельного времени.

Также можно использовать оператор `after` без задания начального значения. Этот подход используется для планирования постоянных изменений состояния сигнала. Это полезно при генерации, например, тактовых сигналов, поскольку сигнал может инвертироваться с фиксированными интервалами. В приведенном ниже фрагменте кода показан базовый метод генерации тактовых сигналов в VHDL-тесте.

```

clock <= not clock after 10 ns;

```

Здесь 10 нс составляют половину периода тактового сигнала `clock`.

### ***Написание теста***

Первым шагом при написании тестового окружения является создание модуля VHDL, который выступает в качестве контейнера. Данный контейнер не имеет входных и выходных данных (см. рис. 1.11), поэтому при его описании входные и выходные порты отсутствуют, как показано в следующем фрагменте кода.

```

entity test_bench is

end test_bench;

architecture test of example_tb is

...

end architecture example_tb;

```

Архитектура тестового окружения должна содержать экземпляр тестируемого проекта (англ. *design under test – DUT*). Для создания экземпляра необходимо использовать те же языковые конструкции, что и при иерархическом описании проекта. Это означает, что можно создать экземпляр тестируемого модуля, используя либо оператор `component`, либо синтаксис непосредственного создания экземпляра. Таким образом, вторым шагом в написании теста является создание экземпляра тестируемого модуля. Для описанного ранее нами модуля `device_01` (см. листинг 1.3) этот шаг будет выглядеть следующим образом

```

DUT: entity work.device_01(Beh4) port map (x=>test_x, y=>test_y);

```

На заключительном шаге создания тестового окружения описывается генерация тестовых сигналов. В нашем случае, чтобы протестировать схему, нужно сгенерировать все восемь возможных двоичных комбинаций. Для этого мы присваиваем входным данным значение, а затем используем оператор `wait`, чтобы обеспечить задержку на заданный интервал времени. Следующий фрагмент кода иллюстрирует изложенные идеи.

```

stimulus: process

begin

wait for 100ns;

test_x <= "000";

wait for 10ns;

test_x <= "001";

wait for 10ns;

test_x <= "010";

wait for 10ns;

test_x <= "011";

wait for 10ns;

test_x <= "100";

wait for 10ns;

test_x <= "101";

wait for 10ns;

test_x <= "110";

wait for 10ns;

test_x <= "111";

wait for 10ns;

end process stimulus;

```

Целиком VHDL-файл тестового окружения проекта приведен в листинге 1.4.

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity device_01_tb is

end device_01_tb;

architecture Behavioral of device_01_tb is

signal test_x: std_logic_vector(2 downto 0);

signal test_y: std_logic;

begin

DUT: entity work.device_01(Beh4) port map (x=>test_x, y=>test_y);

stimulus: process

begin

```

```

wait for 100ns;

test_x <= "000";

wait for 10ns;

test_x <= "001";

wait for 10ns;

test_x <= "010";

wait for 10ns;

test_x <= "011";

wait for 10ns;

test_x <= "100";

wait for 10ns;

test_x <= "101";

wait for 10ns;

test_x <= "110";

wait for 10ns;

end process stimulus;

```

Листинг 1.4. VHDL-описание тестового окружения

### 1.1.6. Маршрут моделирования цифрового устройства в САПР Vivado

В данном подразделе будет кратко рассмотрен общий маршрут моделирования цифрового устройства в САПР Vivado. Будут рассмотрены этапы разработки VHDL-описания устройства, создания тестового окружения, а также получения временных диаграмм работы устройства.

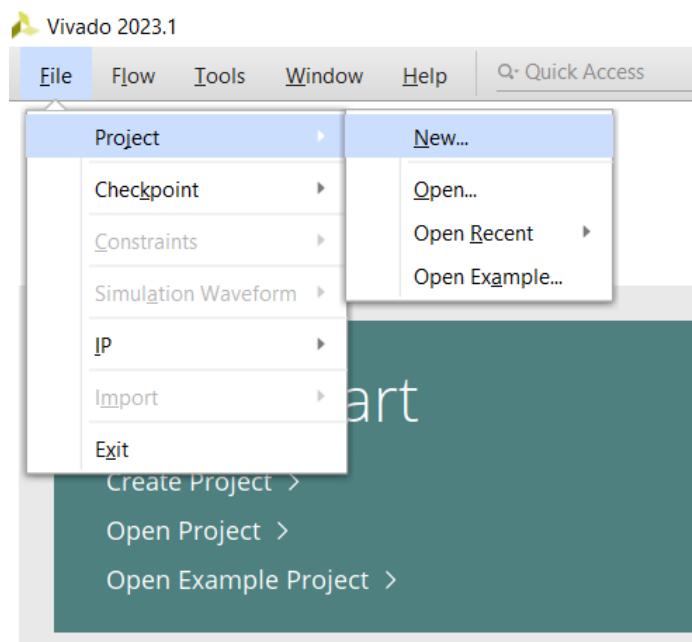

Чтобы создать проект в Vivado, после запуска необходимо выполнить в меню команду **File -> Project -> New**, как показано на рис. 1.12.

Рис. 1.12. Запуск процесса создания проекта в Vivado

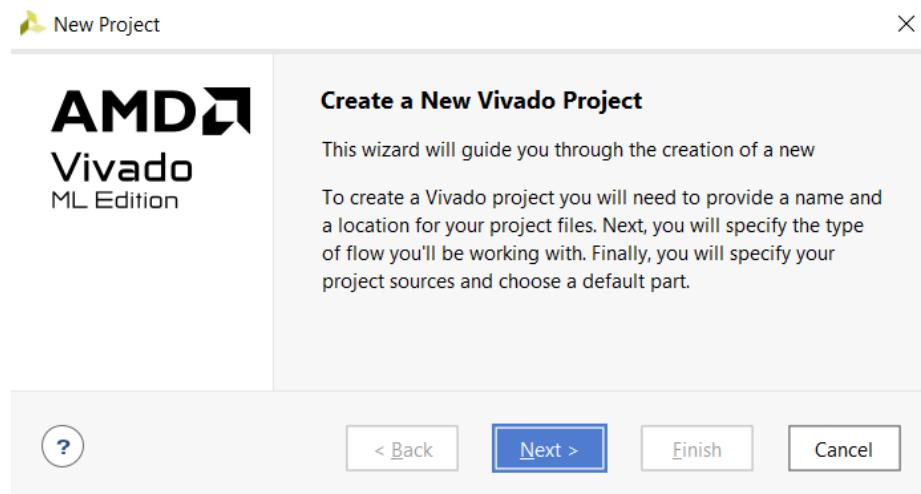

После этого на экране появится окно мастера (*wizard*) для создания проекта в Vivado (рис. 1.13). Чтобы продолжить процесс, необходимо нажать **Next**.

Рис. 1.13. Приветствие мастера по созданию проекта в Vivado

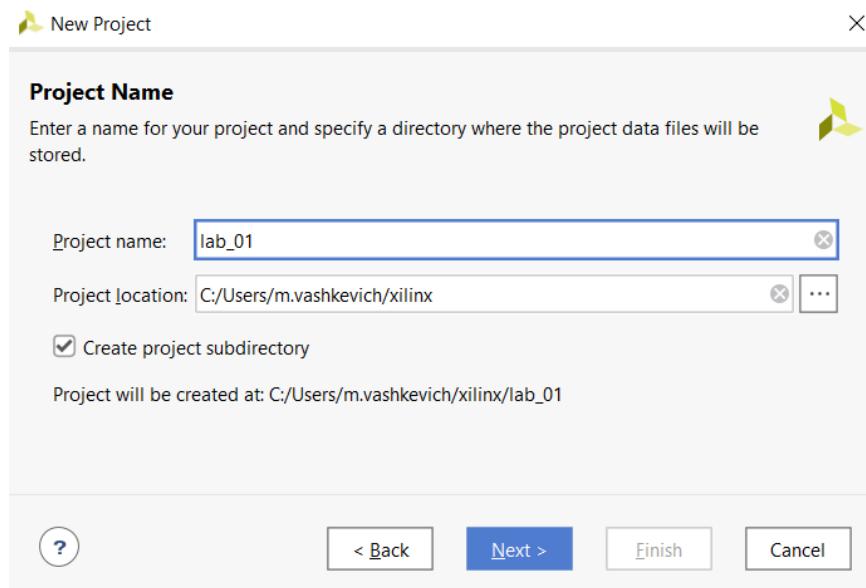

В появившемся окне мастера (рис. 1.14) необходимо ввести имя проекта (в данном случае это *lab\_01*), а также при необходимости задать директорию на диске для хранения проекта. По завершении данных действий необходимо нажать *Next*.

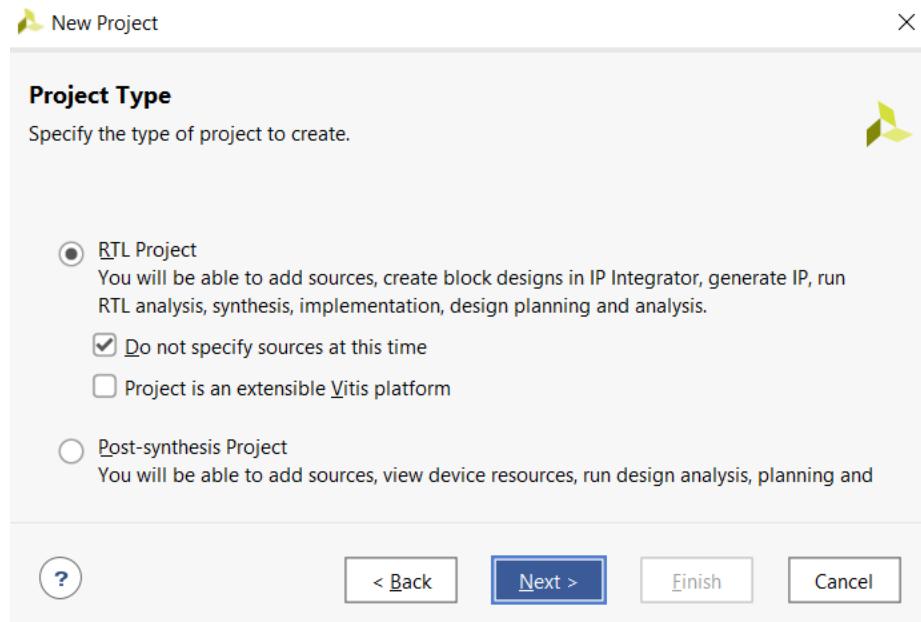

В следующем окне мастера (рис. 1.15) будет предложено выбрать тип проекта: *RTL*-проект либо *Post-synthesis* проект. В большинстве случаев проекты описываются на уровне регистровых передач (*register transfer level – RTL*). Создаваемое в рамках лабораторной работы описание также относится к *RTL*-проекту. Если установить флаг *Do not specify sources at this time*, то Vivado пропустит этап добавления исходных файлов к проекту.

Рис. 1.14. Задание имени и папки проекта

Опция *Post-synthesis* проекта относится к тому случаю, когда исходное HDL-описание получено в результате работы сторонней программы-синтезатора, а главная цель проекта состоит в анализе аппаратных затрат ПЛИС, необходимых для реализации проекта.

Рис. 1.15. Выбор типа проекта

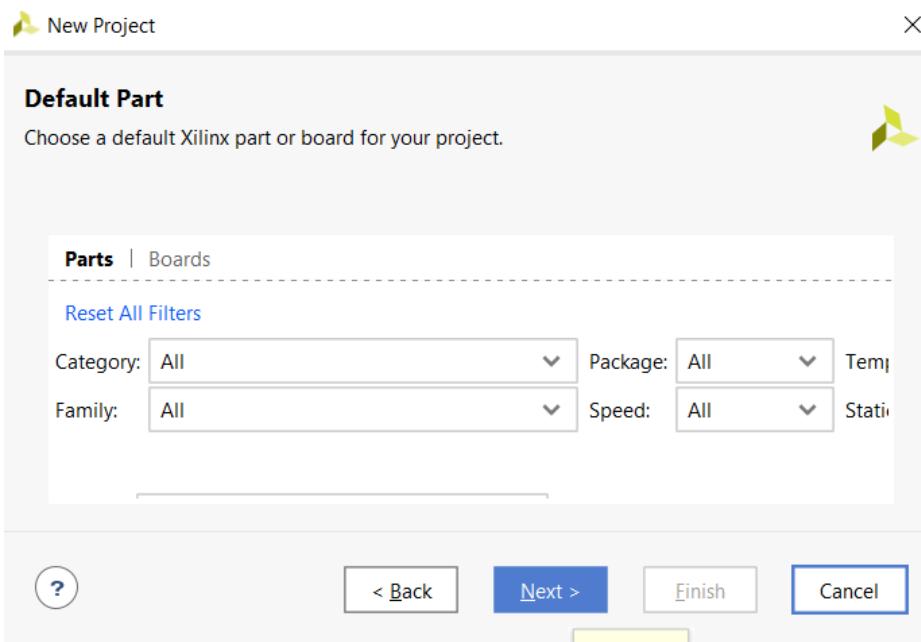

Далее мастер создания проектов предложит выбрать конкретную микросхему ПЛИС либо целевую отладочную плату, для которой создается проект (рис. 1.16). В рассматриваемом случае никаких требований к аппаратной платформе нет, поэтому можно нажать Next и перейти к следующему этапу.

Рис. 1.16. Выбор аппаратной платформы

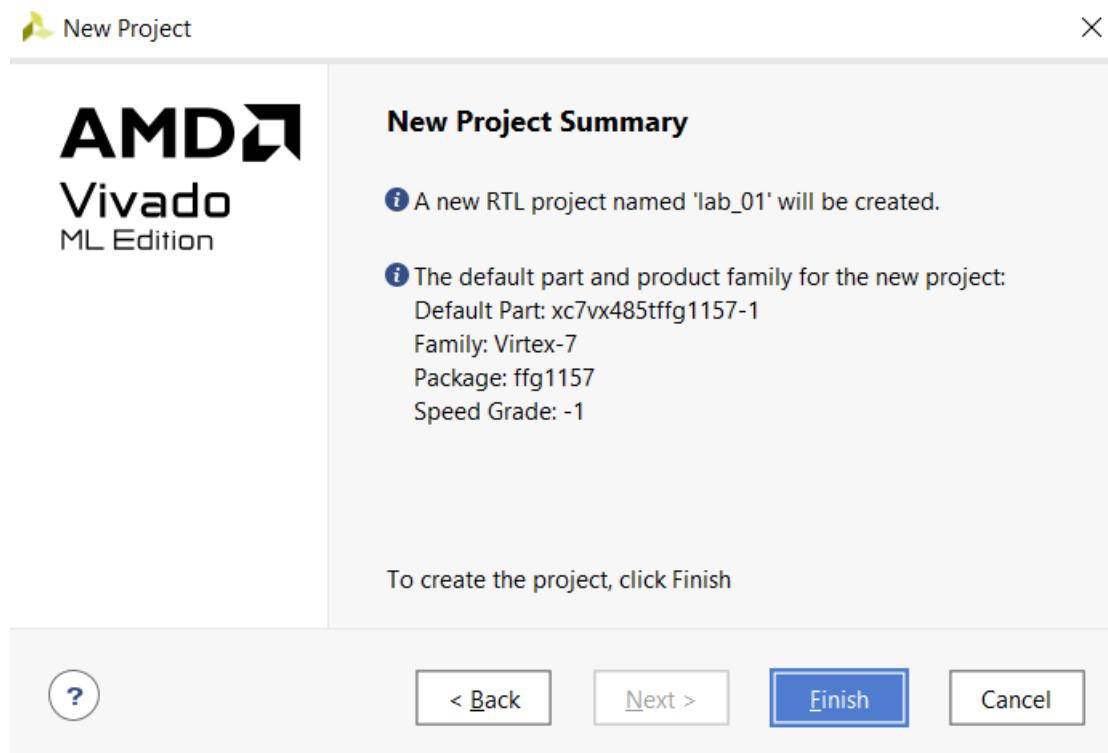

На заключительном этапе будет показано окно-уведомление (рис. 1.17) об окончании процесса создания проекта. В окне отображается название проекта, его тип, а также параметры аппаратной платформы, выбранные по умолчанию.

Рис. 1.17. Окно-уведомление об окончании процесса создания проекта

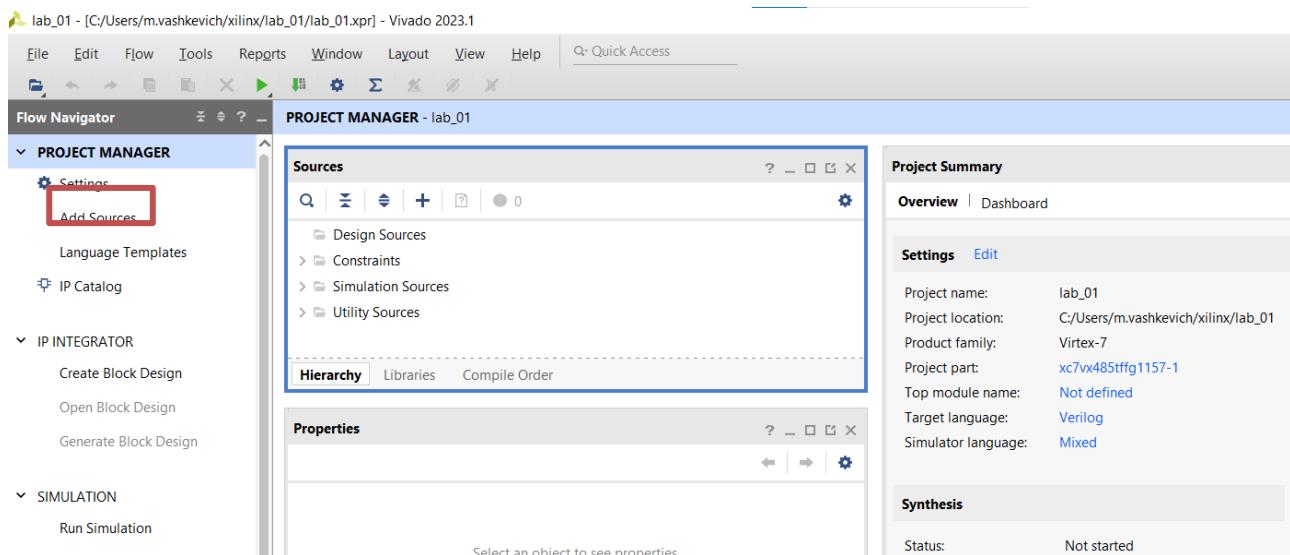

После окончания работы мастера откроется окно Vivado с проектом. Следующим этапом в создании проекта является добавление исходных файлов. Для этой цели в окне менеджера проекта необходимо выбрать пункт **Add Sources** (рис. 1.18).

Рис. 1.18. Окно проекта Vivado

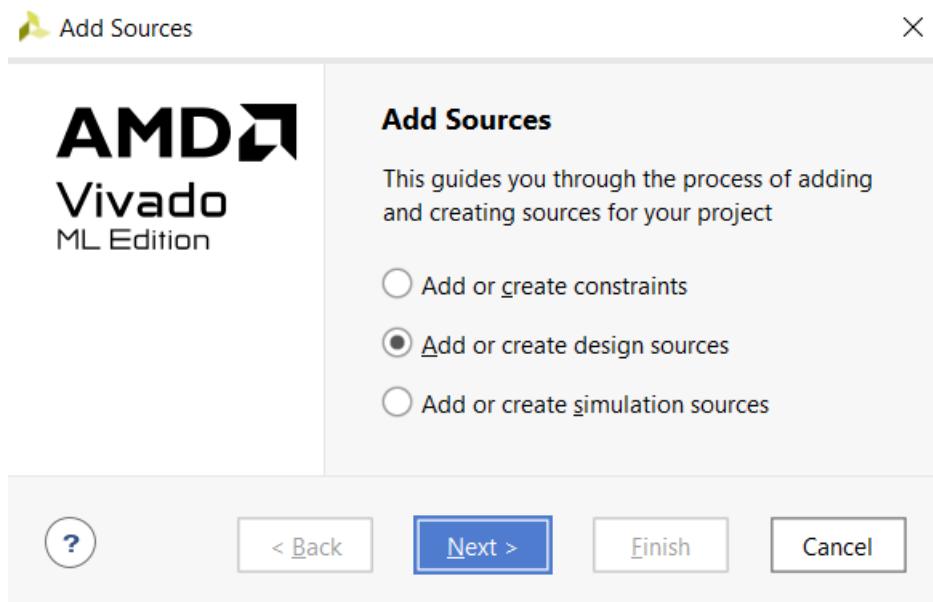

При этом на экране появится мастер добавления исходных файлов (рис. 1.19), в котором пользователю предлагается выбрать тип добавляемого исходного файла. Это может быть файл с ограничениями, исходный файл с описанием проекта на языках HDL либо файл, содержащий тест. С последними двумя типами мы уже познакомились выше. Файл с ограничениями (*constraints*) имеет важное значение на этапе создания загрузочного файла для FPGA. В нем, помимо прочего, описывается соответствие между портами разработанного устройства и выводами FPGA. На начальном этапе добавлять файл с ограничениями к проекту не нужно.

Рис. 1.19. Окно добавления исходных файлов

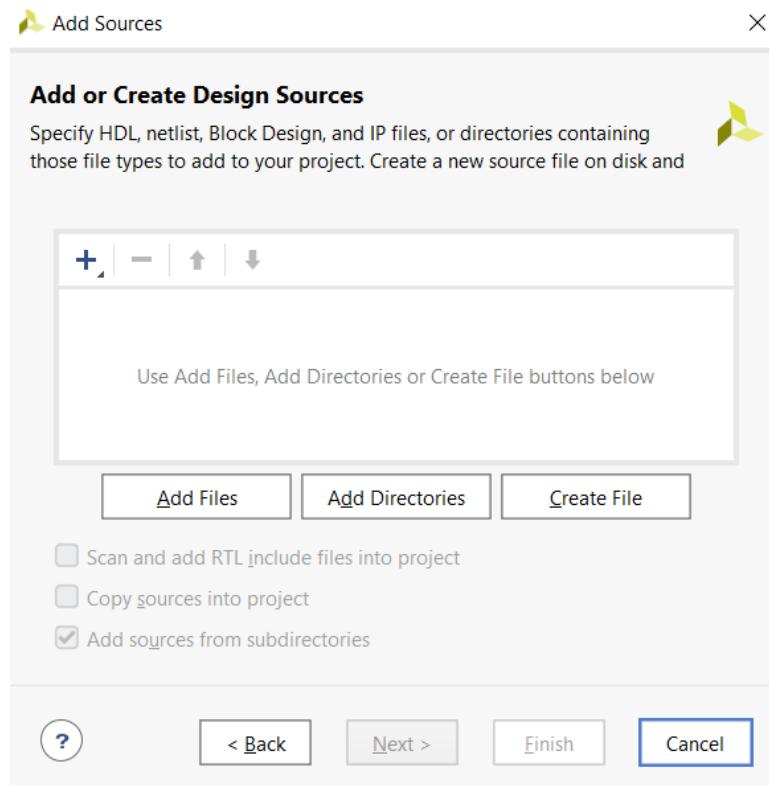

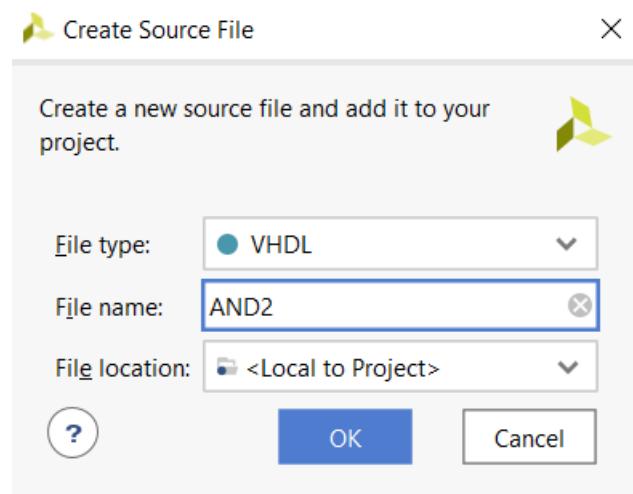

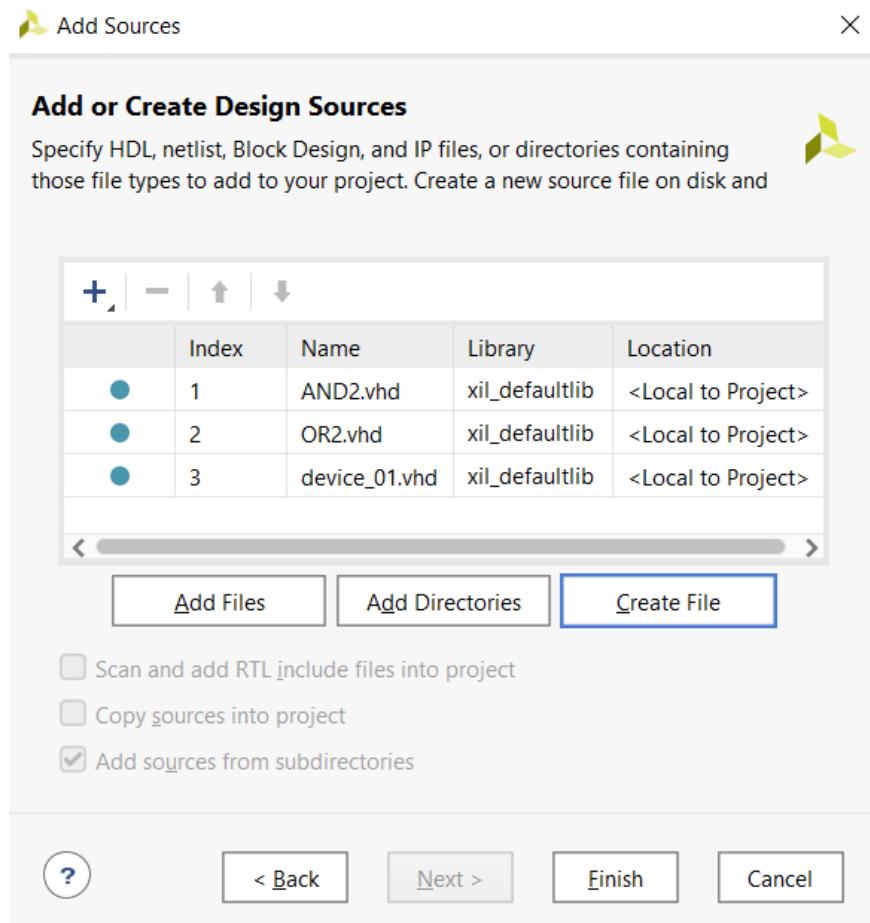

Для выполнения начального этапа разработки цифрового устройства необходимо добавить исходные файлы проекта (*design sources*), которые будут описывать все его блоки. Для этого нужно выбрать пункт *Add or create design sources* в окне добавления исходных файлов (см. рис. 1.19). После этого появится окно (рис. 1.20), в котором будет предложено добавить или создать исходные файлы проекта. Если необходимо добавить уже существующие файлы, то для этого нужно нажать кнопку *Add Files* и указать их место расположения. Если файлы необходимо создать (как в рассматриваемом случае), нужно нажать кнопку *Create File*. Далее появится окно *Create Source File*, в котором будет предложено выбрать тип файла (VHDL, Verilog, SystemVerilog), имя файла и каталог для хранения файла. В данном случае выбираем тип файла VHDL, а имя – AND2 (рис. 1.21). Аналогичным образом необходимо создать VHDL-файлы с именами OR2 и device\_01. По окончании этого действия окно должно выглядеть, как показано на рис. 1.22.

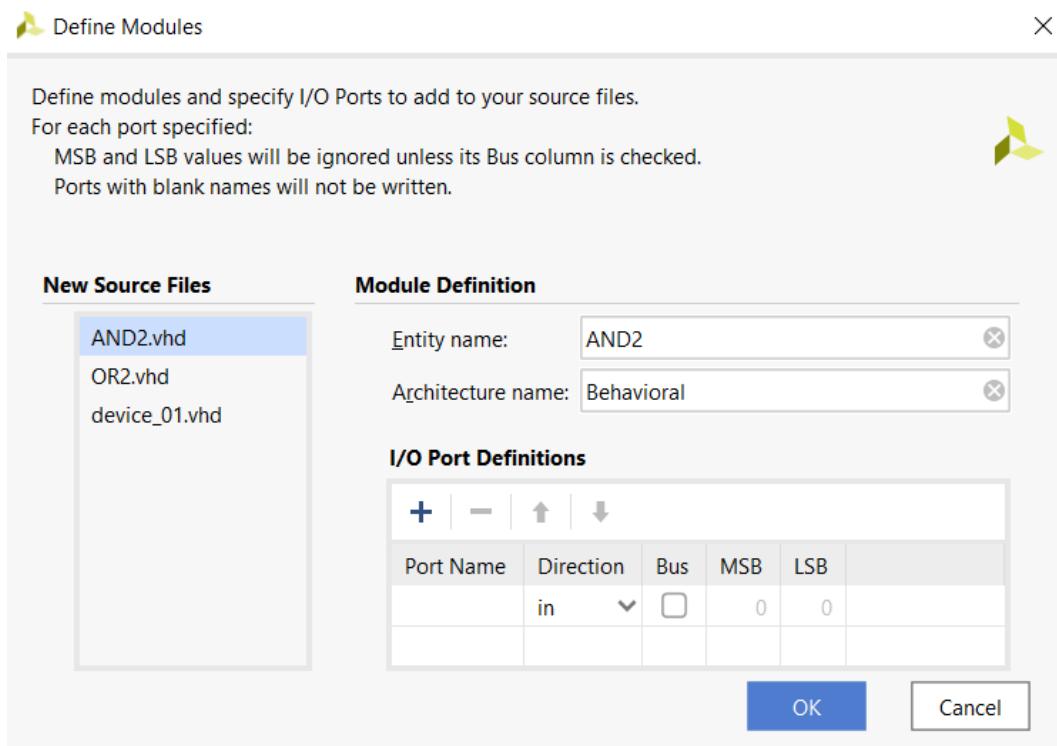

Далее мастер добавления исходных файлов предложит определить при помощи графического интерфейса входные и выходные порты модулей, а также их разрядность (рис. 1.23). Данный шаг можно пропустить, поскольку порты удобнее определять непосредственно в VHDL-коде.

Рис. 1.20. Окно добавления/создания исходных файлов проекта

Рис. 1.21. Окно создания файла с описанием модуля AND2

Рис. 1.22. Вид окна проекта после добавления исходных файлов проекта

Рис. 1.23. Окно для задания портов модуля

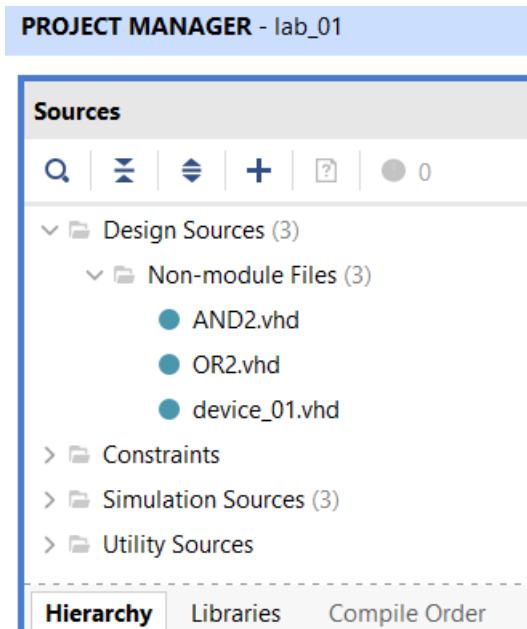

После выполнения указанных действий в окне исходных файлов менеджера проектов должны отобразиться три новых исходных файла (рис. 1.24).

Рис. 1.24. Окно менеджера проекта

В проектные файлы AND2.vhd и OR2.vhd необходимо поместить описание вентилей, приведенное в листинге 1.2. В проектный файл device\_01.vhd нужно поместить описание, приведенное в листинге 1.3. На этом завершается процесс описания схемы устройства.

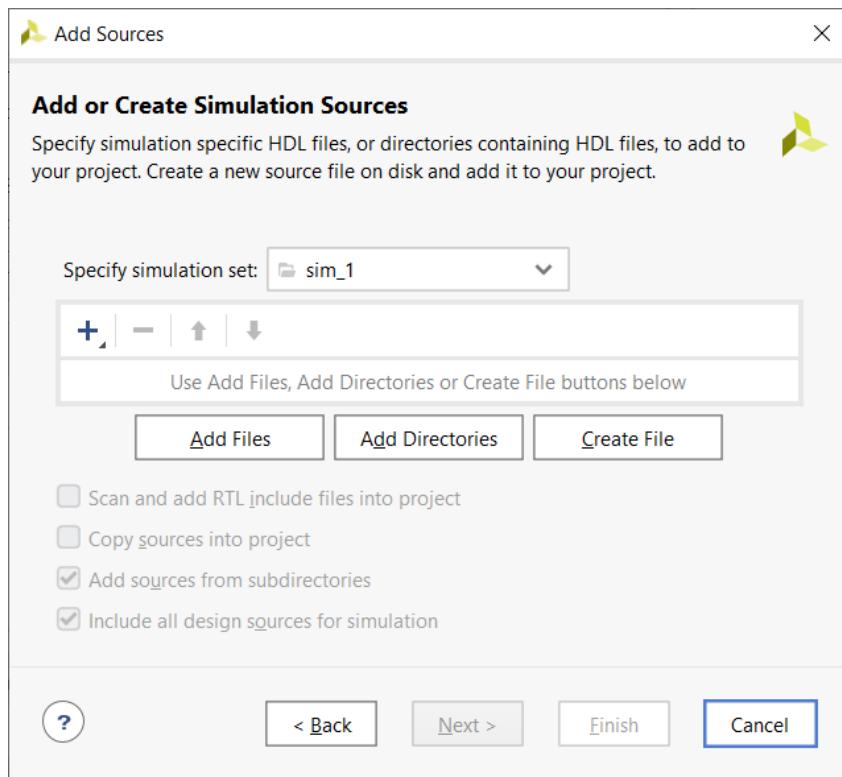

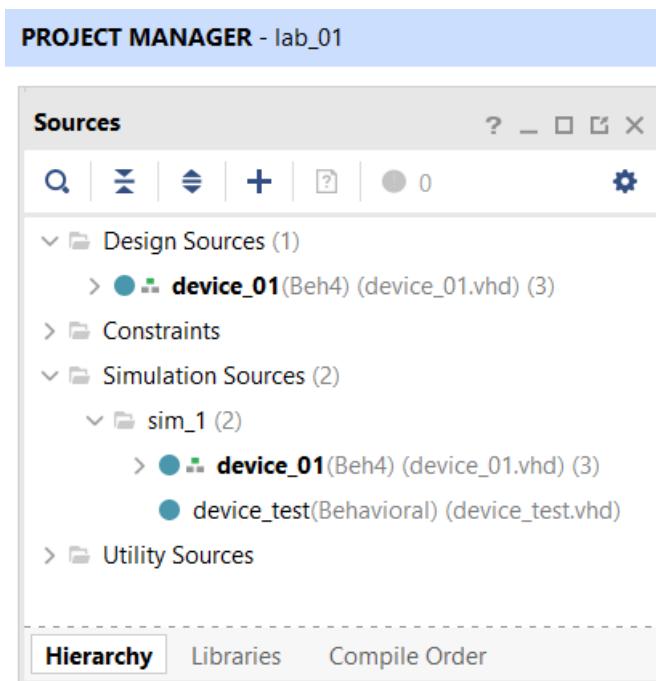

Следующим этапом является тестирование проекта. Для этого необходимо к проекту добавить vhdl-файл с описанием теста. Для этого в окне менеджера проекта выбираем пункт Add Sources (см. рис. 1.18). Далее в появившемся окне (см. рис. 1.19) выбираем пункт Add or create simulation sources (создать или добавить файл для симуляции). В появившемся окне (рис. 1.25) нажимаем кнопку Create File, задаем имя файла (например, device\_test.vhd), после чего нажимаем кнопку Finish для завершения процесса добавления тестовых файлов проекта. Vivado предложит определить входные и выходные порты создаваемого модуля (см. рис. 1.23), однако модуль, описывающий тест, не имеет входных и выходных портов, поэтому это действие можно пропустить. После окончания указанных действий в менеджере проектов в окне Sources в разделе Simulation Sources должен появиться файл device\_test.vhd (рис. 1.26).

Для завершения процесса создания тестового окружения необходимо в файл device\_test поместить описание теста, приведенное в листинге 1.4.

Рис. 1.25. Окно создания исходного файла с тестом

Рис. 1.26. Исходный файл с тестом (device\_test.vhd)

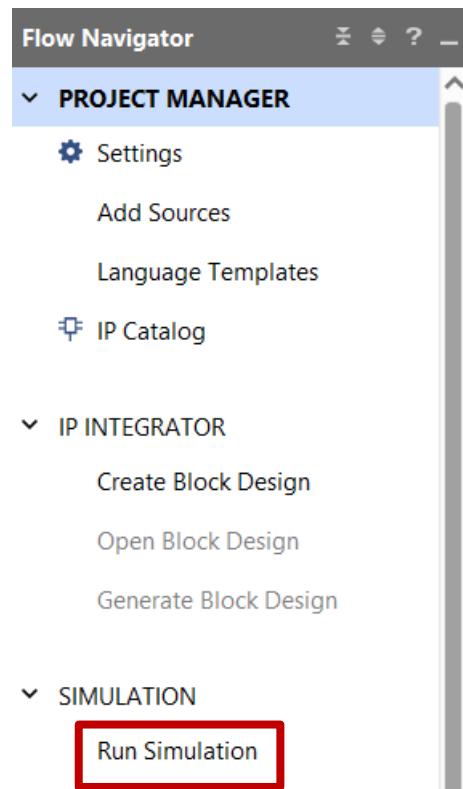

Далее для запуска процесса моделирования необходимо на панели Flow Navigator выбрать пункт Run Simulation, как показано на рис. 1.27. После этого нужно выбрать первый появившийся пункт Run Behavioral Simulation.

Рис. 1.27. Запуск процесса моделирования

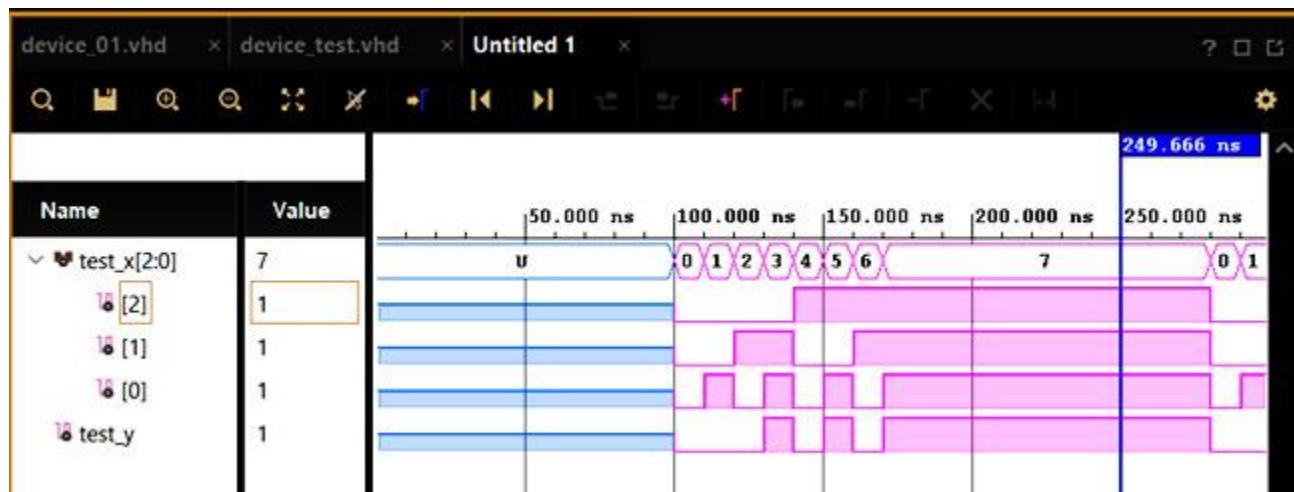

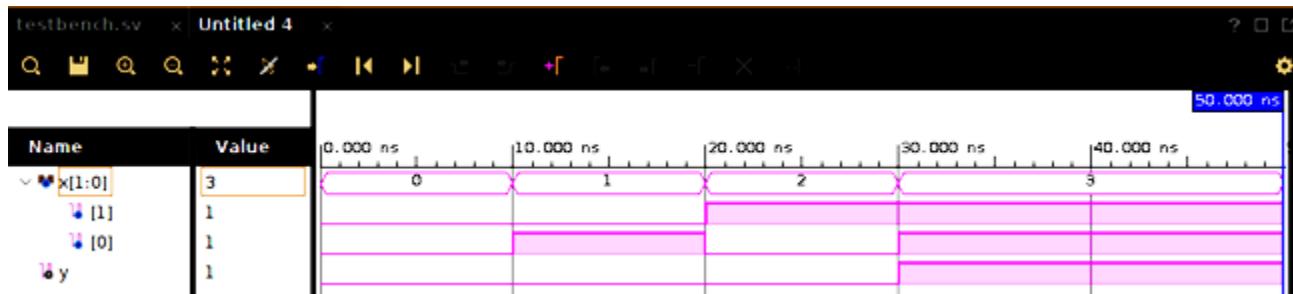

В результате на экране появится окно с временной диаграммой теста, как показано на рис. 1.28.

Рис. 1.28. Временная диаграмма теста

Верху окна с временной диаграммой расположена панель инструментов и навигации, при помощи которой можно выполнить настройку внешнего вида временной диаграммы.

Таким образом, были рассмотрены этапы от создания исходного описания цифрового устройства до разработки теста и получения временных диаграмм работы устройства в САПР Vivado.

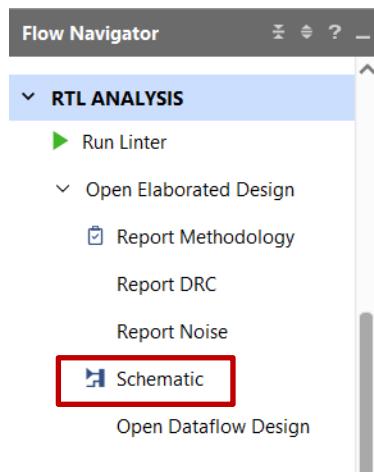

Помимо указанных возможностей, САПР Vivado позволяет анализировать логическую корректность вашего проекта. Чтобы убедиться, что составленное VHDL-описание компилируется без проблем, что все необходимые модели присутствуют и нет несоответствий интерфейсов, необходимо открыть окно Schematic (рис. 1.29) разработанного проекта (RTL Analysis → Open Elaborated Design)

Рис. 1.29. Запуск процесса генерации схемы проекта

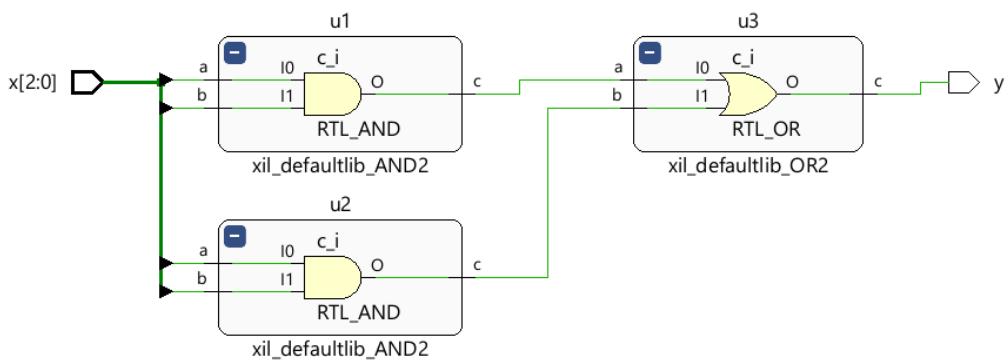

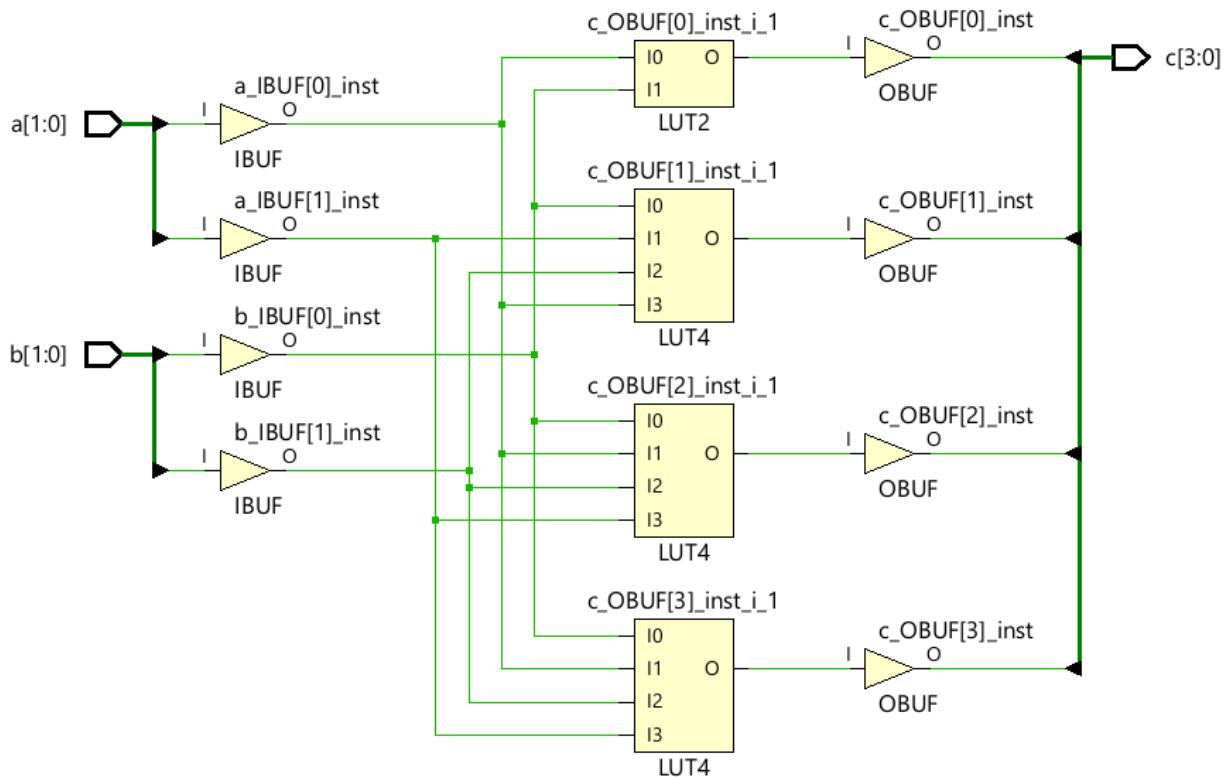

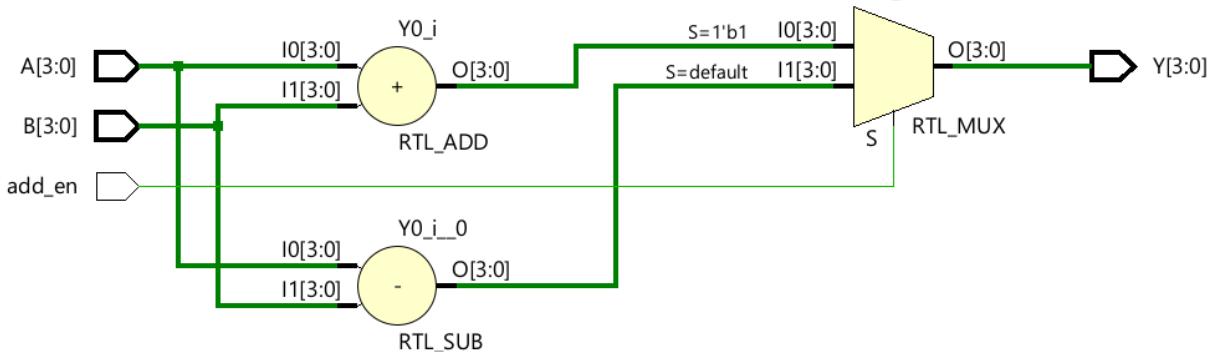

Например, для разработанного проекта (см. листинг 1.3) вид синтезированной схемы показан на рис. 1.30.

Рис. 1.30. Результат процесса анализа RTL-описания

В данном случае, поскольку анализируемое VHDL-описание не содержит сложных конструкций, все описанные примитивы были без труда распознаны Vivado как логические вентиli. Полученная схема полностью совпадает с исходной (см. рис. 1.10).

Инструмент Schematic позволяет визуализировать логические взаимосвязи разработанных модулей, а также иерархическую структуру проекта. Важно отме-

тить, что в процессе анализа VHDL-описания не происходит отображения разработанного проекта на технологический базис ПЛИС. Данный процесс следует рассматривать как этап валидации разработанного VHDL-описания. Например, если согласно логике описания в схеме должен быть мультиплексор, а фактически в полученной схеме (см. рис. 1.30) его нет.

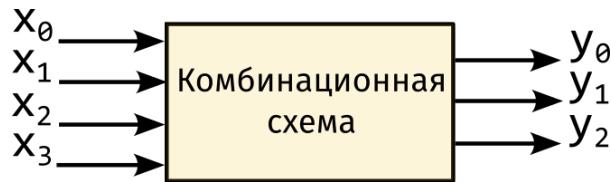

## 1.2. Порядок выполнения работы

1. Согласно варианту (табл. 1.2) выполнить синтез комбинационной схемы (рис. 1.31), реализующей систему логических функций. Для получения компактного описания логические функции необходимо минимизировать, применив любой известный метод минимизации, например, с помощью карт Карно, диаграмм двоичного выбора и т. д.

Таблица 1.2

Варианты для лабораторной работы № 1

| Вариант | Система логических функций                                                                                          |

|---------|---------------------------------------------------------------------------------------------------------------------|

| 1       | $y_0 = (7, 10, 11, 13, 14, 15);$<br>$y_1 = (5, 6, 9, 12);$<br>$y_2 = (1, 4, 6, 9, 11, 12, 14)$                      |

| 2       | $y_0 = (3, 7, 8, 10, 11, 13, 14, 15);$<br>$y_1 = (2, 5, 6, 8, 9, 12, 15);$<br>$y_2 = (1, 3, 9, 11, 12, 13, 14, 15)$ |

| 3       | $y_0 = (1, 3, 7, 11, 13, 15);$<br>$y_1 = (2, 3, 5, 6, 9, 12, 15);$<br>$y_2 = (1, 3, 6, 9, 11, 14)$                  |

| 4       | $y_0 = (0, 1, 2, 4, 6, 10, 11, 13, 14);$<br>$y_1 = (5);$<br>$y_2 = (2, 4, 5, 6, 8, 9, 10, 11, 12, 14)$              |

| 5       | $y_0 = (3, 7, 8, 9, 10, 11, 12, 14, 15);$<br>$y_1 = (2, 3, 5, 6, 8, 9, 12, 15);$<br>$y_2 = (3, 6, 9, 11, 12, 14)$   |

| 6       | $y_0 = (7, 13, 14);$<br>$y_1 = (5, 6, 8, 9, 12, 15);$<br>$y_2 = (1, 6, 9, 11, 12, 14)$                              |

| 7       | $y_0 = (2, 6, 7, 8, 9, 10, 11, 13, 15);$<br>$y_1 = (5, 9);$<br>$y_2 = (3, 11, 14)$                                  |

| 8       | $y_0 = (7, 10, 11, 13, 14, 15);$<br>$y_1 = (2, 3, 5, 6, 8, 9, 12, 15);$<br>$y_2 = (0, 1, 3, 5, \dots, 15)$          |

2. Разработать структурное VHDL-описание разработанной схемы.

3. Разработать поведенческую VHDL-модель разработанной схемы.

4. Составить тестирующую программу, выполнить моделирование разработанных VHDL-описаний на всех наборах значений входных переменных.

Рис. 1.31. Комбинационная схема, реализующая систему булевых функций

5. Составить отчет. В отчете должны быть приведены таблица истинности и соответствующие ей VHDL-модели. Также в отчете должна содержаться тестирующая программа для всех наборов входных переменных, соответствующих таблице истинности. В обязательном порядке в отчете должны быть приведены временные диаграммы, соответствующие тестирующей программе.

6. Подготовить отчет по лабораторной работе.

### 1.3. Дополнительные вопросы и задания

1. Записать семь логических операций языка VHDL.

2. Можно ли записывать оператор назначения сигнала как в левую ( `<=` ), так и в правую ( `=>` ) сторону?

3. Имеет ли тестирующая программа входные и выходные порты?

4. Используя логические операторы, записать VHDL-модель многоуровневой комбинационной схемы.

5. Верно ли то, что архитектурное тело ( `architecture` ) есть множество параллельных операторов, взаимодействующих между собой и находящихся под влиянием друг друга?

## ЛАБОРАТОРНАЯ РАБОТА № 2. ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ

ЦЕЛЬ РАБОТЫ: создание VHDL-модели электронной схемы, моделирование ее в САПР Vivado с задержками и без, анализ полученных временных диаграмм и определение максимальной задержки схемы.

### 2.1. Теоретические сведения

#### 2.1.1. Задержка распространения сигнала

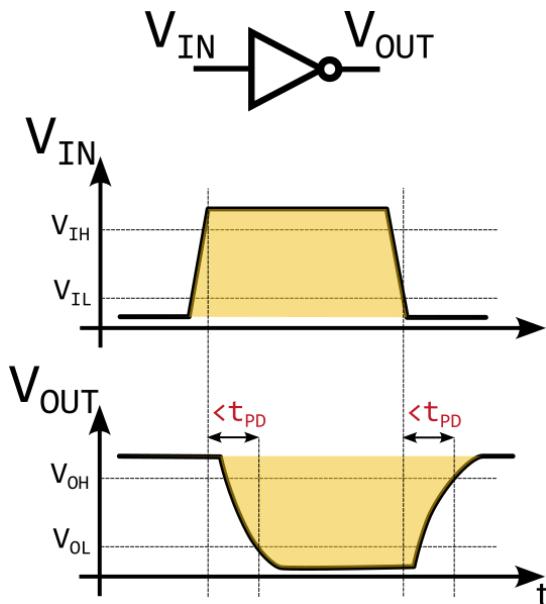

Все физические схемы имеют задержку распространения сигнала между изменением входного сигнала и результирующим изменением выходного сигнала. В качестве примера рассмотрим функционирование обычного инвертора (рис. 2.1).

Рис. 2.1. Задержка распространения сигнала в инверторе

Когда входное напряжение  $V_{IN}$  достигает уровня  $V_{IH}$  – логической единицы (по входу) – начинается переходной процесс переключения выходного уровня инвертора из состояния логической единицы в состояние логического нуля. Процесс считается завершенным, когда напряжение на выходе инвертора опускается ниже  $V_{OL}$  (выходного уровня нуля). Задержка между входом и выходом обозначается как  $t_{PD}$  и именуется задержкой распространения сигнала (*propagation delay*). В данном случае  $t_{PD}$  – это максимальная задержка распространения, которая в документации обычно обозначается как  $t_{PD,MAX}$ . Аналогичные процессы происходят и при переключении из состояния логической единицы в состояние логического нуля. Важно отметить, что времена задержки при переключении из нуля в единицу и из единицы в нуль могут отличаться. Разумеется, при проектировании цифровых устройств стремятся к тому, чтобы минимизировать задержку распространения сигнала.

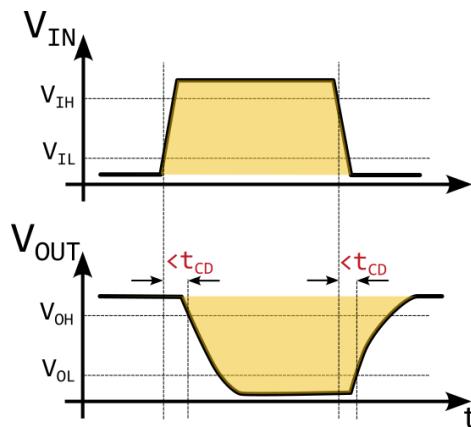

Помимо максимальной задержки распространения сигнала (см. рис. 2.1), иногда рассматривают также минимальную задержку распространения  $t_{PD,MIN}$ . В англоязычных источниках ее обозначают как  $t_{CD}$  (англ. *contamination delay*). По сути,  $t_{CD}$  представляет из себя нижнюю границу задержки от момента, когда сигнал перестал быть валидным на входе, до момента, когда сигнал перестает быть валидным на выходе, как показано на рис. 2.2.

Рис. 2.2. Минимальная задержка распространения сигнала

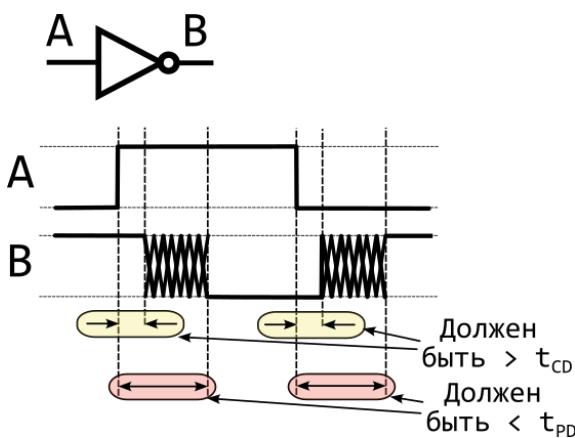

Если время  $t_{CD}$  не задано, его можно считать равным нулю. Таким образом, временную диаграмму переключения инвертора можно изобразить так, как показано на рис. 2.3.

Рис. 2.3. Диаграмма переключения инвертора

Во время переходного процесса, пока от момента переключения входного сигнала А прошло менее  $t_{PD}$ , состояние выхода В считается неопределенным. Значение выхода в этот период времени может восприниматься другими схемами как логическая единица либо как логический нуль. После истечения времени задержки распространения сигнала выход элемента переходит в устойчивое состояние.

Наличие у реальных логических элементов задержек распространения приводит к тому, что на выходах цифровых схем, собранных из логических элементов,

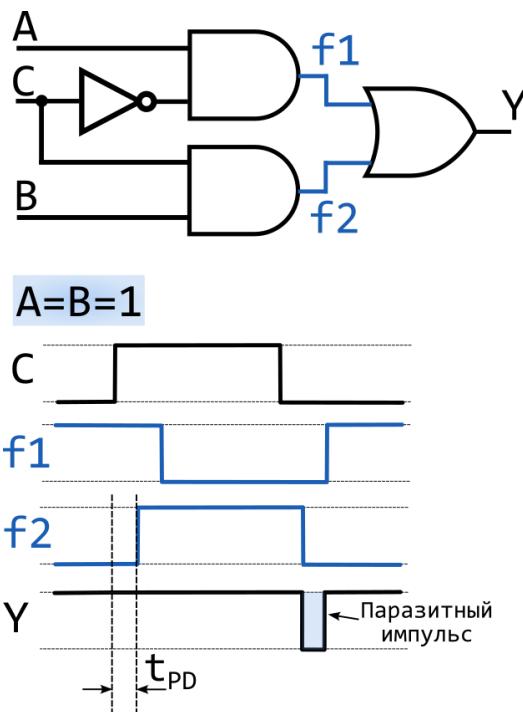

могут возникать паразитные импульсы (англ. *glitch*), которые также называют рисками сбоя или просто рисками (англ. *hazard*). В качестве иллюстрирующего примера рассмотрим схему на рис. 2.4.

Рис. 2.4. Схема, иллюстрирующая механизм появления паразитного импульса на выходе цифрового устройства

В рассматриваемой схеме входы  $A$  и  $B$  считаются фиксированными, на них подана логическая единица. Изменяется только сигнал  $C$ , который в данной ситуации не должен влиять на выходное значение  $Y$ . Тем не менее существование у реальных логических элементов задержек приводит к тому, что внутренние сигналы  $f_1$  и  $f_2$  изменяются не синхронно. В частности, сигнал  $f_1$  отстает от  $f_2$ , поскольку для его изменения должно произойти переключение двух элементов, а изменение  $f_2$  зависит только от одного вентиля И. Разбежка в переключении внутренних сигналов приводит к тому, что возникает ситуация, при которой выход  $Y$  на короткое время переходит в состояние логического нуля. Данный пример является иллюстрацией статического риска (сбоя). Вообще, под статическим риском понимают кратковременное изменение сигнала, который должен был бы оставаться неизменным (единичным или нулевым). Если же состояние выхода должно изменяться, но вместо однократного перехода происходят многократные, то имеет место динамический риск.

## 2.1.2. Анализ временных задержек

Важным элементом процесса проектирования цифрового устройства является анализ временных задержек разработанной схемы. В процессе анализа временных задержек все узлы в схеме помечаются как входные, выходные либо внутренние. Средство анализа (англ. *timing analyzer*) вычисляет время прибытия (англ. *arrival time*) для всех узлов схемы (т. е. максимальное время, за которое каждый из узлов схемы переключится). При этом разработчик должен указать время поступления входных сигналов, а также время, когда данные должны появиться на выходе. Время переключения  $a_i$  узла  $i$  зависит от задержки распространения вентиля, который управляет (является драйвером) узлом  $i$ , а также от времени переключения входов этого вентиля.

$$a_i = \max_{j \in \text{fan}_{\text{in}}(i)} \{a_j\} + t_{\text{PD}_i}.$$

При анализе задержек важным понятием является *временной резерв* (англ. *slack*), который определяется как время между требуемым и фактическим временем переключения сигнала. Если временной резерв является положительным, то считается, что цифровая схема удовлетворяет временным ограничениям. Отрицательное значение временного резерва указывает на то, что схема работает недостаточно быстро.

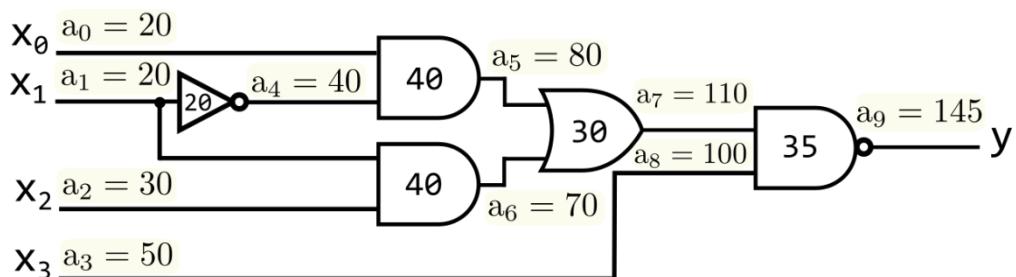

Чтобы глубже разобраться с понятием временного резерва, рассмотрим схему на рис. 2.5. На этой схеме внутри вентиляй указаны их задержки в пикосекундах.

Рис. 2.5. Схема, иллюстрирующая понятие временного резерва (*slack*)

Для каждого узла указано время поступления сигнала. Для внутренних узлов это время поступления рассчитывается с использованием выражения приведенной формулы. Если дополнительно задать, что ожидаемое время поступления сигнала на выход равно 200 пс, то временной резерв в данном случае будет равен 55 пс.

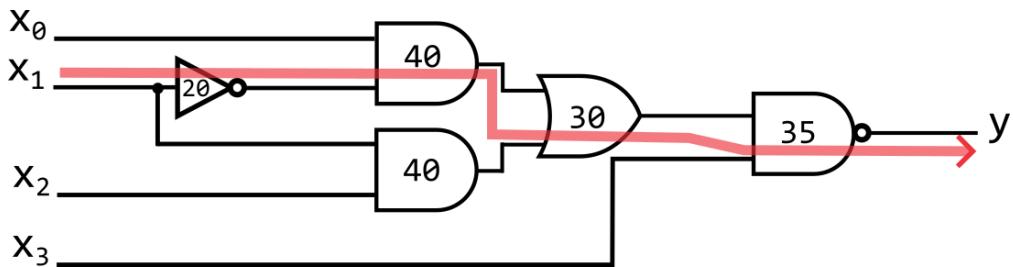

Как правило, большинство цепей в цифровом устройстве удовлетворяет заданным временным ограничениям, при этом, однако, может существовать некоторое число критических путей, которые ограничивают скорость работы устройства. На рис. 2.6 показан критический путь для схемы, которая использовалась для иллюстрации понятия временного резерва.

Рис. 2.6. Критический путь схемы

В рассматриваемом примере критический путь проходит через четыре вентиля. Общая задержка, которая возникает между приходами входных сигналов и формированием выхода, равна 125 пс.

### 2.1.3. Моделирование VHDL-описаний цифровых устройств

При моделировании VHDL-описаний схем иногда необходимо указать величину задержки между входом и выходом ее элементов. Ниже показан пример, который поясняет, каким образом можно добавить задержку в описание простого вентиля И (листинг 2.1).

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity AND2 is

Port (a: in STD_LOGIC;

b: in STD_LOGIC;

c: out STD_LOGIC);

end AND2;

architecture arch1 of AND2 is

begin

c <= a and b after 2 ns;

end arch1;

```

Листинг 2.1. VHDL-описание вентиля И с задержкой

Главной особенностью приведенного описания является использование ключевого слова `after` в операторе назначения сигнала `<=`. Фактически в архитектурном описании вентиля И указывается, что новое значение выходному сигналу `c`, равное `a and b`, будет назначено через 2 нс модельного времени после изменения входных сигналов (`a` либо `b`). Более формально оператор назначения сигнала имеет следующее описание.

```

<signal> <= [transport] <value> [after <time>];

```

Здесь, как и ранее, в квадратных скобках указаны необязательные параметры. Ключевое слово `transport` определяет, что при назначении сигнала используется *транспортная* задержка, в противоположном случае задержка считается *инерционной*.

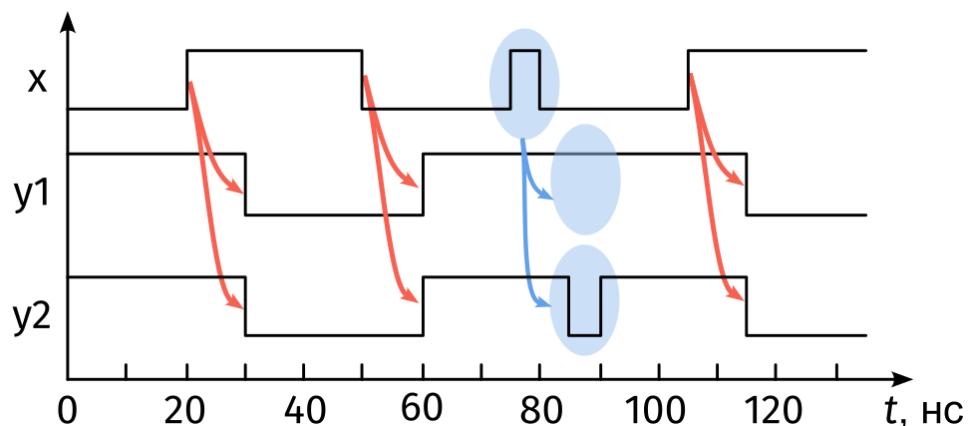

В случае инерционной задержки значение сигнала изменяется только тогда, когда входной сигнал будет сохранять соответствующий уровень в течение времени, заданного параметром `after`. В случае транспортной задержки сигнал изменяется независимо от того, сколько входной сигнал сохранял свой уровень. Приведем пример.

```

y1 <= not x after 10ns; -- назначение сигнала

y2 <= transport not x after 10ns;

```

На рис. 2.7 показана временная диаграмма сигналов  $x$ ,  $y_1$  и  $y_2$ .

Рис. 2.7. Иллюстрация понятия транспортной и инерционной задержки

Можно заметить, что поведение  $y_1$  и  $y_2$  практически везде совпадает, за исключением временного интервала, в котором во входном сигнале  $x$  возникает кратковременный импульс длительностью менее 10 нс. В сигнале  $y_2$  импульс находит свое отражение, поскольку в данном случае моделируется транспортная задержка сигнала, которая используется, чтобы моделировать задержки, возникающие в линиях связи между отдельными элементами схемы. В сигнале  $y_1$  реакции на импульс нет, поскольку моделируемая задержка в данном случае является инерционной, поэтому любые изменения на входе длительностью менее 10 нс отфильтровываются, т. е. отбрасываются системой моделирования и не приводят к формированию нового значения  $y_1$ .

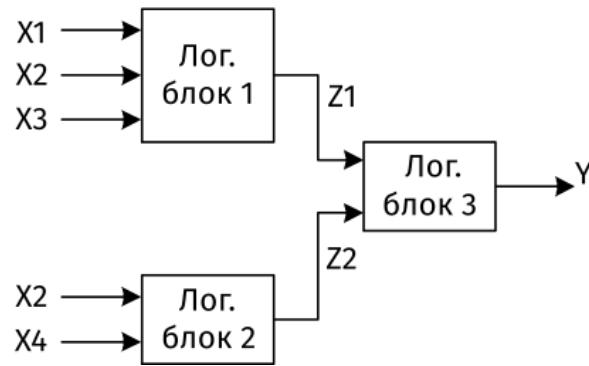

Рассмотрим более подробно, как происходит процесс моделирования работы цифрового устройства, описанного на языке VHDL. Ранее уже упоминалось, что сигналы в цифровых устройствах передаются и обрабатываются параллельно. Обратимся к примеру, показанному на рис. 2.8.

Рис. 2.8. Параллельные процессы в VHDL

Если подать значения входных сигналов на логический блок 1 и логический блок 2, то эти блоки будут одновременно активированы. Через некоторое время выходные сигналы поступят на вход блока 3, а в это время на блоки 1 и 2 могут прийти новые значения.

Параллельность работы отдельных блоков реализуется на VHDL с помощью процессов (process). Каждому логическому блоку соответствует свой процесс. Описание схемы может иметь следующий вид.

```

...

BL1: process (x1,x2,x3)

begin

end process BL1;

BL2: process (x2,x4)

begin

end process BL2;

BL3: process (z1,z2)

begin

end process BL3;

...

```

Процесс активируется, когда происходит изменение какого-либо сигнала в списке сигналов запуска (списке чувствительности) этого процесса, который идет после ключевого слова `process`. Список чувствительности соответствует входным сигналам логического блока.

Каждый процесс может быть в одном из трех состояний:

- выполняющийся;

- активный;

- приостановленный.

Процесс является выполняющимся, когда система моделирования выполняет процесс; активным, когда процесс ожидает, чтобы система его выполнила; приостановленным, когда не является активным или выполняющимся. Выполненный процесс является приостановленным.

Параллелизм процессов программно имитируется, поэтому только один из нескольких параллельных процессов является выполняющимся по существу. Моделирование параллельных процессов осуществляется так: все параллельные процессы, которые надо одновременно выполнить, выстраиваются в очередь, система моделирования выбирает процесс из очереди и выполняет его, затем следующий, пока не будет исчерпан весь список активных процессов. Когда очередь активных процессов пуста, считается, что все параллельные сигналы выполняются одновременно, и тогда изменяются значения всех сигналов. После этого выполняется следующий цикл моделирования.

В процессе моделирования одного дискретного момента времени приостановленный процесс может стать активным, когда один из драйверов сигналов в списке чувствительности изменился.

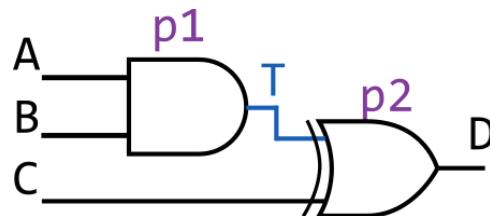

Чтобы пояснить процесс моделирования VHDL-описаний, рассмотрим еще один пример схемы (рис. 2.9), которая описывается VHDL-кодом, приведенным ниже.

Рис. 2.9. Комбинационная схема

```

entity NANDXOR is

port (A,B,C: in std_logic; D: out std_logic);

end NANDXOR;

architecture RTL of NANDXOR is

signal T: std_logic;

begin

p0: T<=A nand B after 2 ns;

p1: process (T,C)

begin

D<=T xor C after 3 ns;

end process p1;

end RTL;

```

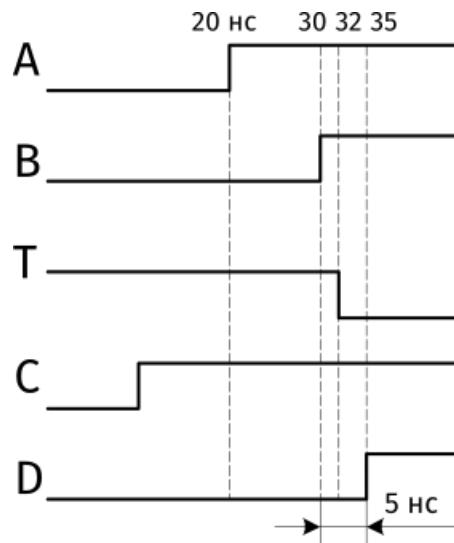

При инициализации каждый из сигналов имеет значение 0. Если в ходе теста какой-то из входных сигналов изменился, то процесс p0 вычислит значение T и приостановится, затем будет вычисляться значение D в процессе p1. Очередной цикл моделирования начинается тогда, когда один из сигналов изменится. Изменение сигнала называется событием. На рис. 2.10 показана временная диаграмма работы комбинационной схемы при изменении входных сигналов.

Рис. 2.10. Временная диаграмма работы комбинационной схемы

Из приведенной временной диаграммы видно, что максимально возможная задержка (соответствующая критическому пути схемы) равна 5 нс и возникает при переключении входного сигнала В.

#### 2.1.4. Дельта-задержка

Для правильного понимания моделирования VHDL-описания важным является понятие *дельта-задержки*. Чтобы пояснить данное понятие, рассмотрим, как будет происходить процесс моделирования комбинационной схемы, показанной на рис. 2.9, если не учитывать задержек распространения сигналов в элементах схемы. В этом случае архитектурное тело VHDL-описания схемы примет следующий вид.

```

architecture Delta of NANDXOR is

signal T: std_logic;

begin

p0: T<=A nand B; -- нет after

p1: process (T,C)

begin

D<=T xor C;

end process p1; -- нет after

end Delta;

```

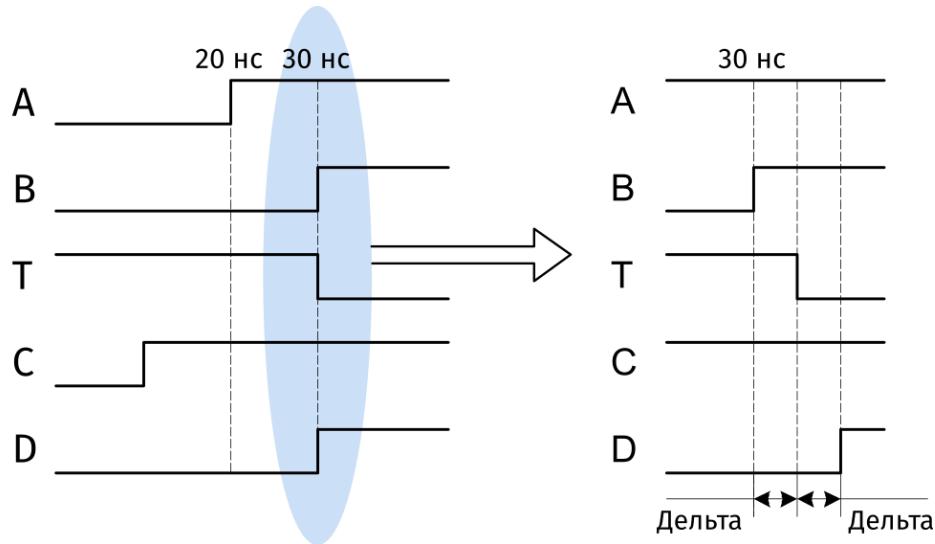

Временная диаграмма, получаемая в результате моделирования данного описания, представлена на рис. 2.11.

В момент времени 30 нс входной сигнал В изменился, что послужило причиной изменения сигнала Т и сигнала D. На временной диаграмме все это случилось в одно время, однако логичным будет сказать, что сигнал Т изменился после сигнала В. Бесконечно малая величина, показанная на рис. 2.11, называется дельта-задержкой. Сигнал D изменится после изменения сигнала Т, т. е. появляется другая дельта-задержка.

Рис. 2.11. Иллюстрация понятия дельта-задержки

*Дельта-задержка* – основное понятие моделирования в VHDL, это условная величина (один цикл прогона VHDL-модели, условный такт моделирования, когда нет явного указания времени задержки – *after*, *wait*).

VHDL-модели, имитирующие поведение цифровых систем, состоят из множества процессов. Во время прогона модели в данном цикле запускаются все процессы, входные сигналы которых изменились с момента выполнения последнего цикла. После того как все процессы выполнены, данный цикл моделирования считается завершенным. Следующий цикл начинается тогда, когда произойдет изменение какого-либо сигнала в списке чувствительности процесса. Этот период может составлять секунды, наносекунды или быть равным дельта. С точки зрения логической схемы дельта-задержка – задержка на одном каскаде логики, когда не заданы конкретные временные задержки логических элементов.

Механизм событий при моделировании позволяет имитировать исполнение параллельных процессов несмотря на то, что работа моделирующей программы представляет собой один поток операций, выполняющихся последовательно. Механизм дельта-задержек позволяет обнаружить некорректные присваивания сигналов типа  $X \leftarrow \text{not } X$ . В этом случае процесс моделирования заходит в бесконечный цикл. Чтобы этого избежать, задают ограничение на число тактов моделирования (обычно 5000) и прерывают моделирование, если за это количество тактов не произошло изменение ни одного сигнала за нулевой момент времени (за дельта-задержку).

Важным является вопрос о том, где в описаниях на языке VHDL могут быть использованы операторы присваивания значений переменным и операторы назначения сигналов. Присваивание значений переменным разрешается внутри процессов, в функциях и процедурах. Назначение сигнала может встречаться в любом месте исполняемого раздела архитектурного тела.

## 2.2. Порядок выполнения работы

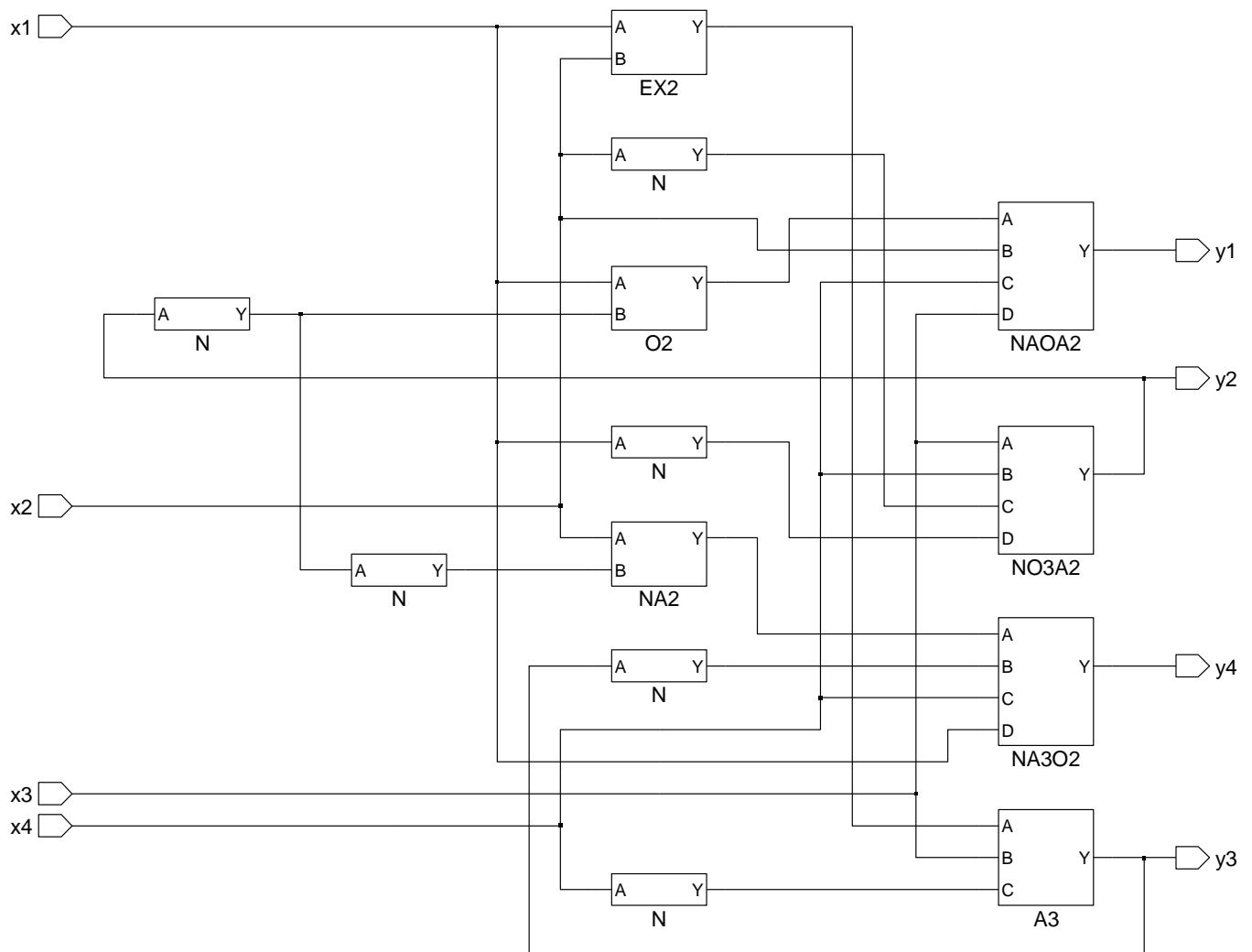

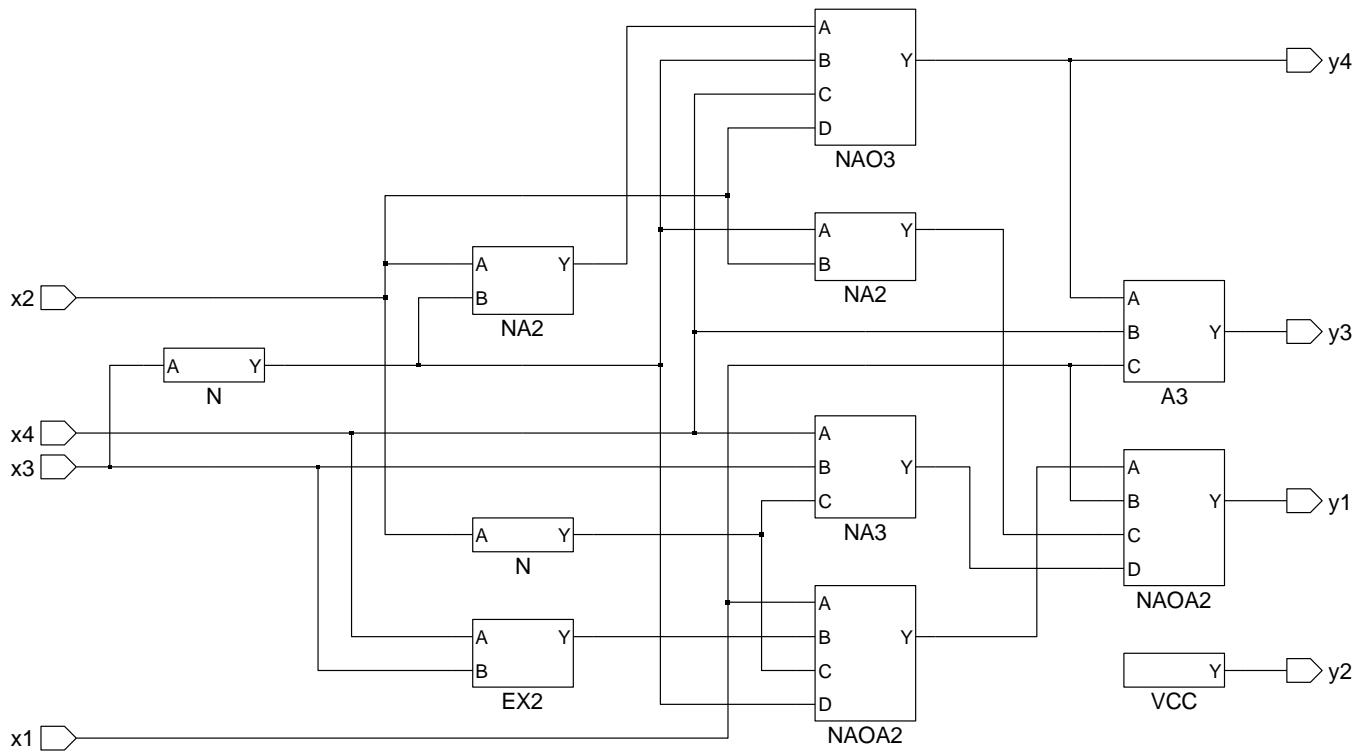

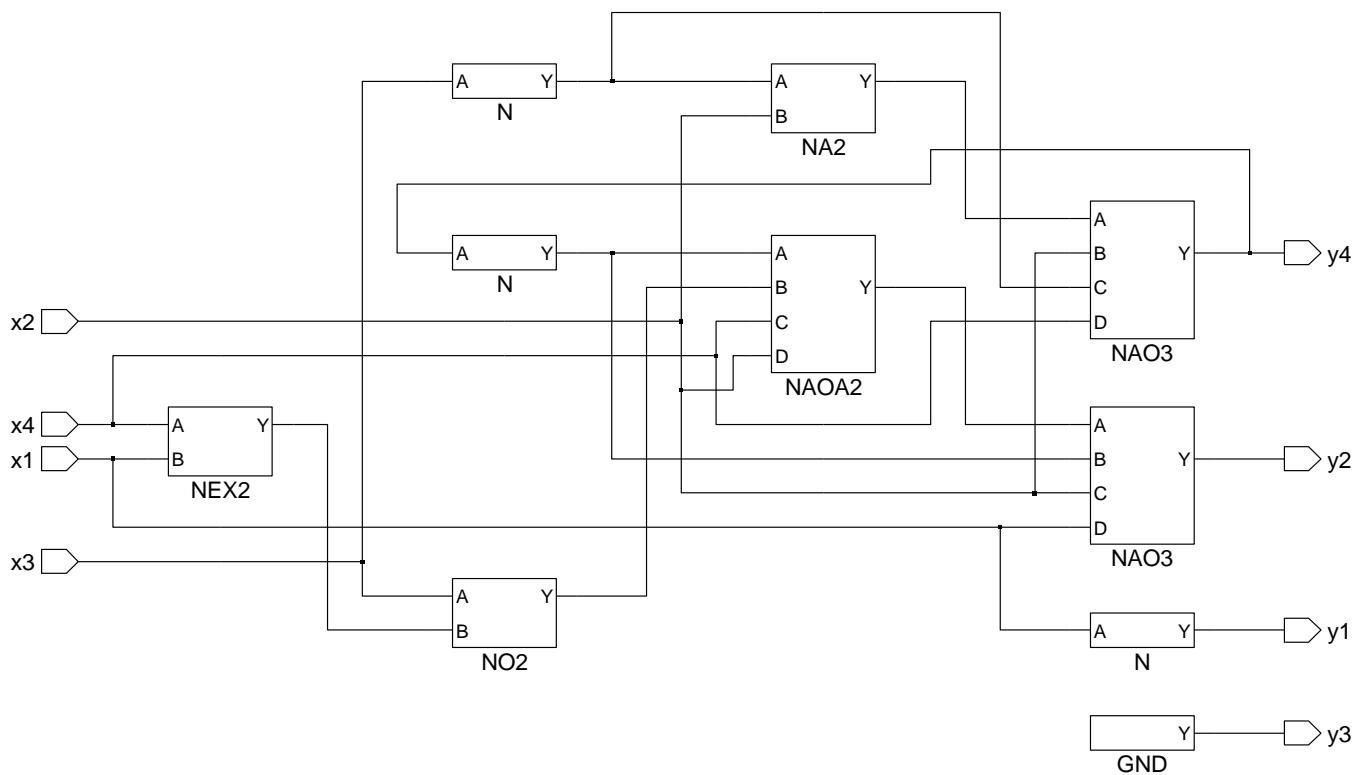

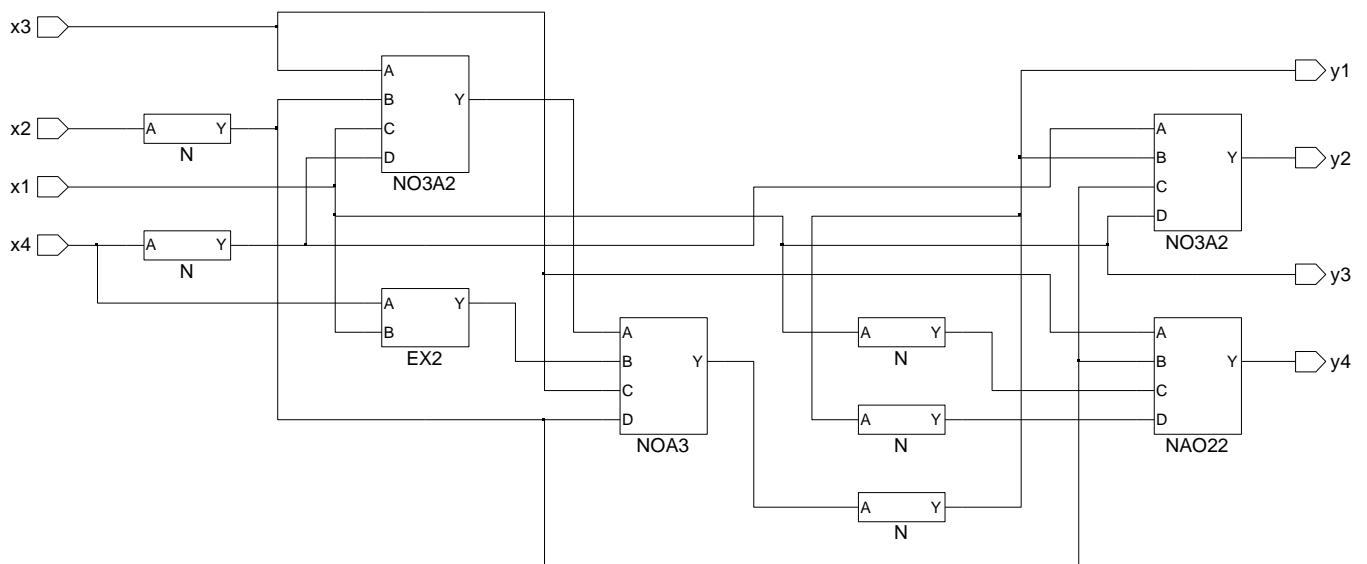

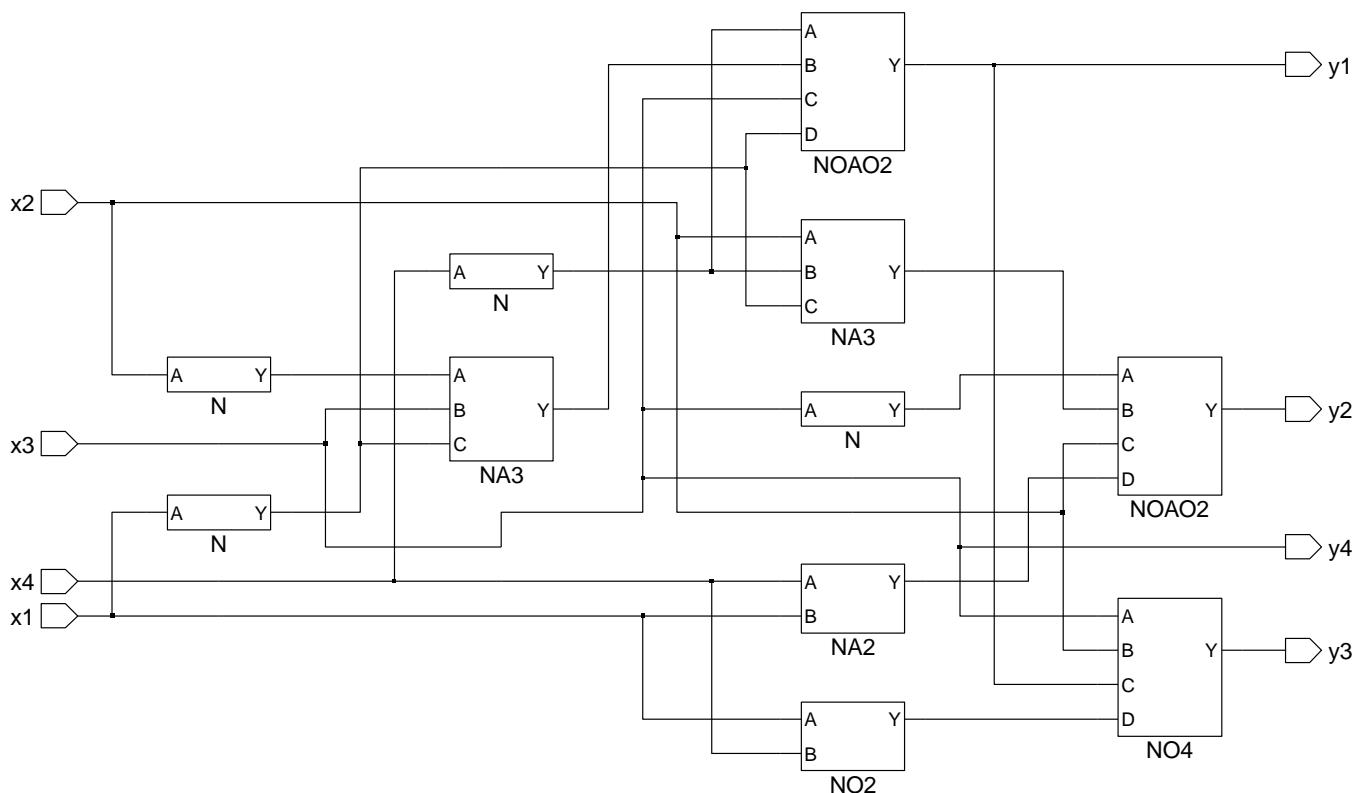

1. Получить у преподавателя вариант нерегулярной логической схемы (см. приложение). Для заданной схемы составить структурное VHDL-описание. Составить VHDL-модель каждого из типов элементов, входящих в схему. Если в схеме есть элементы одинакового типа, то составляется одна модель для всех элементов данного типа. Модель элемента должна соответствовать задержке, указанной в таблице П.1. При графическом изображении логического элемента на схеме будут указываться его тип (библиотечное имя) и имена входных и выходных полюсов.

2. Составить тестирующую программу для всех наборов значений входных переменных.

3. Провести моделирование и получить временную диаграмму.

4. По временной диаграмме записать систему логических функций, реализуемых схемой.

5. Для каждого тестирующего набора определить задержку схемы.

6. Найти критический путь на схеме – путь с наибольшей суммарной задержкой элементов.

7. Подготовить отчет по лабораторной работе. В отчете должна быть нарисована логическая схема. При этом обозначения сигналов, элементов схемы должны соответствовать описанию на языке VHDL. В отчете должен содержаться VHDL-код схемы и тестирующая программа. VHDL-код и тест должны быть в отдельных файлах и содержать комментарии: а) автор разработанной VHDL-модели; б) номер варианта. В отчете должны содержаться временные диаграммы, соответствующие тестирующей программе, система логических функций, реализуемых схемой. На логической схеме должен быть отмечен критический путь. В отчете должно быть указано значение задержки схемы, соответствующее задержке критического пути.

## 2.3. Дополнительные вопросы и задания

1. Нарисовать дерево иерархии проекта логической схемы, моделирование которой было проведено лабораторной работе № 2.

2. Что такое ключевое соответствие портов?

3. Что такое позиционное соответствие портов?

4. Могут ли употребляться операторы создания экземпляров компонентов (`port map`) вместе с операторами назначения сигнала в архитектурном теле?

5. Правильно ли то, что в операторе `port map` символы `=>` и `<=` (соответствия) употребляются в зависимости от направления порта (для входа символы `=>`, для выхода символы `<=`)?

6. Правильно ли то, что операторы `port map` обязательно должны иметь метки?

7. Что такое временной резерв (*slack*)?

8. Что такое транспортная и инерционная задержки в VHDL? Для чего они используются?

9. Пояснить, что такое дельта-задержки и для чего они используются в процессе моделирования.

# ЛАБОРАТОРНАЯ РАБОТА № 3. ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ НА УРОВНЕ ВЕНТИЛЕЙ И РЕГИСТРОВЫХ ПЕРЕДАЧ НА SYSTEMVERILOG

ЦЕЛЬ РАБОТЫ: изучение основных конструкций языка SystemVerilog, освоение концепции проектирования цифровых устройств на уровне логических вентилей и регистрационных передач.

## 3.1. Теоретические сведения

### 3.1.1. Краткая история SystemVerilog

Язык описания аппаратуры Verilog создан в начале 1980-х годов компанией Gateway Design Automation. Вначале Verilog был проприетарным программным обеспечением (ПО), однако в 1989 году он перешел в категорию ПО с открытым исходным кодом. В 1995 году был выпущен первый стандарт IEEE данного языка. Стандарт впоследствии обновлялся в 2001 и 2005 годах. Версия 2001 года является наиболее широко используемой, при ссылке на нее обычно говорят просто Verilog. Однако растущая сложность проектирования цифровых схем привела к тому, что в 2005 году был выпущен новый IEEE стандарт Verilog. В это же время был разработан новый стандарт, описывающий язык SystemVerilog. После 2005 года в IEEE началась работа по объединению двух стандартов в один язык. Последующий язык получил название SystemVerilog и был закреплен в стандарте 2009 года. На этом этапе Verilog был полностью заменен SystemVerilog. Впоследствии происходило обновление стандарта SystemVerilog в 2012 и в 2017 годах. Некоторые расширенные функции SystemVerilog остаются нереализованными в различных коммерческих компиляторах SystemVerilog.

### 3.1.2. Модуль

В SystemVerilog модуль является базовым «строительным блоком». Каждый модуль определяется как набор входных и выходных *портов*, которые являются входными и выходными сигналами схемы. Тело каждого модуля начинается с ключевого слова *module*, за которым следует объявление портов. Внутри модуля объявляются внутренние сигналы и описывается логика работы схемы, затем идет описание модуля и завершается ключевым словом *endmodule*. Внутри модуля могут создаваться экземпляры одной или нескольких копий других модулей.

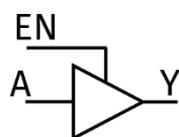

В простейшем случае модуль на SystemVerilog состоит из комбинации базовых вентилей, описание которых приведено в табл. 3.1.

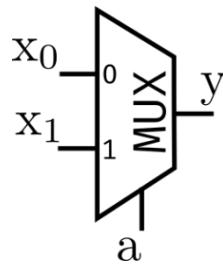

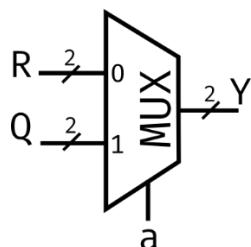

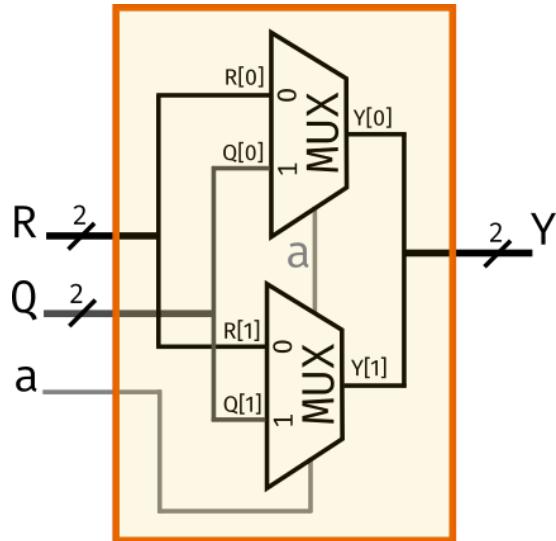

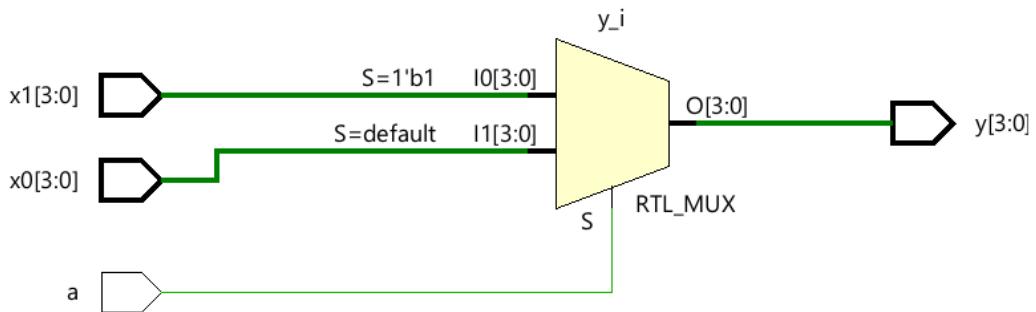

В качестве примера опишем простую комбинационную схему – мультиплексор 2:1. Мультиплексор имеет два информационных входа  $x_0$  и  $x_1$  и один адресный вход  $a$  и выход  $y$  (рис. 3.1).

Таблица 3.1

## Описание базовых вентилей на языке SystemVerilog

| Тип вентиля                                  | Синтаксис                           | Описание                                                                                                                                                                        |

|----------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| И                                            | <code>and g(y, x1, x2, ...)</code>  | Выполняет логическую операцию И над двумя и более входами                                                                                                                       |

| ИЛИ                                          | <code>or g(y, x1, x2, ...)</code>   | Выполняет логическую операцию ИЛИ над двумя и более входами                                                                                                                     |

| Исключающее ИЛИ                              | <code>xor g(y, x1, x2, ...)</code>  | Выполняет логическую операцию исключающее ИЛИ над двумя и более входами                                                                                                         |

| И-НЕ                                         | <code>nand g(y, x1, x2, ...)</code> | Выполняет логическую операцию И-НЕ над двумя и более входами                                                                                                                    |

| Эквивалентность                              | <code>xnor g(y, x1, x2, ...)</code> | Выполняет логическую операцию эквивалентность над двумя и более входами                                                                                                         |

| Буфер                                        | <code>buf g(y, x)</code>            | Буферный элемент                                                                                                                                                                |

| НЕ                                           | <code>not g(y, x)</code>            | Выполняет логическую операцию НЕ                                                                                                                                                |

| Трехстабильный буфер с управляющим входом    | <code>bufif1 g(y, x, c)</code>      | Буферный элемент с управляющим входом с. Входной сигнал x проходит на выход y только тогда, когда управляющий сигнал c равен 1, иначе выход устанавливается в z-состояние       |

| Трехстабильный буфер с управляющим входом    | <code>bufif0 g(y, x, c)</code>      | Буферный элемент с управляющим входом с. Входной сигнал x проходит на выход y только тогда, когда управляющий сигнал c равен 0, иначе выход устанавливается в z-состояние       |

| Трехстабильный инвертор с управляющим входом | <code>notif1 g(y, x, c)</code>      | Элемент НЕ с управляющим входом с. Отрицание входного сигнала x проходит на выход y только тогда, когда управляющий сигнал c равен 1, иначе выход устанавливается в z-состояние |

| Трехстабильный инвертор с управляющим входом | <code>notif0 g(y, x, c)</code>      | Элемент НЕ с управляющим входом с. Отрицание входного сигнала x проходит на выход y только тогда, когда управляющий сигнал c равен 0, иначе выход устанавливается в z-состояние |

Рис. 3.1. Обозначение мультиплексора 2:1

Если адресный вход  $a$  равен нулю, то выход  $y = x_0$ , в противоположном случае  $y = x_1$ . Поведение мультиплексора описывается логической функцией

$$y = x_0 \bar{a}_0 + x_1 a_0.$$

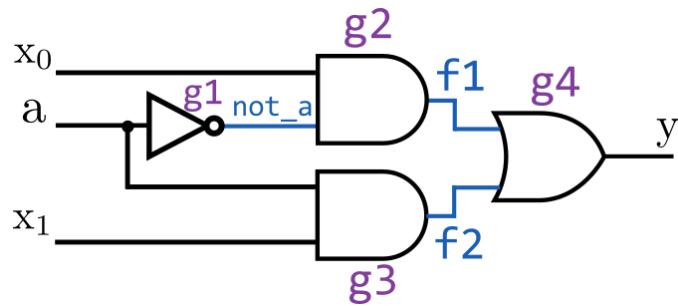

Реализация мультиплексора на уровне логических вентилей показана на рис. 3.2.

Рис. 3.2. Реализация мультиплексора в базисе логических вентилей

На языке SystemVerilog мультиплексор *на уровне вентилей* (англ. *gate-level modeling*) может быть описан следующим образом.

```

module mux

(

input logic x0, x1, a,

output logic y

);

logic not_a, f1, f2;

not g1(not_a, a);

and g2(f1, x0, not_a);

and g3(f2, x1, a);

or  g4(y, f1, f2);

endmodule

```

Приведенное описание, по сути, является текстовым аналогом схемы, представленной на рис. 3.2. Для удобства сопоставления на рис. 3.3 показана схема того же мультиплексора с указанием названий внутренних связей.

Рис. 3.3. Схема мультиплексора с обозначением внутренних связей

В дальнейшем мы будем использовать приведенное описание мультиплексора для иллюстрации некоторых концепций языка SystemVerilog.

### Логические типы данных

В примере с мультиплексором входы и выходы объявлены как однобитовый тип логических данных (тип `logic`). Логический тип данных может принимать четыре различных значения, которые перечислены в табл. 3.2.

Таблица 3.2

Значения типа данных `logic`

| Значение | Описание                                      |

|----------|-----------------------------------------------|

| 0        | Логический нуль                               |

| 1        | Логическая единица                            |

| x        | Неопределенное состояние                      |

| z        | Высокоимпедансное состояние, третье состояние |

Значения 0 и 1 типа данных `logic` не требуют дополнительных пояснений, они используются для обозначения того, что внутренний сигнал схемы находится в одном из двух устойчивых состояний. Значение X возникает в том случае, если внутренняя линия схемы не проинициализирована. Значение Z возникает, когда внутренний сигнал схемы не имеет источника, т. е. им никто не управляет. Таких ситуаций следует избегать. Состояния X и Z имеют значение только на этапе моделирования, их появление на линиях, как правило, сигнализирует разработчику о наличии ошибок в описании схемы.

Для ускорения процесса моделирования в SystemVerilog используют тип `bit`. Битовый тип принимает всего два значения: 0 и 1, и поэтому занимает в памяти меньше места, а также упрощает анализ сигналов данного типа.

В SystemVerilog существуют и другие типы данных, из которых стоит упомянуть `int` и `tri/wire`. Тип `int` – это 32-разрядные целые числа, которые не допускают значений X и Z. Тип `int` обычно используется для описания итераций циклов при составлении тестов, но не используется для описания синтезируемых

конструкций. Линии (сигналы), имеющие тип `tri/wire`, могут управляться несколькими источниками, что используется для моделирования/описания буферов с тремя состояниями и при описании шин.

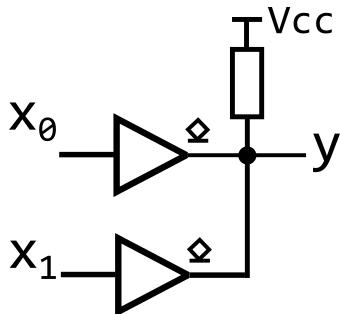

Чтобы проиллюстрировать использование типа `wire`, рассмотрим следующую схему (рис. 3.4).

Рис. 3.4. Схема «монтажного» И

Приведенная схема реализует так называемое «монтажное» И. Здесь использованы два буфера с открытым коллектором (или открытым стоком). Если хотя бы на одном из входов будет установлен низкий уровень, то выходная линия будет замкнута на «землю». Если на двух входах установлен высокий уровень, то это приведет к тому, что на выходной линии будет присутствовать высокий уровень, т. е. логическая единица. Таким образом, представленная схема из двух буферов с объединением двух выходов реализует логическое («монтажное») И для положительной логики. Заметьте, что при использовании обычных вентилей объединение выходов схем не допускается.

Ниже приведено описание «монтажного» И на SystemVerilog.

```

module mount_and(

input logic [1:0] x,

output wire y

);

buf(weak1, strong0) b1(y, x[0]);

buf(weak1, strong0) b2(y, x[1]);

endmodule

```

Обратим внимание, что при объявлении выходного порта используется тип `wire`, поскольку только данный тип позволяет описывать управление линией с двумя источниками (англ. *drivers*). При описании буферных элементов мы указываем *силу* (англ. *strength*) сигналов на входах и выходах элементов. Значение `weak1` указывает, что выход буферного элемента «подтянут к 1» (англ. *weak pull-up to 1*), т. е. подключен через резистор к напряжению питания, как показано на

рис. 3.4. Такое подключение позволяет получать логическую единицу на выходе буфера при подаче на вход высокого уровня сигнала. Использование значения `strong0` при указании силы сигнала на входе говорит о том, что на входе по умолчанию подан «сильный» (стабильный) низкий логический уровень.

На рис. 3.5 показана временная диаграмма работы схемы «монтажного» И.

Рис. 3.5. Тестирование «монтажного» И

Рекомендуется использовать тип данных `logic` для синтезируемых конструкций, если только нет необходимости использовать другой тип данных.

### *Создание экземпляра модуля*

В SystemVerilog цифровые схемы описываются в соответствии с принципами иерархичности и вложенности. Поэтому схемы более высокого уровня всегда включают модули более низкого уровня. Мы уже это видели, когда описывали мультиплексор (см. рис. 3.2). По сути, при описании модуля `mix` после объявления портов и внутренних сигналов мы *создали экземпляры* четырех примитивных логических элементов. Сами логические элементы мы не описывали, поскольку они являются стандартными модулями SystemVerilog. Важно понять, что создание экземпляра (англ. *instantiation*) является параллельным оператором, поэтому не важно, в каком порядке создаются модули. Создание экземпляров модулей можно сравнить с процессом рисования схемы устройства на бумаге: не важно, в каком порядке вы рисуете элементы, главное, чтобы все они были изображены, а также, чтобы все связи между ними были указаны. Конечным результатом описания является аппаратная схема со всеми связями между ее элементами.

Формально синтаксис создания экземпляра модуля на SystemVerilog следующий.

```

module_name instance_name (arg1, arg2, ...)

```

Вначале указывается название модуля (`module_name`), затем указывается название экземпляра (`instance_name`), в скобках происходит назначение сигналов на входы и выходы модуля. Название экземпляра полезно при отладке, особенно

если в проекте есть несколько экземпляров одного и того же модуля. Назначение входных/выходных портов может осуществляться различными способами:

- позиционное соответствие;

- ключевое соответствие («передача по имени»).

В примере с описанием мультиплексора `mux` назначение портов выполняется при помощи позиционного соответствия. Это стандартный стиль, который напоминает передачу аргументов в функцию в языке программирования С. При позиционном соответствии каждый сигнал передается в соответствующий порт в порядке следования портов при определении модуля. Стандартные логические элементы (`and`, `or`, `buf` и др.) всегда передают выходные данные в качестве первого порта, за которым следуют входные данные (см. табл. 3.1).

Предположим, что внутри схемы имеются сигналы `X`, `Y`, `Z`, `W` и нам необходимо создать экземпляр мультиплексора `mux` с назначением портов  $x_0 = X$ ,  $x_1 = Y$ ,  $a_0 = Z$ ,  $y = W$ . Используя позиционное соответствие в языке SystemVerilog, мы можем сделать это следующим образом.

```

mux mux_unit (X, Y, Z, W)

```

Несмотря на простоту приведенного выше способа назначения портов, его следует избегать, отдавая предпочтение ключевому соответству. Все дело в том, что при использовании ключевого соответствия вероятность допустить ошибку гораздо ниже. Представим себе ситуацию, что по какой-то причине разработчик внес изменение в порядок объявления портов в модуле (например, выходной порт у мультиплексора `mux` переместил на первое место). В этом случае необходимо проследить, чтобы во всех экземплярах модуля были внесены соответствующие правки. Если хотя бы в одном месте не выполнить переназначения, то впоследствии обнаружить такую ошибку будет достаточно сложно.

По этой причине следует использовать передачу по имени, т. е. ключевое соответствие, где каждому порту явно присваивается имя внутреннего сигнала. Пример ключевого соответствия приведен ниже.

```

mux mux_unit (.x0(X), .x1(Y), .a0(Z), .y(W))

```

Теперь мы можем изменить порядок портов так, как захотим, без необходимости обновлять экземпляры. Имена линий привязаны при помощи ключевого соответствия к соответствующим портам.

Если имя порта и имя сигнала, передаваемого в этот порт, совпадают, то круглые скобки могут быть опущены. Если в приведенном выше примере сигнал `X` переименовать в `x0`, а `Y` переименовать в `x1`, то назначение по имени будет выглядеть следующим образом.

```

mux mux_unit (.x0, .x1, .a0(z), .y(w))

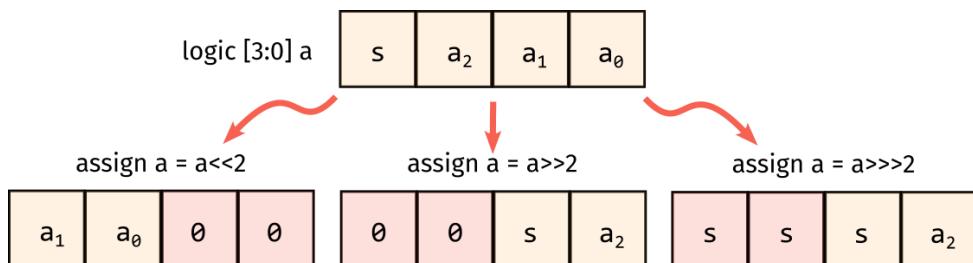

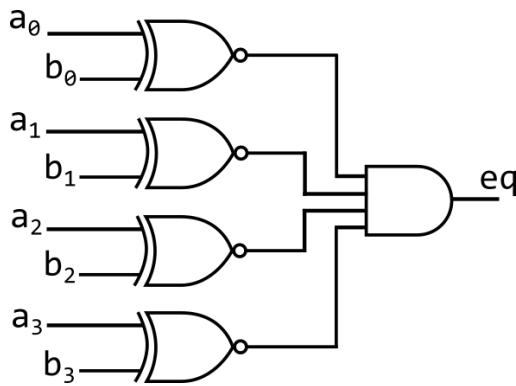

```