# Back-end-of-line compatible $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$ ferroelectric devices enabled by microwave annealing

Yinchi Liu<sup>1,2</sup> , Hao Zhang<sup>1</sup>, Jining Yang<sup>1</sup>, Dmitriy Anatolyevich Golosov<sup>3</sup>, Xiaohan Wu<sup>1,4</sup>, Chenjie Gu<sup>5,\*</sup>, Shijin Ding<sup>1,4</sup> & Wenjun Liu<sup>1,2,6,\*</sup>

<sup>1</sup>School of Microelectronics, Fudan University, Shanghai 200433, China

<sup>2</sup>Shaoxin Laboratory, Shaoxing, Zhejiang 312000, China <sup>3</sup>Belarusian State University of Informatics and Radioelectronics, Minsk 220013, Belarus

<sup>4</sup>Jiashan Fudan Institute, Fudan University, Jiaxing, Zhejiang 314100, China

<sup>5</sup>Department of Microelectronic Science and Engineering, School of Physical

Science and Technology, Ningbo University, Ningbo 315211, China

<sup>6</sup>Zhangjiang Fudan International Innovation Center, Fudan University, Shanghai 201203, China

\*E-mails: [guchenjie@nbu.edu.cn](mailto:guchenjie@nbu.edu.cn) (Chenjie Gu), [wjliu@fudan.edu.cn](mailto:wjliu@fudan.edu.cn) (Wenjun Liu)

Cite as: Liu, Y. et al. Back-end-of-line compatible  $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$  ferroelectric devices enabled by microwave annealing. *Chip* 4, 100120 (2025).

<https://doi.org/10.1016/j.chip.2024.100120>

Received: 31 July 2024

Accepted: 9 December 2024

Published online: 20 December 2024

**In this work, we demonstrate an extremely low annealing processing at 300 °C for the crystallization of  $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$  (HZO) films with the adoption of microwave annealing (MWA). Compared to conventional annealing methods, an enhanced double remnant polarization (2Pr) of 55.4  $\mu\text{C}/\text{cm}^2$ , a higher maximum dielectric constant, and nearly wakeup-free were realized by modulating the power of the microwave. It is believed that the increasing loss factor of zirconia with rising temperature allows more energy to be extracted from the microwave and transferred to the ferroelectric HZO molecules, which facilitates the crystallization at low temperature. Furthermore, an amorphous indium gallium zinc oxide ferroelectric field-effect transistor treated with microwave annealing was fabricated, and a competitive memory window of 1.5 V was substantially achieved. These findings offer insights into the integration of  $\text{HfO}_2$  ferroelectric materials in non-volatile memory devices compatible with back-end-of-line (BEOL) in the future.**

**Keywords:** Microwave annealing,  $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$ , Ferroelectric capacitors, Remnant polarization, Back-end of line

## INTRODUCTION

Due to its compatibility with complementary metal-oxide-semiconductor technology and sub-10-nm scalability, the Zr-doped  $\text{HfO}_2$  ( $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$  [HZO]) ferroelectric (FE) device has garnered

significant attention. It is considered as one of the most promising candidates for next-generation embedded non-volatile memories and logic devices<sup>1–4</sup>. With continuous innovations in internal computation, artificial intelligence, flexible synapses and machine learning,  $\text{HfO}_2$ -based FE devices compatible with BEOL process, including FE capacitors (FeCAPs), FE field-effect transistors (FeFETs), FE tunnel junctions, and FE random-access memory, have become focal points for future monolithic three-dimensional integration applications<sup>5–8</sup>. In the industry, high-temperature annealing processes have demonstrated significant usages, including the activation of ion implantation and the supplementation of nitrogen for TiN materials. Nonetheless, low-temperature annealing techniques for FE materials are essential in the BEOL process. The conventional annealing processes, including rapid thermal annealing (RTA) and furnace annealing (FA), which utilize a single mode of energy transfer, often result in the degradation of FE properties when the annealing temperature is reduced. This degradation poses significant challenges for the integration of FE devices<sup>9–14</sup>.

For the integration of FE devices into memory systems compatible with the BEOL process, significant attempts have been made to fully balance the ferroelectricity and thermal budget. These efforts encompass interlayer engineering<sup>15–19</sup>, electrode engineering<sup>20–22</sup>, interface engineering<sup>23</sup>, and modifications to the annealing process rooted in conventional processes<sup>24</sup>. Nonetheless, the non-ideal effects introduced by these methods, such as imprint and wakeup effects, continue to present substantial obstacles for the integration and application in the BEOL processes. Ultimately, this is primarily ascribed to the single energy transfer mechanism of conventional annealing processes, which necessitates additional design modifications in both structure and process to compensate for the performance degradation resulted from reduced annealing temperatures. Our previous work has reported high-performance amorphous indium gallium zinc oxide ( $\alpha$ -IGZO) thin-film transistors processed at a minimal temperature of 189.6 °C via MWA<sup>25</sup>. In addition, Joh et al. presented a focus MWA method, which can effectively crystallize the HZO thin film into FE phase at a low process temperature<sup>26</sup>. Chen et al. investigated the FE HZO dielectric in metal-insulator-metal devices and metal-oxide-semiconductor capacitors by comparing the RTA and MWA<sup>27</sup>. All the aforementioned observations demonstrate that MWA shows significant advantages in device integration during BEOL processes. However, the impact of the process details of MWA on the performance of FE devices and non-ideal effects still requires further exploration.

In this work, an ultra-low crystallization temperature of approximately 300 °C was achieved by using MWA on the HZO film under the microwave power of 1400 W. Furthermore, a competitive  $2P_r$  of 55.4  $\mu\text{C}/\text{cm}^2$ , lower  $E_c$  of 1.09 MV/cm, higher maximum dielectric constant and nearly wakeup free were demonstrated by modulating the power of annealing. In addition, an FeFET with a 10-nm  $\alpha$ -IGZO channel annealing with MWA was fabricated, and an excellent MW of 1.5 V was obtained. The ultra-low crystallization temperature and high-quality FE properties provide an alternative approach for further memory devices compatible with BEOL.

## RESULTS AND DISCUSSIONS

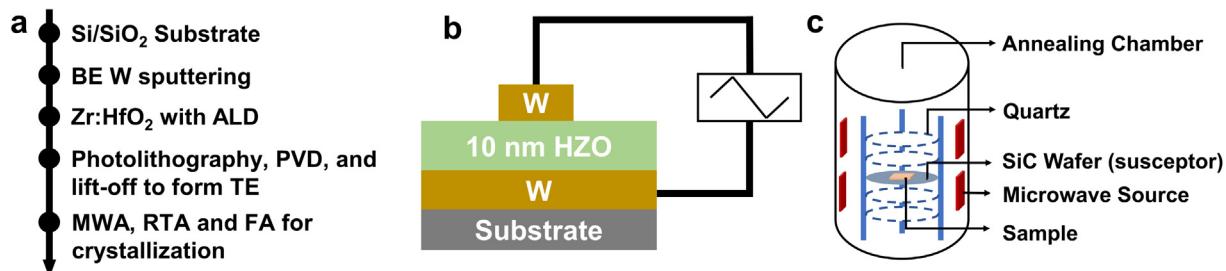

Fig. 1a and b depict the process flow and schematic of the FeCAP, respectively. Fig. 1c shows the schematic diagram of the MWA

process. In the MWA system, eight magnetrons were used as microwave sources, with a frequency of 5.8 GHz. To enhance the microwave absorption efficiency and improve the heating uniformity, quartz and silicon carbide wafers were typically placed inside the chamber as microwave susceptors. Prior to supplying the microwave power, a purge with 1200 s of  $\text{N}_2$  gas was performed within the cavity to ensure the integrity of the gaseous environment inside.

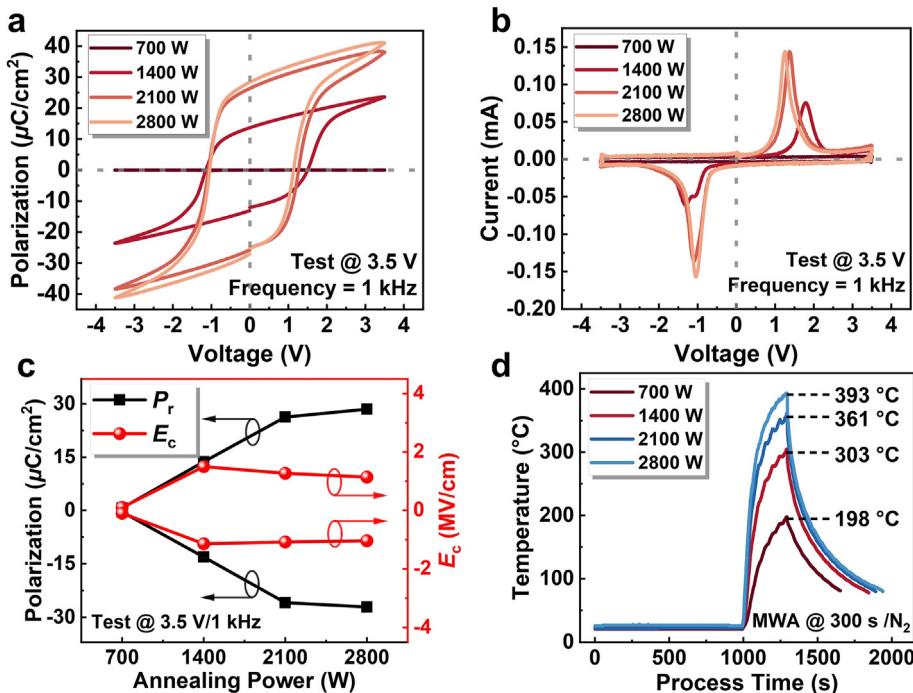

Fig. 2a and b show the remnant polarization-voltage ( $P$ - $V$ ) and dynamic current-voltage ( $I$ - $V$ ) loops of the capacitor under 3.5-V sweeping with different microwave powers from 700 to 2800 W. The extracted  $P_r$  and  $E_c$  as a function of microwave power are presented in Fig. 2c. The capacitors annealed at 1400, 2100 and 2800 W exhibit the  $2P_r$  of 26.8, 52.3 and 55.4  $\mu\text{C}/\text{cm}^2$ , respectively. In addition, as the microwave power reached 2800 W, the  $E_c$  of the FeCAP was continuously decreased to 1.09 MV/cm. This presents a significant advantage

**Fig. 1 | Fabrication and schematic of the processes.** a, The process flow and b, schematic of FE capacitor. c, The schematic diagram of the microwave annealing process. Abbreviation: FE, ferroelectric.

**Fig. 2 | Ferroelectricity of the capacitors annealed at MWA with different microwave powers.** a,  $P$ - $V$  and b, dynamic  $I$ - $V$  loops of capacitor with various annealing powers under 3.5 V at 1 kHz. c, The extracted  $P_r$  and  $E_c$  as a function of microwave power. d, Annealing temperature as a function of time for various MWA processes. Abbreviations: MWA, microwave annealing;  $I$ - $V$ , dynamic current-voltage;  $P$ - $V$ , polarization-voltage.

that distinguishes it from the existing literatures<sup>18,23,24,28,29</sup>. **Fig. 2d** shows the temperature as a function of time for various MWA powers, where the temperature is measured in real time with the adoption of an infrared pyrometer. MWA facilitates the development of ferroelectricity in the capacitor at the temperature of  $\sim 300$  °C with the power of 1400 W, although the cavity temperature remains below 400 °C during the maximum power of MWA process up to 2800 W, which is fully compatible with the BEOL process. The reduced thermal budget is believed to be ascribed to the ability of MWA to directly transfer energy to the target material by vibration of polar molecules, which avoids excessive time and energy consumption during the annealing process. Additionally, during the process of microwave energy transfer, it will selectively couple with materials that exhibit higher dielectric losses, and the loss factor tends to increase with temperature, implying that HZO could absorb more energy for improved crystallization<sup>25–27,30</sup>.

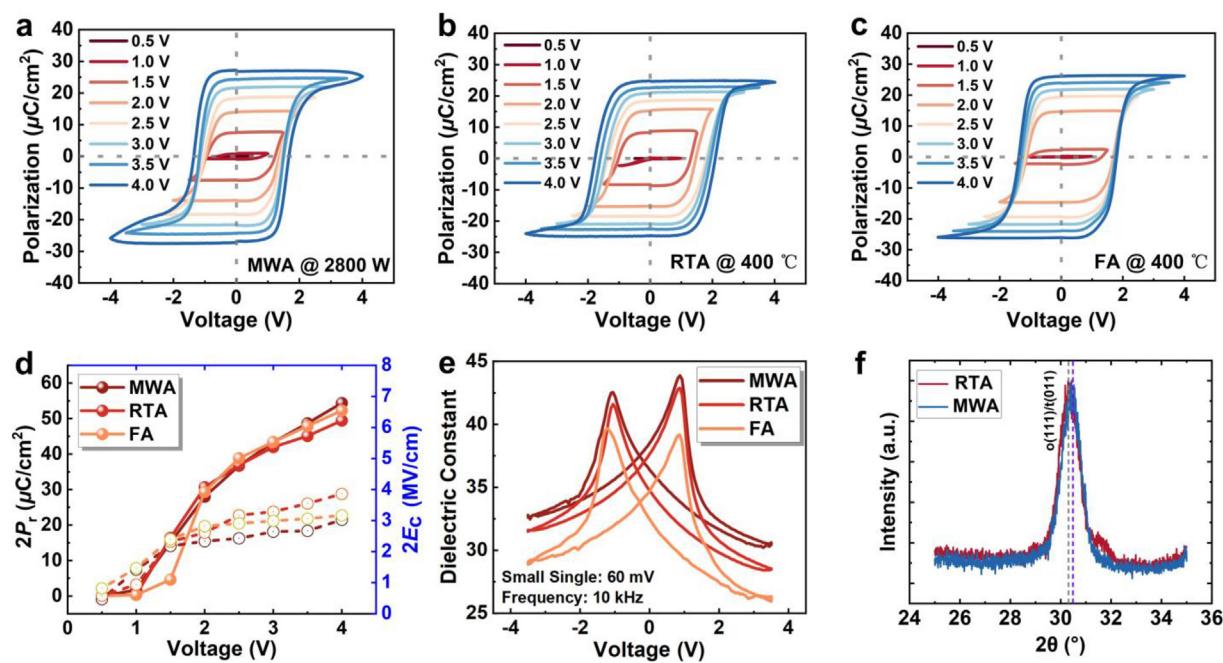

**Fig. 3a–c** present the  $P$ – $V$  curves obtained by the positive-up-negative-down test under the operating voltage ( $V_{op}$ ) of 0.5 to 4.0 V. The extracted  $2P_r$  and  $2E_c$  as a function of  $V_{op}$  for each annealing process are summarized in **Fig. 3d**. Comparative analysis shows that capacitors treated with MWA and RTA demonstrate enhanced  $2P_r$  at low  $V_{op}$  below 2.0 V, exhibiting a superior ferroelectricity in contrast to the capacitor treated with FA. Moreover, the capacitor treated with MWA shows a lower  $2E_c$  than that treated with conventional annealing process. **Fig. 3e** shows the butterfly-shaped curves of dielectric constant–voltage ( $\epsilon$ – $V$ ) for the capacitors treated with different annealing processes, indicating the existence of ferroelectricity<sup>31–33</sup>. The dielectric constants of the monoclinic phase (m-phase), orthorhombic phase (o-phase), and tetragonal phase (t-phase) of most  $\text{HfO}_2$ -based FE films are known to be  $\sim 17$  to 20, 25 to 30, and 35 to 40, respectively<sup>34</sup>. It can be seen that the capacitor treated

with MWA exhibits a higher dielectric constant than those annealed at RTA and FA, which primarily stems from the improved FE-phase ratio<sup>18,35</sup>. As shown in **Fig. 3f**, the diffraction peaks of the HZO films treated with MWA occur at a higher  $2\theta$  angle than the those treated with RTA. Furthermore, the HZO films treated with RTA exhibit an additional diffraction peak around 31.8°, suggesting a more complex internal phase structure.

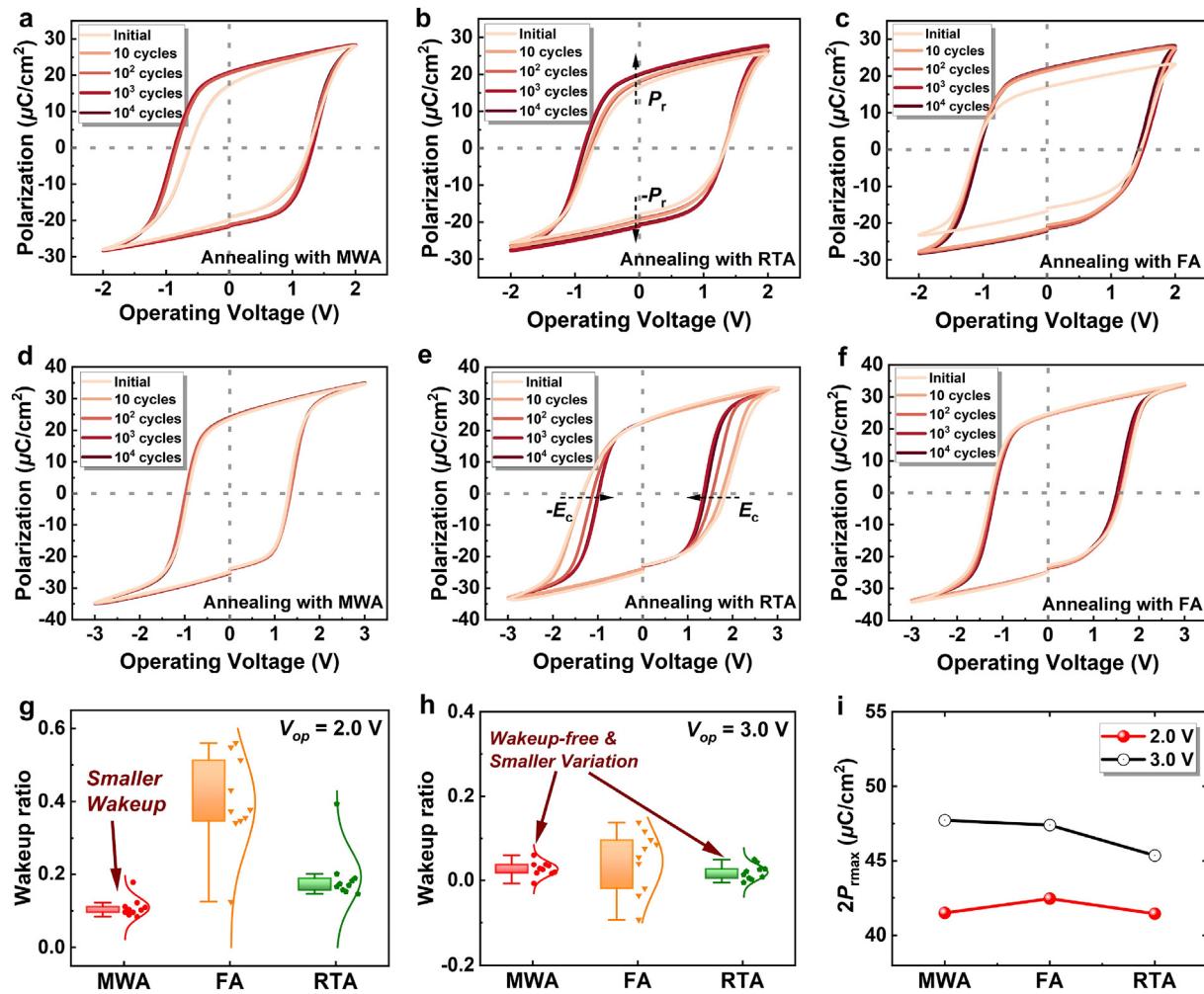

**Fig. 4a–f** show the  $P$ – $V$  loops under 2 to 3 V after wakeup cycling of capacitors treated with different annealing processes. Notably, the capacitors annealed with MWA and FA show their stability after applying 10 wakeup cycles. In contrast, the capacitor annealed at RTA shows a progressive increase in  $P_r$  with continuous wakeup pulses application until reaching its stability after  $10^4$  cycles. Under the high  $V_{op}$  of 3 V, the capacitor treated with MWA exhibits a notably stable  $P_r$  and  $E_c$ . Ten devices from each of annealing processes were randomly selected under uniform environmental conditions to determine their wakeup ratios and maximum  $P_r$ , which are summarized in **Fig. 4g–i**. The capacitor treated with MWA exhibits the lowest wakeup ratio among the above processes under 2 and 3 V sweeping. This enhancement could arise from the unique energy transmission in MWA, contributing to an improved phase structure within the HZO films and a more uniform distribution of oxygen vacancies than conventional annealing processes<sup>36,37</sup>.

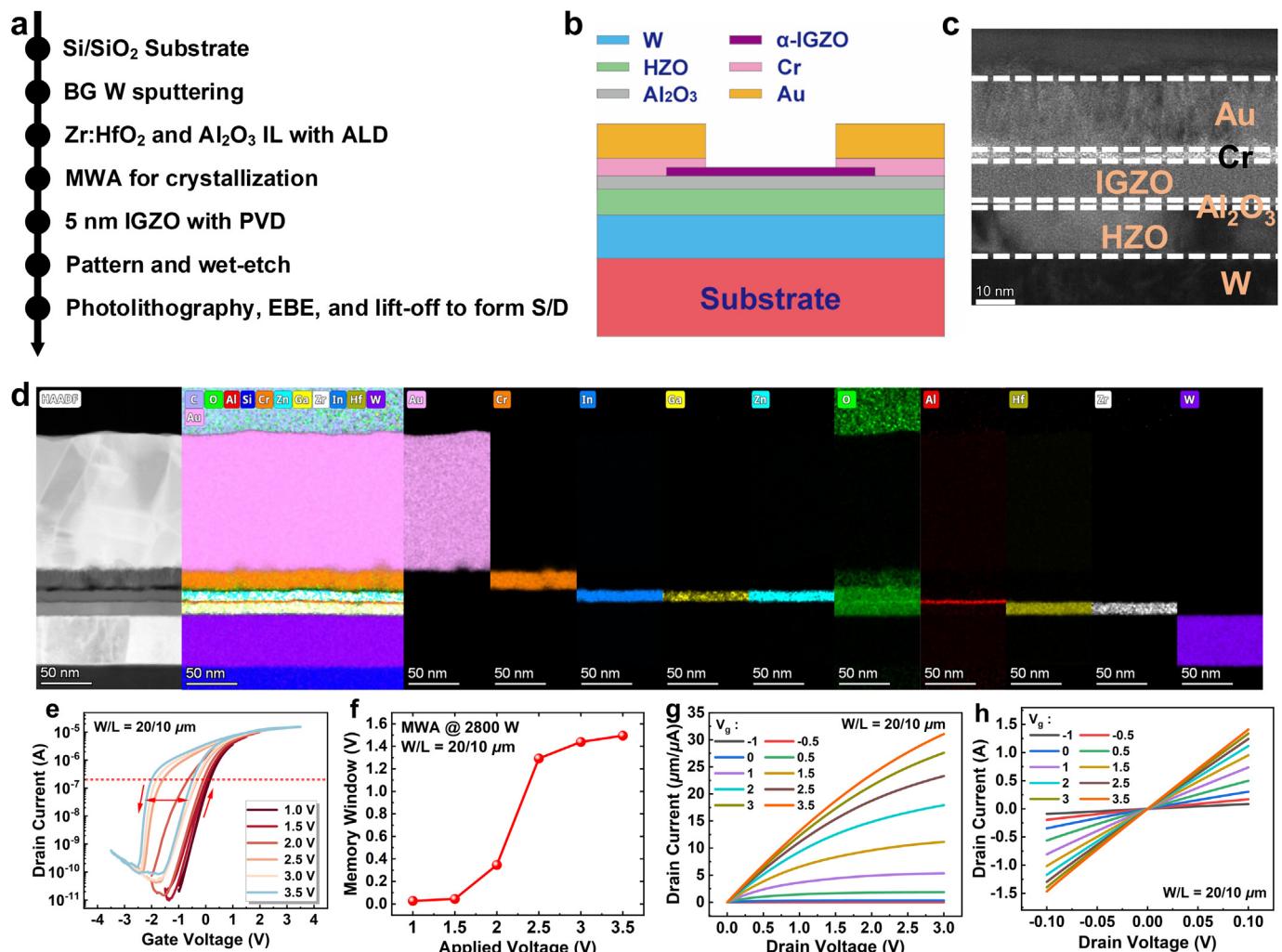

An FeFET with  $\alpha$ -IGZO channel was subjected to MWA at the power of 2800 W for 300 s under  $\text{N}_2$  atmosphere was prepared. To minimize the leakage current and optimize the interface between the  $\alpha$ -IGZO channel and HZO thin film, a 2-nm aluminum oxide layer was introduced as an interfacial layer<sup>38,39</sup>. **Fig. 5a** and **b** show the key processes and schematic structure of the  $\alpha$ -IGZO FeFET, respectively. **Fig. 5c** presents the cross-sectional transmission electron microscopy

**Fig. 3 | The ferroelectricity of fabricated capacitors treated with different annealing processes.** The  $P$ – $V$  curves treated with **a**, MWA, **b**, RTA and **c**, FA under different  $V_{op}$  from 0.5 to 4.0 V at 1 kHz. The extracted **d**,  $2P_r$  and  $2E_c$  as a function of  $V_{op}$ . **e**, Forward and reverse sweeps of dielectric constant–voltage between  $-3.5$  and  $3.5$  MV/cm. **f**, The GIXRD results of the HZO films treated with RTA and MWA. Abbreviations:  $P$ – $V$ , polarization–voltage; MWA, microwave annealing; RTA, rapid thermal annealing; FA, furnace annealing;  $V_{op}$ , operating voltage; GIXRD, grazing-incidence X-ray diffraction; HZO,  $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$ .

**Fig. 4 | The wakeup effect of the FE capacitors treated with different processes.** The  $P$ - $V$  loops under a–c, 2 V and d–f, 3-V sweeping after wakeup cycles. Extracted wakeup ratios ( $1 - P_{r\text{initial}}/P_{r\text{max}}$ ) under g, 2 V and h, 3-V sweeping. i, The extracted  $2P_{r\text{max}}$  under different operating electric fields. Abbreviations:  $P$ - $V$ , polarization-voltage; FE, ferroelectric.

(TEM) images of the  $\alpha$ -IGZO FeFET structure. A clear and sharp interface between the channel and the FE layer guarantees its good interfacial property. Fig. 5d illustrates the high-angle annular dark field (HAADF) image of the fabricated  $\alpha$ -IGZO FeFET and the energy dispersive X-ray spectroscopy (EDS) mapping diagrams of all the elements along the corresponding position. Fig. 5e shows the dual sweep  $I_d$ - $V_g$  curves of the  $\alpha$ -IGZO FeFET with the gate voltage ranging from 1.0 to 3.5 V. It is noticeable that a threshold voltage ( $V_{th}$ ) shift is observed under different gate voltages. This phenomenon is attributed to the accumulation of the positively charged oxygen vacancies, which are generated by the ionization of neutral oxygen vacancies within the semiconductor channel. These positively charged vacancies migrate and accumulate at the interface between the channel and the dielectric layer<sup>25</sup>. Once the gate voltage is removed, the need to maintain charge balance with the FE domains will cause the positively charged oxygen vacancies to become pinned at the interface.

On the other hand, the hydrogen donors introduced into the dielectric layer during the processes may migrate toward the channel under the influence of a negative gate voltage, ionizing to generate extra carriers and positive charges and leading to a threshold voltage shift<sup>40</sup>. A stable FE-type counterclockwise hysteresis is observed for the FeFET and the memroy window (MW) at a constant current of  $W/L \times 10^{-7} \text{ A}$ <sup>41,42</sup>. The extracted MW as a function of sweeping voltage is presented in Fig. 5f, showing that the maximum MW of 1.5 V is achieved under the sweeping voltage of 3.5-V. It is essentially close to its saturated MW even at 2.5 V. Fig. 5g depicts the output characteristics of the  $\alpha$ -IGZO FeFET treated by MWA at 2800 W. With the increase in  $V_{ds}$ , the slope of the output curves also shows an increasing trend, suggesting the effective control ability of the gate voltage over the  $\alpha$ -IGZO FeFET. Fig. 5h shows the output characteristics of the 10-nm  $\alpha$ -IGZO FeFET in the linear region. Observations reveal the device's commendable linearity and saturation characteristics, highlighting a robust ohmic contact between the Cr/Au electrode and the  $\alpha$ -IGZO channel layer.

**Fig. 5** | The structure and electrical characteristics of the α-IGZO FeFET treated with MWA. **a**, The process flow and **b**, the schematic structure of fabricated α-IGZO FeFET. **c**, Cross-sectional TEM and **d**, HAADF and EDS mapping images of the FeFET. **e**, Transfer characteristics under different gate voltages from 1.0 to 3.5 V with a fixed  $V_{ds}$  of 100 mV. **f**, The extracted MW as a function of applied voltage. **g**, Output characteristics of the FeFET. **h**, The output characteristics in linear region. Abbreviations: α-IGZO, amorphous indium zinc oxide; MWA, microwave annealing; FeFET, ferroelectric field-effect transistor; TEM, transmission electron microscopy; HAADF, high-angle annular dark field; EDS, energy dispersive X-ray spectroscopy; MW, memory window.

## CONCLUSION

In summary, we have achieved an ultra-low annealing temperature of approximately 300 °C with the adoption of the MWA process under 1400 W. Compared to conventional processes, a superior  $2P_r$  of 55.4  $\mu$ C/cm<sup>2</sup>, lower  $E_c$  of 1.09 MV/cm, and nearly wakeup free were demonstrated in the FeCAPs treated with MWA under 2800 W. Additionally, a considerable MW of 1.5 V was achieved in α-IGZO FeFETs. These findings suggest that the application of MWA is a feasible approach to optimize both the ferroelectricity and memory properties for FE device compatible with BEOL.

## METHODS

**Fabrication of the ferroelectric capacitor** Firstly, 30-nm tungsten (W) bottom electrodes were deposited onto the p-Si/SiO<sub>2</sub> (90 nm) substrate by physical vapor deposition (PVD). Next, the 10-nm HZO thin

film was prepared by plasma-enhanced atomic layer deposition (PEALD) at 280 °C, using Hf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>, Zr[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>, and oxygen plasma as the Hf, Zr, and oxygen sources, respectively. Afterwards, photolithography and PVD were used to pattern and sputter the 30-nm W top electrodes with an area of 100 × 100  $\mu$ m<sup>2</sup>. Finally, the FeCAPs with conventional HZO film were subjected to MWA under different microwave powers from 700 to 2800 W for 300 s under N<sub>2</sub> atmosphere, and the MWA process was performed using DGST-axom 200 at 5.8 GHz.

**Fabrication of the amorphous indium gallium zinc oxide ferroelectric field-effect transistor** Firstly, a 50-nm W bottom gate was grown by PVD at room temperature on a 90-nm SiO<sub>2</sub>/p-Si substrate. Accordingly, a 15-nm HZO FE layer was prepared using PEALD at 280 °C. The deposited reactant precursors are consistent with the preparation of FeCAPs. Subsequently, a 2-nm Al<sub>2</sub>O<sub>3</sub> layer was deposited onto the stack by thermal atomic layer deposition at 200 °C. Al(CH<sub>3</sub>)<sub>3</sub> and H<sub>2</sub>O were chosen as aluminum and oxygen precursors.

Then, the device went through MWA at the power of 2800 W for 300 s under  $N_2$  atmosphere for crystallization. After that, a 10 nm  $\alpha$ -IGZO was deposited by PVD at room temperature, and the active channel layer was patterned by photolithography and wet etching (diluted HCl). The channel length and width are 10 and 20  $\mu\text{m}$ , respectively. Finally, photolithography and electron beam evaporation were applied to pattern and form source and drain electrodes of Cr/Au (10/50 nm).

**Measurement of the fabricated devices** The microstructure and element analysis of the fabricated FeFETs were characterized by TEM (TalosF200XG2), HAADF, and EDS. The electrical performance was measured using a semiconductor device analyzer (Agilent B1500A) in a dark box at room temperature. The ferroelectricity of the devices was measured by FE test system (Precision Premier II).

## REFERENCES

1. Schroeder, U., Park, M. H., Mikolajick, T. & Hwang, C. S. The fundamentals and applications of ferroelectric  $\text{HfO}_2$ . *Nat. Rev. Mater.* **7**, 653–669 (2022). <https://doi.org/10.1038/s41578-022-00431-2>.

2. Park, M. H. et al. Ferroelectricity and antiferroelectricity of doped thin  $\text{HfO}_2$ -based films. *Adv. Mater.* **27**, 1811–1831 (2015). <https://doi.org/10.1002/adma.201404531>.

3. Choi, Y., Park, H., Han, C., Min, J. & Shin, C. Improved remnant polarization of Zr-doped  $\text{HfO}_2$  ferroelectric film by  $\text{CF}_4/\text{O}_2$  plasma passivation. *Sci. Rep.* **12**, 16750 (2022). <https://doi.org/10.1038/s41598-022-21263-8>.

4. Cho, H. W. et al. Direct growth of orthorhombic  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  thin films for hysteresis-free  $\text{MoS}_2$  negative capacitance field-effect transistors. *npj 2D Mater. Appl.* **5**, 46 (2021). <https://doi.org/10.1038/s41699-021-00229-w>.

5. Sun, C. et al. Temperature-dependent operation of  $\text{InGaZnO}$  ferroelectric thin-film transistors with a metal-ferroelectric-metal-insulator-semiconductor structure. *IEEE Electron Device Lett.* **42**, 1786–1789 (2021). <https://doi.org/10.1109/led.2021.3121677>.

6. Wang, Y. et al. A stable rhombohedral phase in ferroelectric  $\text{Hf}(\text{Zr})_{1+x}\text{O}_2$  capacitor with ultralow coercive field. *Science* **381**, 558–563 (2023). <https://doi.org/10.1126/science.adf6137>.

7. Kim, B. H. et al. Low operating voltage and immediate read-after-write of HZO-based Si ferroelectric field-effect transistors with high endurance and retention characteristics. *Adv. Electron. Mater.* **10**, 2300327 (2024). <https://doi.org/10.1002/aelm.202300327>.

8. Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. *Nature* **432**, 488–492 (2004). <https://doi.org/10.1038/nature03090>.

9. Hur, J., Luo, Y.-C., Tasneem, N., Khan, A. I. & Yu, S. Ferroelectric hafnium zirconium oxide compatible with back-end-of-line process. *IEEE Trans. Electron Devices* **68**, 3176–3180 (2021). <https://doi.org/10.1109/led.2021.3072610>.

10. Dutta, S. et al. Logic compatible high-performance ferroelectric transistor memory. *IEEE Electron Device Lett.* **43**, 382–385 (2022). <https://doi.org/10.1109/led.2022.3148669>.

11. Chernikova, A. G. et al. Improved ferroelectric switching endurance of La-doped  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  thin films. *ACS Appl. Mater. Interfaces* **10**, 2701–2708 (2018). <https://doi.org/10.1021/acsami.7b15110>.

12. Liu, Y.-C. et al. Back-end of line compatible  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2/\text{ZrO}_2/\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  stack achieving  $2P_r$  of 39.6  $\mu\text{C}/\text{cm}^2$  and endurance exceeding  $10^{10}$  cycles under low-voltage operation. *IEEE Electron Device Lett.* **45**, 388–391 (2024). <https://doi.org/10.1109/led.2023.3346912>.

13. Fields, S. S. et al. Phase-exchange-driven wake-up and fatigue in ferroelectric hafnium zirconium oxide films. *ACS Appl. Mater. Interfaces* **12**, 26577–26585 (2020). <https://doi.org/10.1021/acsami.0c03570>.

14. Hyuk Park, M., Kim, H. J., Kim, Y. J., Moon, T. & Hwang, C. S. The effects of crystallographic orientation and strain of thin  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  film on its ferroelectricity. *Appl. Phys. Lett.* **104**, 072901 (2014). <https://doi.org/10.1063/1.4866008>.

15. Yu, E., Lyu, X., Si, M., Ye, P. D. & Roy, K. Interfacial layer engineering in sub-5 nm HZO: enabling low-temperature process, low-voltage operation, and high robustness. *IEEE Trans. Electron Devices* **70**, 2962–2969 (2023). <https://doi.org/10.1109/led.2023.3270397>.

16. Li, Y.-C. et al. Dual  $\text{Al}_2\text{O}_3/\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  stack thin films for improved ferroelectricity and reliability. *IEEE Electron Device Lett.* **43**, 1235–1238 (2022). <https://doi.org/10.1109/led.2022.3185246>.

17. Chen, Y.-F. et al. Wake-up free ferroelectric capacitor with quadruple-level storage by inserting  $\text{ZrO}_2$  interlayer and bottom layer in  $\text{HfZrO}_x$ . *IEEE Electron Device Lett.* **44**, 400–403 (2023). <https://doi.org/10.1109/led.2023.3235715>.

18. Liu, Y.-C. et al. Back-end of line compatible  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  with  $\text{ZrO}_2$  seed layer for enhanced ferroelectricity. *IEEE Electron Device Lett.* **44**, 1116–1119 (2023). <https://doi.org/10.1109/led.2023.3278291>.

19. Qi, Y., Xu, X., Krylov, I. & Eizenberg, M. Ferroelectricity of as-deposited HZO fabricated by plasma-enhanced atomic layer deposition at 300 °C by inserting  $\text{TiO}_2$  interlayers. *Appl. Phys. Lett.* **118**, 032906 (2021). <https://doi.org/10.1063/5.0037887>.

20. Cao, R. et al. Effects of capping electrode on ferroelectric properties of  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  thin films. *IEEE Electron Device Lett.* **39**, 1207–1210 (2018). <https://doi.org/10.1109/led.2018.2846570>.

21. Wang, X. et al. Understanding the effect of top electrode on ferroelectricity in atomic layer deposited  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  thin films. *ACS Appl. Mater. Interfaces* **15**, 15657–15667 (2023). <https://doi.org/10.1021/acsami.2c22263>.

22. Cao, R. et al. Improvement of endurance in HZO-based ferroelectric capacitor using Ru electrode. *IEEE Electron Device Lett.* **40**, 1744–1747 (2019). <https://doi.org/10.1109/led.2019.2944960>.

23. Tai, L. et al. Toward low-thermal-budget processing in ferroelectric  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  thin films by ozone interface oxidation. *IEEE Electron Device Lett.* **44**, 1959–1962 (2023). <https://doi.org/10.1109/led.2023.3325426>.

24. Xiao, D.-Q. et al. Low thermal budget fabrication and performance comparison of MFM capacitors with thermal and plasma-enhanced atomic layer deposited  $\text{Hf}_{0.45}\text{Zr}_{0.55}\text{O}_x$  ferroelectrics. *IEEE Trans. Electron Devices* **68**, 6359–6364 (2021). <https://doi.org/10.1109/led.2021.3118665>.

25. Pi, T. et al. High-performance a-IGZO TFT fabricated with ultralow thermal budget via microwave annealing. *IEEE Trans. Electron Devices* **69**, 156–159 (2022). <https://doi.org/10.1109/led.2021.3126692>.

26. Joh, H. et al. Flexible ferroelectric hafnia-based synaptic transistor by focused-microwave annealing. *ACS Appl. Mater. Interfaces* **14**, 1326–1333 (2021). <https://doi.org/10.1021/acsami.1c16873>.

27. Chen, Y.-H., Su, C.-J., Hu, C. & Wu, T.-L. Effects of annealing on ferroelectric hafnium-zirconium-oxide-based transistor technology. *IEEE Electron Device Lett.* **40**, 467–470 (2019). <https://doi.org/10.1109/led.2019.2895833>.

28. Kim, S. J. et al. Low-thermal-budget (300 °C) ferroelectric  $\text{TiN}/\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2/\text{TiN}$  capacitors realized using high-pressure annealing. *Appl. Phys. Lett.* **119**, 242901 (2021). <https://doi.org/10.1063/5.0075466>.

29. Lehninger, D. et al. Back-End-of-Line compatible low-temperature furnace anneal for ferroelectric hafnium zirconium oxide formation. *Phys. Status Solidi (A) Appl. Mater. Sci.* **217**, 1900840 (2020). <https://doi.org/10.1002/pssa.201900840>.

30. Zhu, B. et al. Dielectric enhancement of atomic layer-deposited  $\text{Al}_2\text{O}_3/\text{ZrO}_2/\text{Al}_2\text{O}_3$  MIM capacitors by microwave annealing. *Nanoscale Res. Lett.* **14**, 53 (2019). <https://doi.org/10.1186/s11671-019-2874-5>.

31. Yi, S.-H., Lin, B.-T., Hsu, T.-Y., Shieh, J. & Chen, M.-J. Modulation of ferroelectricity and antiferroelectricity of nanoscale  $\text{ZrO}_2$  thin films using ultrathin interfacial layers. *J. Eur. Ceram. Soc.* **39**, 4038–4045 (2019). <https://doi.org/10.1016/j.jeurceramsoc.2019.05.065>.

32. Kashir, A. & Hwang, H. Ferroelectric and dielectric properties of  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  thin film near morphotropic phase boundary. *Phys. Status Solidi (A) Appl. Mater. Sci.* **218**, 2000819 (2021). <https://doi.org/10.1002/pssa.202000819>.

33. Goh, Y., Hwang, J. & Jeon, S. Excellent reliability and high-speed antiferroelectric  $\text{HfZrO}_2$  tunnel junction by a high-pressure annealing process and built-in bias engineering. *ACS Appl. Mater. Interfaces* **12**, 57539–57546 (2020). <https://doi.org/10.1021/acsami.0c15091>.

34. Park, M. H. et al. Effect of Zr content on the wake-up effect in  $\text{Hf}_{1-x}\text{Zr}_x\text{O}_2$  films. *ACS Appl. Mater. Interfaces* **8**, 15466–15475 (2016). <https://doi.org/10.1021/acsami.6b03586>.

35. Estandia, S. et al. Engineering ferroelectric  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  thin films by epitaxial stress. *ACS Appl. Electron Mater.* **1**, 1449–1457 (2019). <https://doi.org/10.1021/acsaelm.9b00256>.

36. Li, X. et al. In-depth investigation of seed layer engineering in ferroelectric  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  film: wakeup-free achievement and reliability mechanisms. *IEEE Trans. Electron Devices* **71**, 1048–1053 (2024). <https://doi.org/10.1109/led.2023.3342770>.

37. Weng, Z. et al. Wake-up free La-doped  $\text{HfO}_2$ - $\text{ZrO}_2$  ferroelectrics achieved with an atomic layer-specific doping technique. *IEEE Electron Device Lett.* **43**, 1665–1668 (2022). <https://doi.org/10.1109/led.2022.3203472>.

38. Ni, K. et al. Critical role of interlayer in  $\text{Hf}_0.5\text{Zr}_{0.5}\text{O}_2$  ferroelectric FET nonvolatile memory performance. *IEEE Trans. Electron Devices* **65**, 2461–2469 (2018). <https://doi.org/10.1109/led.2018.2829122>.

39. Cui, T. et al. Can interface layer be really free for  $Hf_xZr_{1-x}O_2$  based ferroelectric field-effect transistors with oxide semiconductor channel? *IEEE Electron Device Lett.* **45**, 368–371 (2024). <https://doi.org/10.1109/led.2024.3355523>.

40. Liu, G. et al. Hydrogen-related instability of IGZO field-effect transistors. *IEEE Trans. Electron Devices* **71**, 2995–3001 (2024). <https://doi.org/10.1109/TED.2024.3372486>.

41. Meng, W. et al. Performance improvement of  $Hf_{0.45}Zr_{0.55}O_x$  ferroelectric field effect transistor memory with ultrathin Al–O bonds-modified  $InO_x$  channels. *Nanotechnology* **34**, 175204 (2023). <https://doi.org/10.1088/1361-6528/acb653>.

42. Li, Q. et al. High- performance ferroelectric field-effect transistors with ultra-thin indium tin oxide channels for flexible and transparent electronics. *Nat. Commun.* **15**, 2686 (2024). <https://doi.org/10.1038/s41467-024-46878-5>.

## MISCELLANEA

**Funding** This work was supported by National Key Research and Development Program of China under Grant 2021YFB3202500, and Shanghai Municipal Science and Technology Commission under Grant 23511102300.

**Author contributions** **Yinchi Liu:** Writing – original draft, Methodology, Investigation, Conceptualization. **Hao Zhang:** Validation, Methodology, Formal analysis. **Jining Yang:** Visualization, Software, Data curation. **Dmitriy Anatolyevich Golosov:** Validation, Resources, Methodology. **Xiaohan Wu:** Methodology, Data curation.

**Chenjie Gu:** Software, Resources, Project administration, Methodology. **Shijin Ding:** Visualization, Validation, Software, Resources, Methodology, Formal analysis. **Wenjun Liu:** Writing – review & editing, Writing – original draft, Supervision, Project administration, Methodology, Formal analysis, Conceptualization.

**Declaration of Competing Interest** The authors declare no competing interests.

© 2024 The Author(s). Published by Elsevier B.V. on behalf of Shanghai Jiao Tong University. This is an open access article under the CC BY license (<http://creativecommons.org/licenses/by/4.0/>).