Special Topic: Novel Memory Materials and Devices: Ferroelectrics and Oxide Semiconductors

# Enhanced memory window and reliability of $\alpha$ -IGZO FeFET enabled by atomic-layer-deposited $\text{HfO}_2$ interfacial layer

Yinchi LIU<sup>1,2</sup>, Xun LU<sup>1</sup>, Shiyu LI<sup>1</sup>, Hao ZHANG<sup>1</sup>, Jining YANG<sup>1</sup>, Yeye GUO<sup>1</sup>,

Dmitriy Anatolyevich GOLOSOV<sup>3</sup>, Chenjie GU<sup>4</sup>, Hongliang LU<sup>1</sup>, Zhigang JI<sup>5\*</sup>,

Shijin DING<sup>1</sup> & Wenjun LIU<sup>1,2\*</sup>

<sup>1</sup>School of Microelectronics, Fudan University, Shanghai 200433, China

<sup>2</sup>Shaoxin Laboratory, Shaoxing 312000, China

<sup>3</sup>Belarusian State University of Informatics and Radioelectronics, Minsk 220013, Belarus

<sup>4</sup>School of Physical Science and Technology, Ningbo University, Ningbo 315211, China

<sup>5</sup>National Key Laboratory of Science and Technology on Micro/Nano Fabrication, Shanghai Jiao Tong University, Shanghai 200240, China

Received 14 September 2024/Revised 22 November 2024/Accepted 30 April 2025/Published online 15 May 2025

**Abstract** The ferroelectric field-effect transistor (FeFET) with an amorphous indium–gallium–zinc oxide ( $\alpha$ -IGZO) channel and an atomic-layer-deposited 2 nm  $\text{HfO}_2$  interfacial layer (IL) was designed and fabricated to optimize both memory window (MW) and reliability. Compared with the FeFET without IL, the FeFET with 2 nm  $\text{HfO}_2$  IL achieved an enhanced MW of 1.1 V at a reliable operating voltage with ultrafast current–voltage operation and an approximately 1000 times improvement in endurance with an available MW of  $\sim$ 0.85 V after exerting pulses over  $10^7$  cycles while maintaining retention of over 10 years. This work proposes an effective strategy to enhance MW and reliability for future nonvolatile memory applications.

**Keywords**  $\text{HfO}_2$ , interfacial layer,  $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$ , memory window, reliability

**Citation** Liu Y C, Lu X, Li S Y, et al. Enhanced memory window and reliability of  $\alpha$ -IGZO FeFET enabled by atomic-layer-deposited  $\text{HfO}_2$  interfacial layer. Sci China Inf Sci, 2025, 68(6): 160405, <https://doi.org/10.1007/s11432-024-4429-7>

## 1 Introduction

Recently, ferroelectric field-effect transistors (FeFETs) based on metal oxide channel materials, such as amorphous indium–gallium–zinc oxide ( $\alpha$ -IGZO) [1], indium oxide ( $\text{In}_2\text{O}_3$ ) [2], and tungsten (W)-doped  $\text{In}_2\text{O}_3$  [3], have been considered promising candidates for prospective applications in monolithic 3D integration toward large-scale memory, motivated in part by the low power consumption, high writing speed, complementary metal–oxide–semiconductor technology compatibility, and outstanding scalability of  $\text{HfO}_2$ -based FeFET [4–6]. However, the application of FeFETs is still restricted by their narrow memory window (MW) and poor endurance, which are not only associated with the ferroelectric (FE) layer itself but also linked to the interface between the channel and the gate insulator [7]. Significant efforts and progress have been made to optimize the memory properties of FeFETs, such as interfacial layer (IL) thickness reduction via oxygen scavenging in Si-based FeFET [8] and IL-free gate stacks in  $\alpha$ -IGZO FeFET [9]. However, a large gate voltage drop across the low-k IL and an inferior MW in the IL-free gate structure are unexpectedly obtained. The memory performance of FeFETs was improved by introducing  $\text{Al}_2\text{O}_3$  IL [7] and  $\text{Al}_2\text{O}_3/\text{ZrO}_2$  stack IL [10]. By inserting  $\text{Al}_2\text{O}_3$  IL and scaling down the  $\text{In}_2\text{O}_3$  channel length, Lin et al. [2] obtained and reported an optimized MW, which is measured by the ultrafast current–voltage (UFIV) operation. Comparatively, the combination of the metal sacrificial layer and high-k IL in oxide FeFET could be an effective method for device property enhancement [11]. In this work,  $\alpha$ -IGZO FeFETs with a 2 nm  $\text{HfO}_2$  IL were constructed. The fabricated FeFET with  $\text{HfO}_2$  IL exhibited a competitive MW of  $\sim$ 1.1 V and enhanced program and erase speeds. Subsequently, excellent reliability with continuous loading over  $10^7$  cycles and extrapolated retention of  $>10$  years were achieved.

\* Corresponding author (email: zhigangji@sjtu.edu.cn, wjliu@fudan.edu.cn)

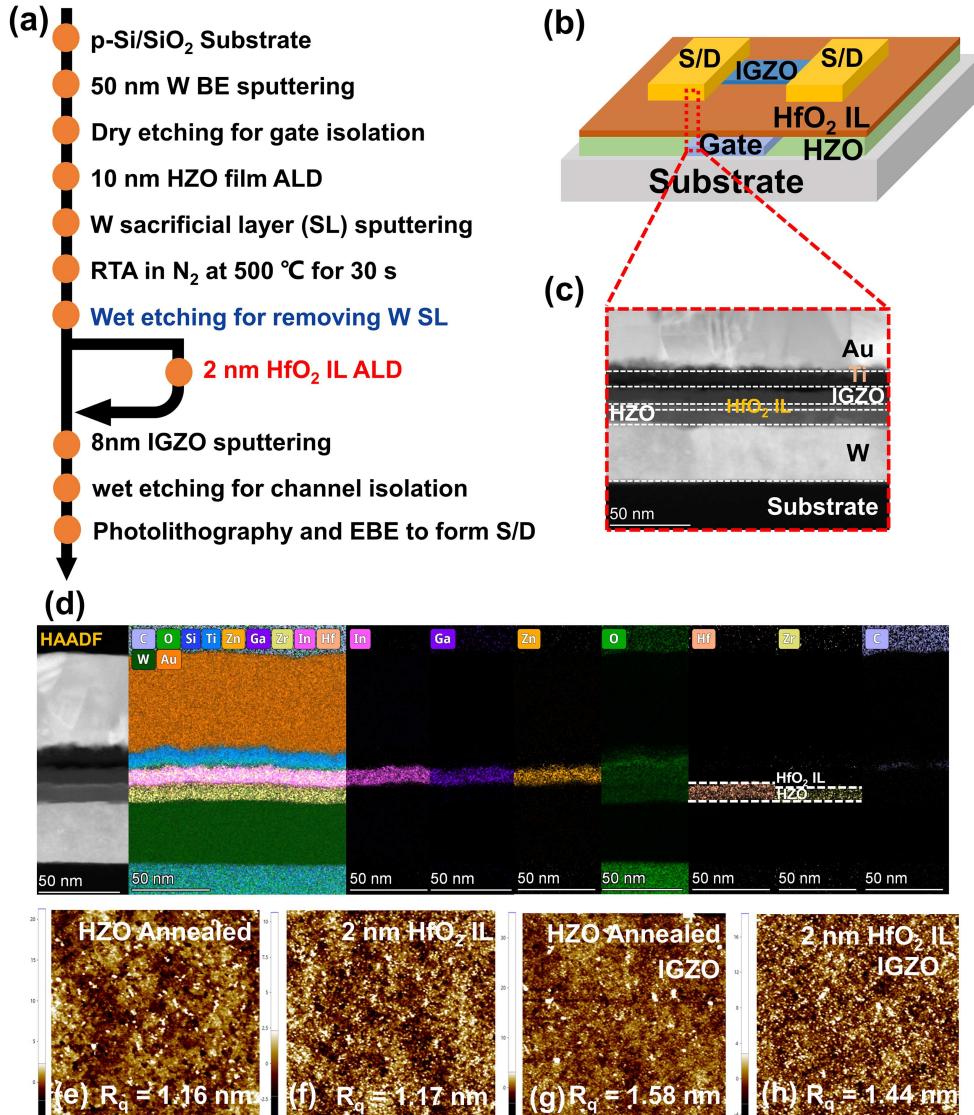

**Figure 1** (Color online) (a) Process flow, (b) schematic, (c) cross-sectional TEM, and (d) HAADF and EDS mapping images of the fabricated FeFET with 2 nm HfO<sub>2</sub> IL. The distribution mapping of the elements In, Ga, Zn, O, Hf, Zr, and C is presented below. AFM images of (e) annealed HZO film, (f) HfO<sub>2</sub> IL, (g) IGZO on annealed HZO, and (h) IGZO on HfO<sub>2</sub> IL with the scanning size of 5  $\mu\text{m} \times 5 \mu\text{m}$ .

## 2 Device fabrication

The process flows of the fabrication of FeFETs with and without HfO<sub>2</sub> IL are shown in Figure 1(a). First, a 50 nm W thin film was deposited onto the SiO<sub>2</sub>/p-Si substrate using physical vapor deposition, followed by photolithography and SF<sub>6</sub>/CHF<sub>3</sub> inductively coupled plasma dry etching for gate isolation. Next, 12 nm Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> (HZO) was prepared by atomic layer deposition (ALD) at 280°C with Hf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>, Zr[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>, and O<sub>2</sub> as Hf, Zr, and oxygen precursors, respectively. The W was then deposited on the thin film as the capping layer because it effectively induces HZO crystallization [12]. Thereafter, the thin films went through rapid thermal annealing at 500°C for 30 s in N<sub>2</sub> atmosphere for crystallization, and the W capping layer was removed by wet etching with H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O = 1:2 and a trace amount of NH<sub>4</sub>OH. Afterward, 2 nm HfO<sub>2</sub> was grown by ALD at 250°C as IL, and a control device without HfO<sub>2</sub> IL was also prepared. Subsequently, 8 nm  $\alpha$ -IGZO was constructed by radio frequency magnetron sputtering at room temperature, and the active channel layer was patterned by photolithography and wet etching (diluted HCl). Finally, photolithography and electron beam evaporation were adopted to pattern and form the source and drain contacts of Ti (10 nm)/Au (50 nm). The surface roughness of the FE dielectric layer and semiconductor channel layer was measured using atomic force microscopy (AFM). The microstructure

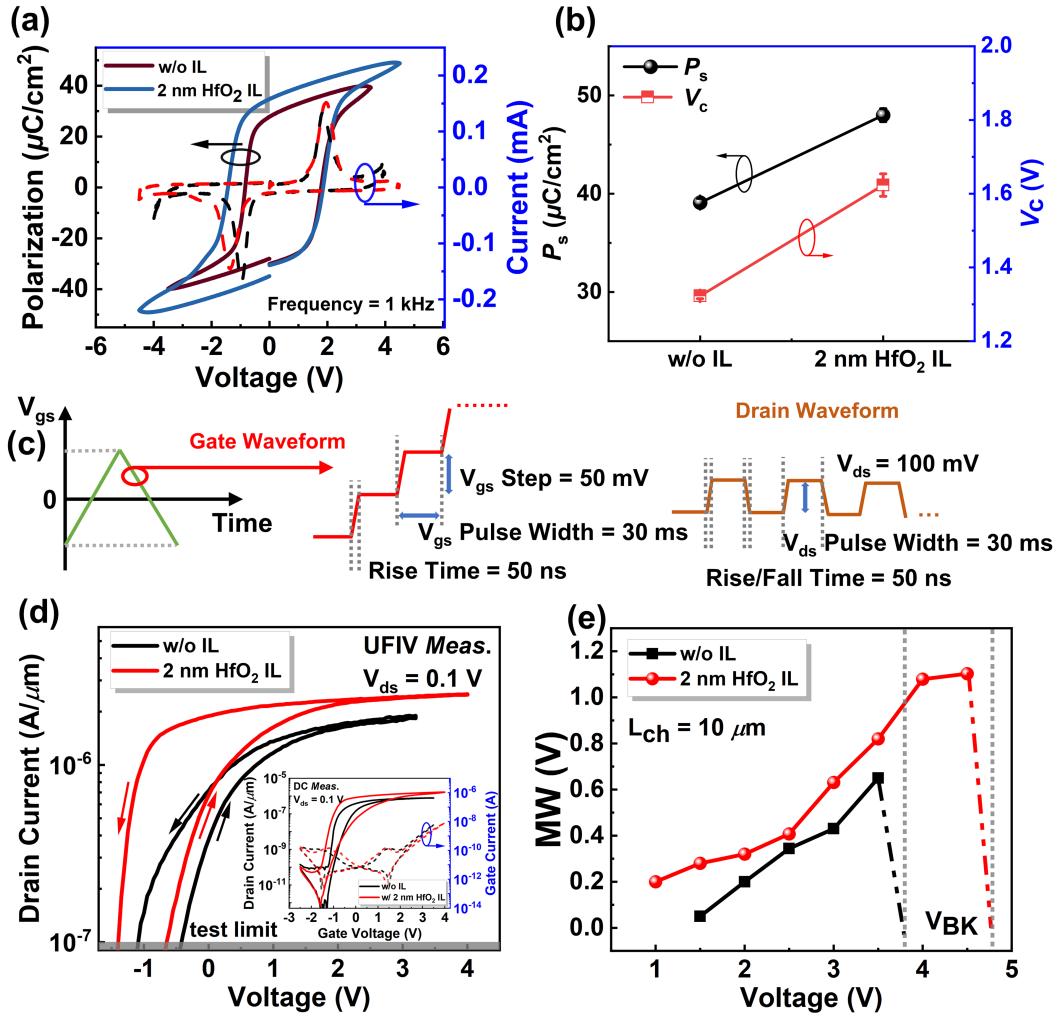

**Figure 2** (Color online) (a)  $P$ - $V$  and dynamic  $I$ - $V$  loops of the FE capacitor based on the MFIM structure without and with 2 nm HfO<sub>2</sub> IL under a reliable operating voltage. (b)  $P_s$  and  $V_c$  of the MFIM structure. (c) Schematic of the UFIV measurements. (d)  $I_d$ - $V_g$  of  $\alpha$ -IGZOFeFETs with different gate stacks under the UFIV test method. The  $I_d$ - $V_g$  and  $I_g$ - $V_g$  curves of the FeFETs based on the DC measurements are shown in the inset in (d) as basic information. (e) MW of  $\alpha$ -IGZO FeFETs without and with 2 nm HfO<sub>2</sub> IL at  $V_{ds}$  of 0.1 V.

and element analyses of the fabricated FeFETs were characterized by transmission electron microscopy (TEM), high-angle annular dark field (HAADF), and energy-dispersive X-ray spectroscopy (EDS). The electrical performance was measured using a semiconductor device analyzer (Agilent B1500A). The ferroelectricity of the devices was measured using a field-effect test system (Precision Premier II).

### 3 Results and discussion

Figure 1(b) shows the schematic view of the FeFET. Two different FeFET structures were fabricated. One sample without IL was designed as the control device, and the other sample with 2 nm HfO<sub>2</sub> IL was used as the experimental device. Figure 1(c) presents the cross-sectional high-resolution TEM images of the FeFET with HfO<sub>2</sub> IL, confirming its clear structure and good interfacial property. Figure 1(d) depicts the HAADF image of the FeFET and the EDS distribution mapping diagrams of all of the elements, showing the distributed elements In, Ga, Zn, O, Hf, Zr, and C in the fabricated FeFET. Notably, the FeFET with HfO<sub>2</sub> IL exhibits sharp interfaces both structurally and chemically without obvious interdiffusion. In addition, the difference in the position and thickness of the elements Hf and Zr verifies the presence of 2 nm HfO<sub>2</sub> IL. Figures 1(e)–(h) show the AFM images of annealed HZO film, HfO<sub>2</sub> IL, IGZO on annealed HZO, and IGZO on HfO<sub>2</sub> IL, where the surface roughness values were 1.16, 1.17, 1.58, and 1.44 nm, respectively.

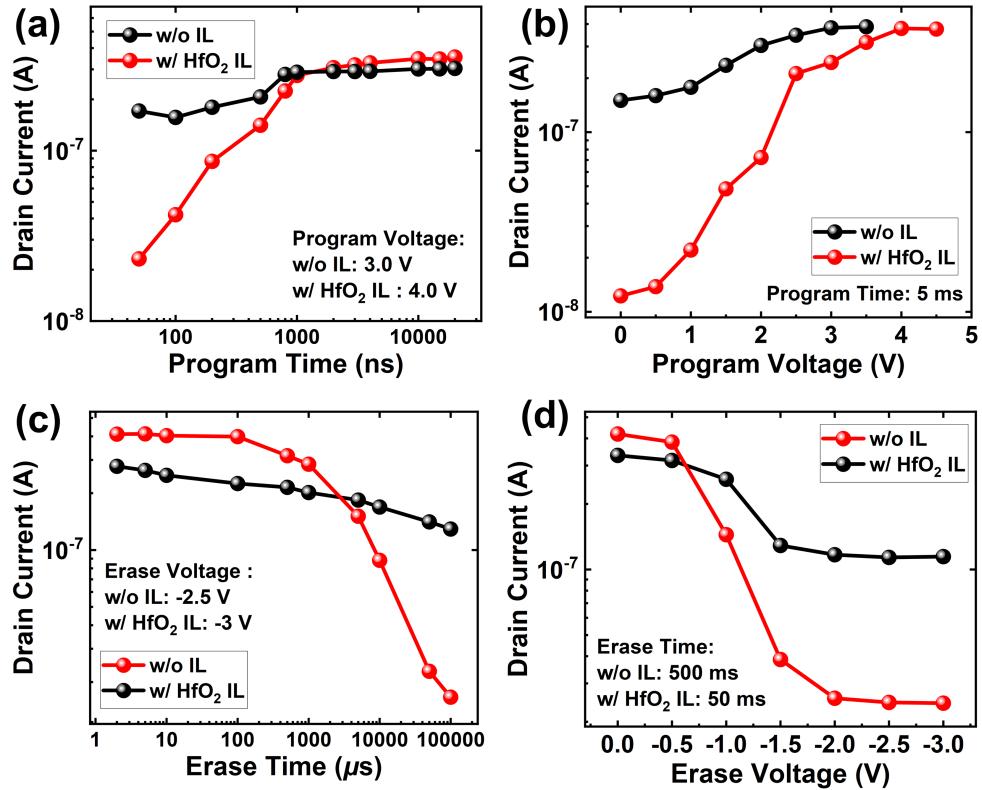

**Figure 3** (Color online) Dependence of  $I_d$  on the (a) program time, (b) program voltage, (c) erase time, and (d) erase voltage of FeFETs with and without  $\text{HfO}_2$  IL.

Figure 2(a) displays the polarization-voltage ( $P$ - $V$ ) and dynamic current-voltage ( $I$ - $V$ ) characteristics at reliable voltage ranges of FE capacitors without and with 2 nm  $\text{HfO}_2$  IL. Compared with the control device, larger spontaneous polarization ( $P_s$ ) and coercive voltage ( $V_c$ ) were observed in the capacitor with  $\text{HfO}_2$  IL, as shown in Figure 2(b). Although the  $\text{HfO}_2$  IL could induce undesired voltage distribution, it substantially increases the reliable voltage range and enhances  $P_s$  under a higher operating voltage ( $V_{op}$ ). Notably, large  $P_s$  and  $V_c$  values could improve the memory properties of FeFET [11,13]. Accordingly, the MW of the FeFETs was measured using the UFIV method, which is reported to suppress charge trapping during voltage sweep [2, 7]. Figure 2(c) presents the detailed waveforms and parameters obtained from the UFIV operation. The measurement step and pulse width of gate voltage ( $V_g$ ) are 50 mV and 30 ms, respectively. Similarly, the drain voltage ( $V_d$ ) is applied with an amplitude of 100 mV and a pulse width of 30 ms. Figure 2 shows the  $I_d$ - $V_g$  curves obtained from the UFIV measurements at  $V_d = 0.1$  V for FeFETs with and without  $\text{HfO}_2$  IL. The inset in Figure 2(d) shows the  $I_d$ - $V_g$  and  $I_g$ - $V_g$  curves obtained from the DC measurements. A stable FE-type counterclockwise hysteresis is observed for all FeFETs, with MW up to 1.1 V by integrating 2 nm  $\text{HfO}_2$  IL. These results reflect a positive correlation between the MW of FeFET and  $P_s$  and  $2V_c$ , which is consistent with previous reports [2, 7]. Furthermore, the DC measurements shown in the inset in Figure 2(d) reveal similar MW enhancement and negative differential-resistance-type behavior in the  $I_d$ - $V_g$  and  $I_g$ - $V_g$  curves [14]. Here, the FeFETs with and without  $\text{HfO}_2$  IL show comparable on-state current of  $\sim 10^{-6}$  A, and the decrease in the on-state current in the FeFET without  $\text{HfO}_2$  IL could be associated with its increased surface roughness [15]. Figure 2(e) depicts the MW of the FeFETs as a function of the operating voltage, showing that the incorporation of  $\text{HfO}_2$  IL resulted in an enhanced MW and increased breakdown voltage. The improved MW is primarily attributed to the optimization of the electric-field distribution within the gate stack and the effective suppression of electron trapping through the utilization of  $\text{HfO}_2$  IL [16].

Furthermore, the cumulative programming and erasing characteristics of FeFETs with and without  $\text{HfO}_2$  IL were explored by applying  $V_g$  pulses with incremental amplitudes or widths. Following each  $V_g$  pulse,  $I_d$  was measured at a  $V_d$  of 0.1 V and a  $V_g$  of 0 V. As the program time and voltage increase, the FE domains progressively switch from the erased state to the programmed state, as shown in Figures 3(a)

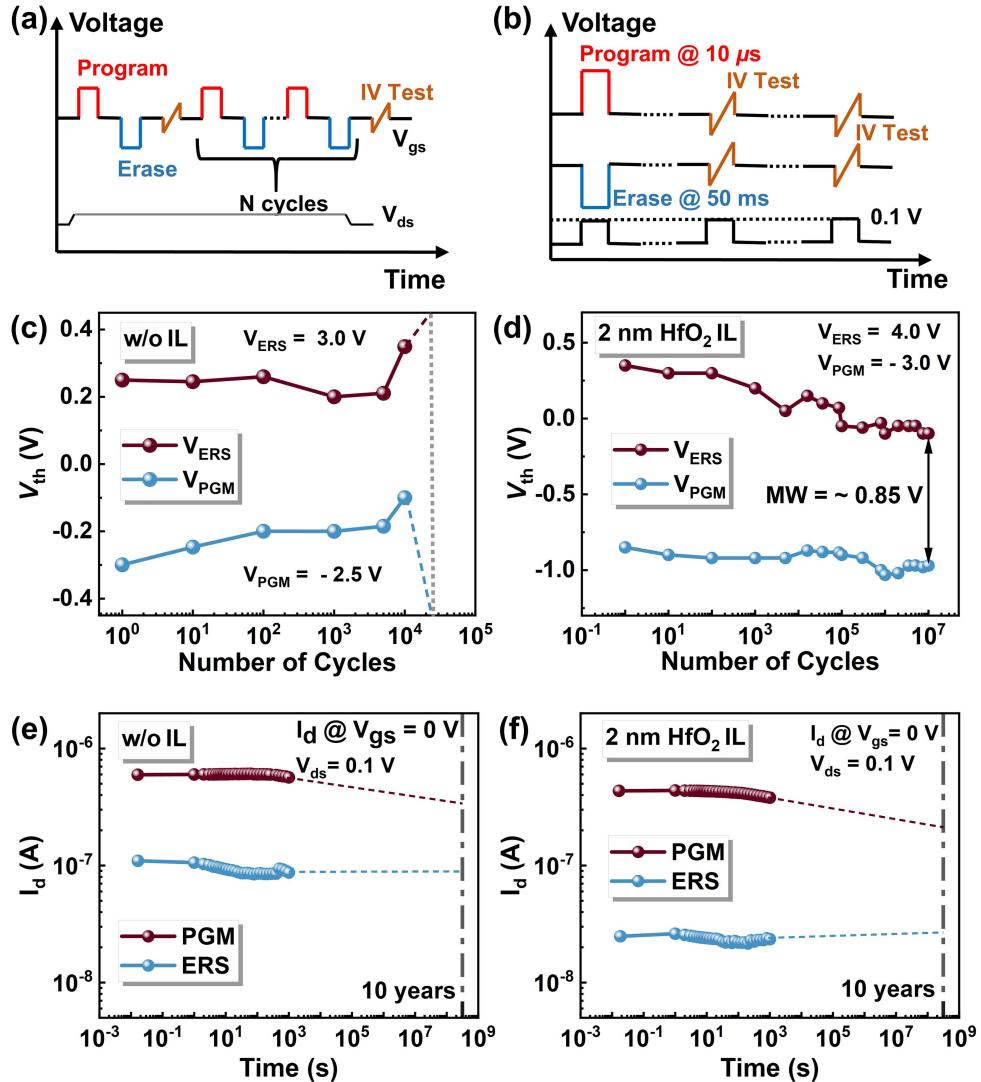

**Figure 4** (Color online) Pulse sequence for (a) endurance and (b) retention testing used. Evolution of  $V_{th}$  with program and erase cycling for the device (c) without and (d) with  $\text{HfO}_2$  IL. Retention characterization of the device (e) without and (f) with  $\text{HfO}_2$  IL.

and (b). By contrast, as the erase voltage or pulse width increases, the FE domains begin to switch from the programmed to the erased state, leading to a reduction in  $I_d$ . Compared with the FeFET without IL, the FeFET with 2 nm  $\text{HfO}_2$  IL exhibits an enhanced current MW and shorter program and erase times. Notably, the erasing speed is significantly slower than the programming speed, which is mainly related to the n-type oxide semiconductor that hardly generates holes under the external electric field. As a result, the accumulation of holes at the channel/insulator interface could not occur rapidly, directly hindering the effective electric field on the FE layer [17, 18].

To further examine the influence of  $\text{HfO}_2$  IL on the memory properties of  $\alpha\text{-IGZO}$  FeFET, the endurance and retention characteristics of FeFETs without and with  $\text{HfO}_2$  IL were measured and analyzed. The pulse sequence for reliability and retention testing used is shown in Figures 4(a) and (b), respectively. The pulse widths of the program and erase processes are 10  $\mu\text{s}$  and 50 ms to ensure complete programming and erasing. Figures 4(c) and (d) display the cycling characteristics of FeFET by loading fatigue cycles. Compared with the control device, the FeFET with  $\text{HfO}_2$  IL shows better reliability, lighter degradation of MW, and even no breakdown until an endurance of  $\sim 10^7$  cycles. The enhanced reliability is believed to be associated with the improved cycles-to-breakdown, resulting from the suppression of defect generation during cycling due to the insertion of  $\text{HfO}_2$  IL [19]. Figures 4(e) and (f) present the retention characterization of the FeFETs. Notably, the FeFETs exhibit a stable  $I_d$  after programming

and erasing, and the retention of  $>10$  years is obtained by linear extrapolation.

## 4 Conclusion

In summary, we have designed and fabricated an  $\alpha$ -IGZO FeFET with atomic-layer-deposited  $\text{HfO}_2$  IL with enhanced MW and reliability. By integrating 2 nm  $\text{HfO}_2$  IL between  $\alpha$ -IGZO and HZO dielectrics, a larger MW of  $\sim 1.1$  V is achieved compared with the FeFET without IL. Moreover, a superior MW of  $\sim 0.85$  V is still maintained after the endurance of  $\sim 10^7$  cycles, and the extrapolated retention of  $>10$  years is projected. These findings provide an alternative method to boost the MW and reliability of FeFETs via interfacial engineering.

**Acknowledgements** This work was supported by National Key Research and Development Program of China (Grant No. 2021YFB3202500) and Shanghai Municipal Science and Technology Commission (Grant Nos. 23511102300, 24DP1500105).

## References

- Chen C K, Fang Z, Hooda S, et al. First demonstration of ultra-low dit top-gated ferroelectric oxide-semiconductor memristor with record performance by channel defect self-compensation effect for BEOL-compatible non-volatile logic switch. In: Proceedings of IEEE International Electron Devices Meeting (IEDM), San Francisco, 2022. 114–117

- Lin Z, Si M, Ye P D. Ultra-fast operation of BEOL-compatible atomic-layer-deposited  $\text{In}_2\text{O}_3$  Fe-FETs: achieving memory performance enhancement with memory window of 2.5 V and high endurance  $>10^9$  cycles without  $V_T$  drift penalty. In: Proceedings of IEEE Symposium on VLSI Technology and Circuits, Hawaii, 2022. 391–392

- Dutta S, Ye H, Chakraborty W, et al. Monolithic 3D integration of high endurance multi-bit ferroelectric FET for accelerating compute-in-memory. In: Proceedings of IEEE International Electron Devices Meeting (IEDM), San Francisco, 2020. 801–804

- Schroeder U, Park M H, Mikolajick T, et al. The fundamentals and applications of ferroelectric  $\text{HfO}_2$ . *Nat Rev Mater*, 2022, 7: 653–669

- Liu F N, Peng Y, Xiao W W, et al. Impact of polarization switching on the effective carrier mobility of  $\text{HfZrO}_x$  ferroelectric field-effect transistor. *Sci China Inf Sci*, 2023, 66: 169402

- Zhang Z H, Tian G L, Huo J L, et al. Recent progress of hafnium oxide-based ferroelectric devices for advanced circuit applications. *Sci China Inf Sci*, 2023, 66: 200405

- Zhou Y, Liang Z, Luo W, et al. Ferroelectric and interlayer co-optimization with in-depth analysis for high endurance FeFET. In: Proceedings of IEEE International Electron Devices Meeting (IEDM), San Francisco, 2022. 118–121

- Kim B H, Kuk S H, Kim S K, et al. Effect of scandium insertion into the gate-stack of ferroelectric field-effect transistors. *IEEE Trans Electron Dev*, 2023, 70: 1996–2000

- Mo F, Tagawa Y, Jin C, et al. Low-voltage operating ferroelectric FET with ultrathin IGZO channel for high-density memory application. *IEEE J Electron Dev Soc*, 2020, 8: 717–723

- Li Y C, Li X X, Huang T, et al. Enhanced memory properties of  $\text{HfO}_2$ -based ferroelectric capacitor by inserting  $\text{Al}_2\text{O}_3/\text{ZrO}_2$  stack interfacial layer. *Appl Phys Lett*, 2023, 122: 172902

- Liang Z, Tang K, Dong J, et al. A novel high-endurance FeFET memory device based on  $\text{ZrO}_2$  anti-ferroelectric and IGZO channel. In: Proceedings of IEEE International Electron Devices Meeting (IEDM), San Francisco, 2021. 118–121

- Cao R, Wang Y, Zhao S, et al. Effects of capping electrode on ferroelectric properties of  $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$  thin films. *IEEE Electron Dev Lett*, 2018, 39: 1207–1210

- Si M, Ye P D. The critical role of charge balance on the memory characteristics of ferroelectric field-effect transistors. *IEEE Trans Electron Dev*, 2021, 68: 5108–5113

- Wang Y, Tao L, Guzman R, et al. A stable rhombohedral phase in ferroelectric  $\text{Hf}(\text{Zr})_{1+x}\text{O}_2$  capacitor with ultralow coercive field. *Science*, 2023, 381: 558–563

- Cui T, Chen D, Dong Y, et al. Can interface layer be really free for  $\text{Hf}_x\text{Zr}_{1-x}\text{O}_2$  based ferroelectric field-effect transistors with oxide semiconductor channel? *IEEE Electron Dev Lett*, 2024, 45: 368–371

- Ni K, Sharma P, Zhang J, et al. Critical role of interlayer in  $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$  ferroelectric FET nonvolatile memory performance. *IEEE Trans Electron Dev*, 2018, 65: 2461–2469

- Meng W, Xiao D Q, Luo B B, et al. Performance improvement of  $\text{Hf}_{0.45}\text{Zr}_{0.55}\text{O}_x$  ferroelectric field effect transistor memory with ultrathin Al-O bonds-modified  $\text{InO}_x$  channels. *Nanotechnology*, 2023, 34: 175204

- Lin Z, Si M, Luo Y C, et al. High-performance BEOL-compatible atomic-layer-deposited  $\text{In}_2\text{O}_3$  Fe-FETs enabled by channel length scaling down to 7 nm: achieving performance enhancement with large memory window of 2.2 V, long retention  $>10$  years and high endurance  $>10^8$  cycles. In: Proceedings of IEEE International Electron Devices Meeting (IEDM), San Francisco, 2021. 386–389

- Toprasertpong K, Takenaka M, Takagi S. Breakdown-limited endurance in HZO FeFETs: Mechanism and improvement under bipolar stress. *Front Electron*, 2022, 3: 1–11